# SOLUTION 11

## Exercise 1: AMOLED Pixel Driver Circuits

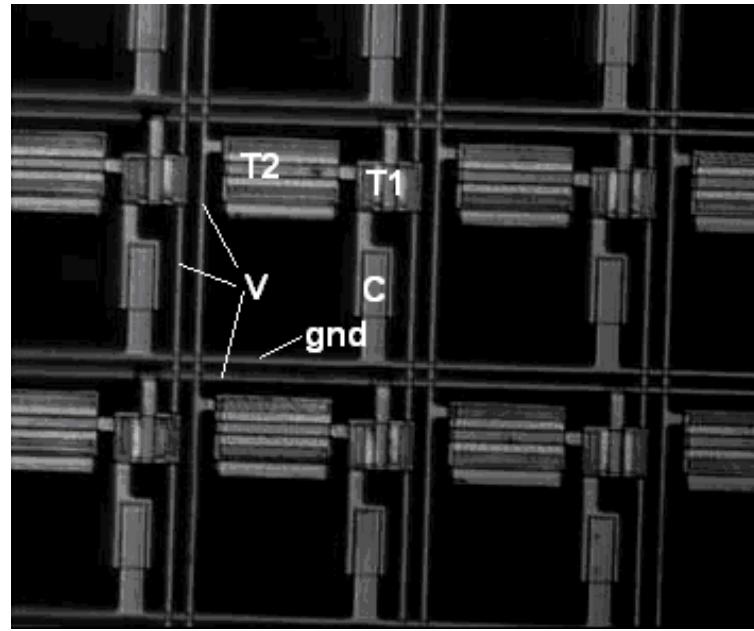

a)  $T_2$  is easily identifiable as most of the current is passing through it, it is also the biggest structure.

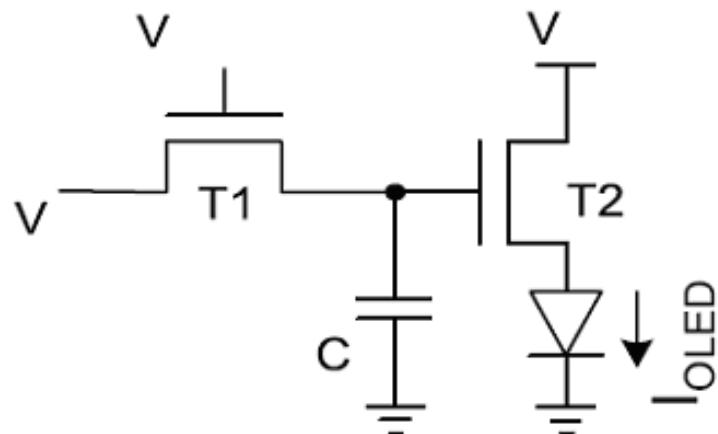

Figure 1: 2-transistors circuit.

From the above circuit, the solution is then given in the following figure. The OLED is the whole black surface, connected via  $T_2$ .

Figure 2: AMOLED pixel circuit.

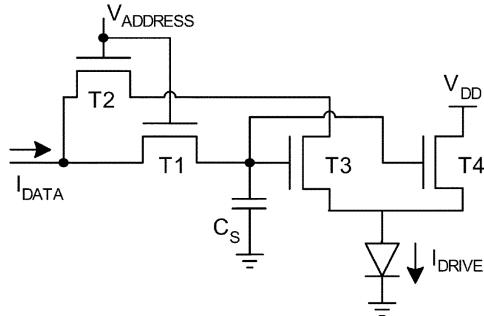

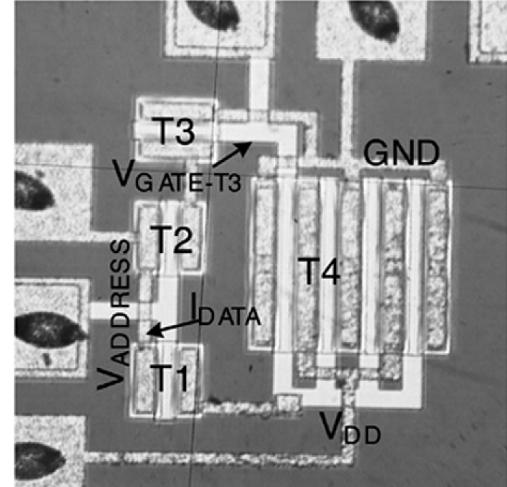

b) The solution is given by:

(a)

(b)

Figure 3: More details can be found in: K. Sakariya et al., IEEE Transactions on electron devices, Vol. 51 (12), Dec. 2004.

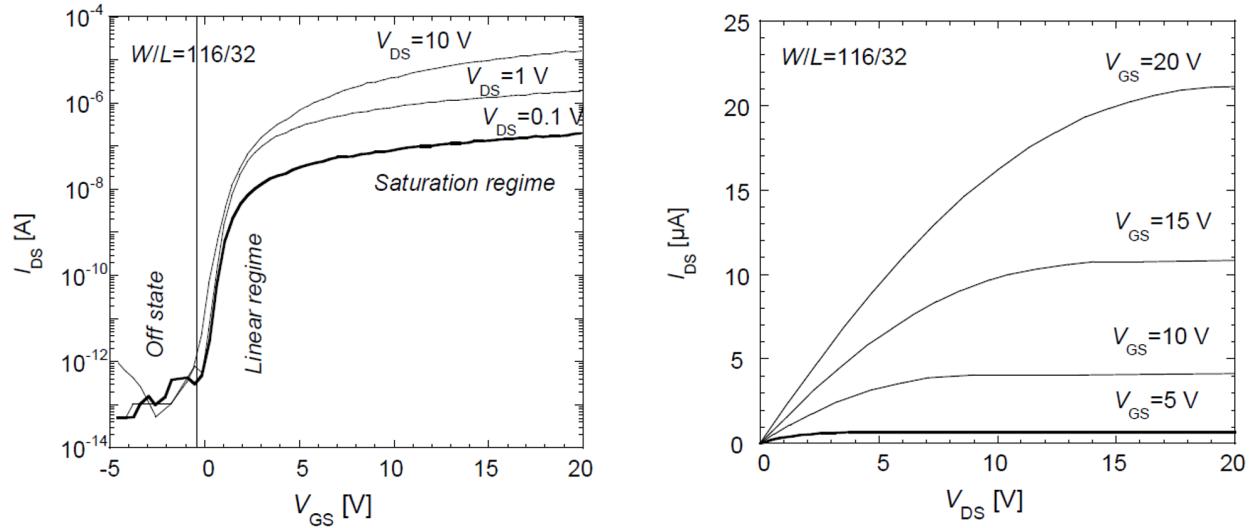

**Exercise 2:** Given are the following a-Si:H TFT characteristics:

a) In p-Thin-film transistors and flat panel displays, slide 36, the following for-

mula is given for the estimation of the field effect mobility:

$$\mu_n^{\text{FET}} \left[ \frac{\text{cm}^2}{\text{V s}} \right] = \frac{\partial I_{\text{ds}}}{\partial V_{\text{G}}} \cdot \frac{L}{W \cdot C'_{\text{SiN}_x} \cdot V_{\text{ds}}}, \quad (1)$$

which is valid in the linear regime. Here  $C'_{\text{SiN}_x}$  denotes a surface normalized capacitance, otherwise above equation would not be correct. Every information can be extracted from the upper left figure (also given in **p-Thin-film transistors and flat panel displays**, slide 34), except the capacitance due to the insulating layer, which will be approximated with a parallel plate capacitor, given by

$$\frac{C}{A} = \frac{\epsilon_0 \epsilon_r}{d} \cong 2.66 \times 10^{-8} \text{ F cm}^{-2}, \quad (2)$$

where  $d$  is typically 250 nm (**p-Thin-film transistors and flat panel displays**, slide 27),  $\epsilon_0 = 8.85 \times 10^{-14} \text{ F cm}^{-1}$  and  $\epsilon_r = 7.5$ .

By using values in the linear range (approximatively between 2 V and 4 V, be careful of the logarithmic scale!)

$$\frac{\partial I_{\text{ds}}}{\partial V_{\text{G}}} \cong \frac{3 \times 10^{-7} \text{ A} - 2 \times 10^{-8} \text{ A}}{4 \text{ V} - 2 \text{ V}} \cong 1.4 \times 10^{-7} \text{ A V}^{-1} \quad (3)$$

for  $V_{\text{ds}} = 10 \text{ V}$ ,  $W = 116 \mu\text{m}$  and  $L = 32 \mu\text{m}$ , we obtain  $\mu_n^{\text{FET}} \cong 0.15 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , which is in the same order as the values given in **p-Thin-film transistors and flat panel displays**, slide 26.

b) By assuming a uniform distribution along the channel of the effective mobility and using the first equation on slide 29, the ratio of free to trapped charge is given by

$$\frac{\mu_n^0}{\mu_n^{\text{FET}}} = \frac{n_f + n_t}{n_f} \quad (4)$$

with  $\mu_n^0 \cong 10 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , leading to

$$\frac{n_t}{n_f} \cong \frac{10}{0.15} - 1 \cong 66. \quad (5)$$

c) In the case of an illuminated layer of a-Si:H (so no field effect in that case), this ratio is very approximately given by the ratio of the drift mobility to the band mobility (see e.g. the lecture on band tails in a-Si:H, `e-conductivity_band-tails, slide 11`), that is

$$\frac{\mu_n^{\text{drift}}}{\mu_n^0} = \frac{n_f}{n_f + n_t}, \quad (6)$$

leading to

$$\frac{n_t}{n_f} = \frac{\mu_n^0}{\mu_n^{\text{drift}}} - 1 \cong \frac{10 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}}{1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}} - 1 \cong 9. \quad (7)$$

Both values were expected to be approximately the same: in both cases there is a thermodynamical equilibrium between trapped and free states (above the Quasi-Fermi level and within the band tails). Our estimation for the FET mobility is a bit too high but with the given graphs, it is quite difficult to make an exact estimation.