## EE-523 – Exercise 1

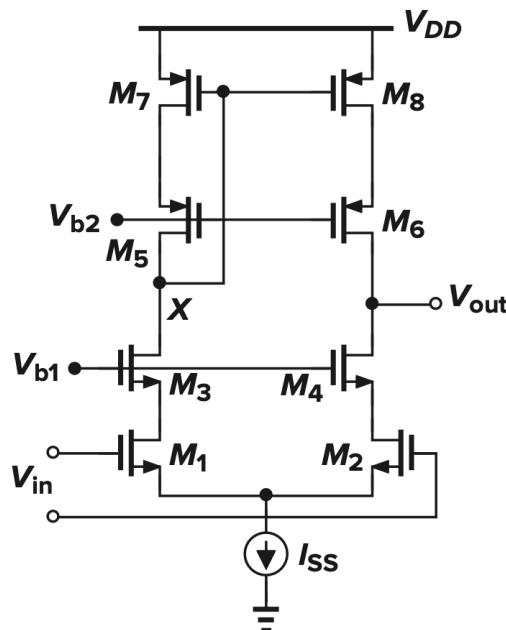

1. In the op amp shown below,  $(W/L_{\text{eff}})_{1-8} = 100/0.34$ ,  $I_{\text{SS}} = 1\text{mA}$ ,  $V_{b1} = 1.7\text{V}$ . Assume  $\gamma=0$ ,  $V_{\text{TH,P}} = 0.8\text{V}$ ,  $V_{\text{TH,N}} = 0.7\text{V}$ ,  $\mu_n C_{\text{ox}} = 0.134 \text{ mA/V}^2$ ,  $\mu_p C_{\text{ox}} = 0.038 \text{ mA/V}^2$ ,  $\lambda=0$ , and  $V_{\text{DD}} = 3\text{V}$ .

- (a) What is the maximum allowable input CM level?

- (b) What is the value of  $V_X$  (voltage at node X)?

- (c) What is the maximum allowable output swing if the gate of  $M_2$  is connected to output?

- (d) What is the acceptable range of  $V_{b2}$ ?

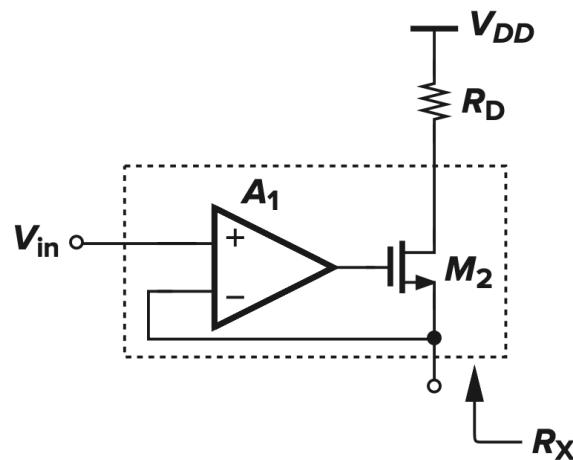

2. Determine the resistance seen at the source of  $M_2$  if  $\gamma = 0$ .

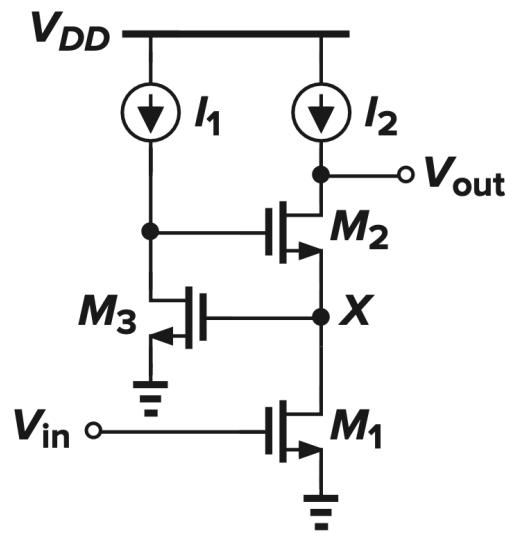

3. Suppose that in the circuit below,  $I_1 = 100\mu\text{A}$ ,  $I_2 = 0.5\text{mA}$ , and  $(W/L_{\text{eff}})_{1-3} = 100/0.34$ ,  $V_{\text{TH,N}} = 0.7\text{V}$ ,  $\mu_n C_{\text{ox}} = 0.134 \text{ mA/V}^2$ ,  $\mu_p C_{\text{ox}} = 0.038 \text{ mA/V}^2$ ,  $\lambda=0$ . Assuming that  $I_1$  and  $I_2$  are implemented with PMOS devices having  $(W/L_{\text{eff}})_P = 50/0.32$

- (a) Calculate the gate bias voltages of  $M_2$  and  $M_3$ .

- (b) Determine the maximum allowable output voltage swing.

- (c) Calculate the overall voltage gain, assuming  $\lambda=0.2$ .