# EE-465 - W5 3-PHASE VSI CARRIER BASED PWM

**Prof. D. Dujic**

École Polytechnique Fédérale de Lausanne

Power Electronics Laboratory

Switzerland

**EPFL**

**pel**

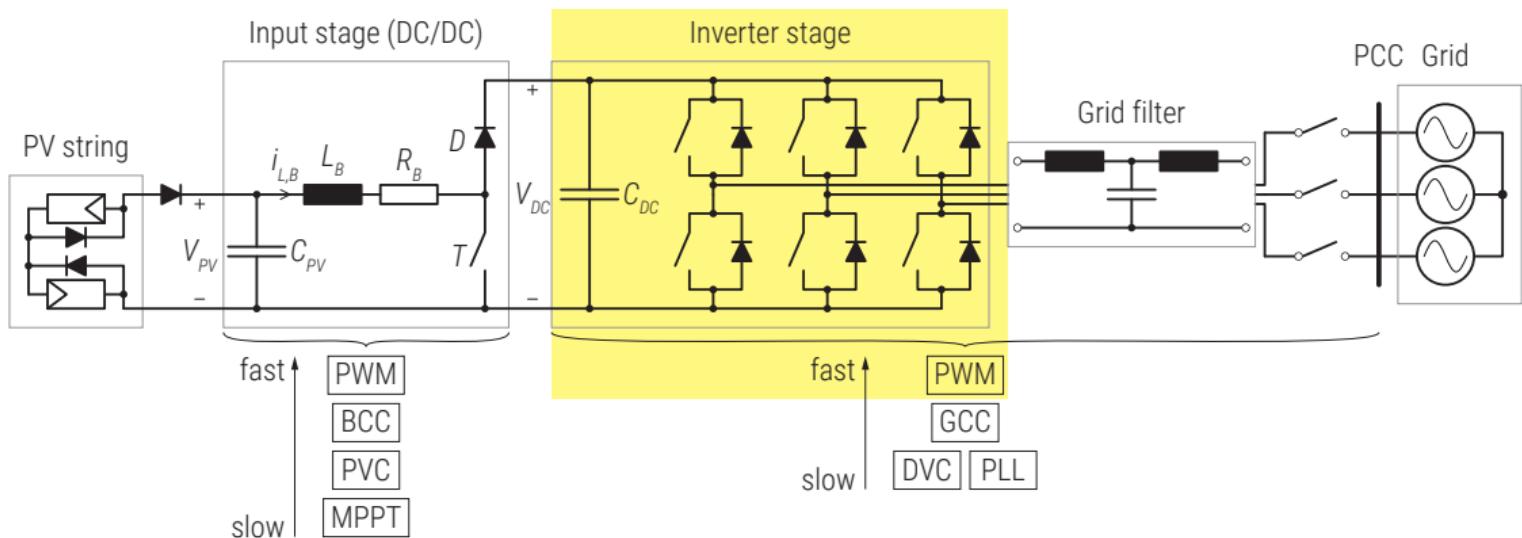

# EE-465 INVERTER STAGE

We will look into:

- ▶ 2L VSI operating principles

- ▶ Carrier-based PWM

- ▶ Zero-sequence injection principles

- ▶ Other multilevel topologies

Figure 1 PV double-stage grid connected converter.

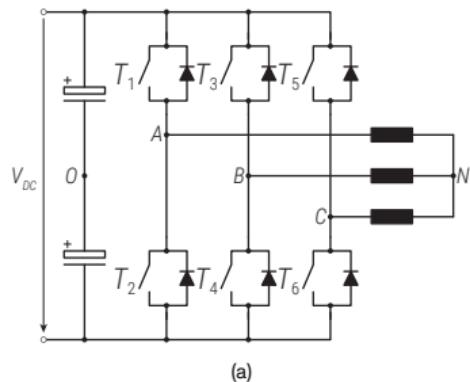

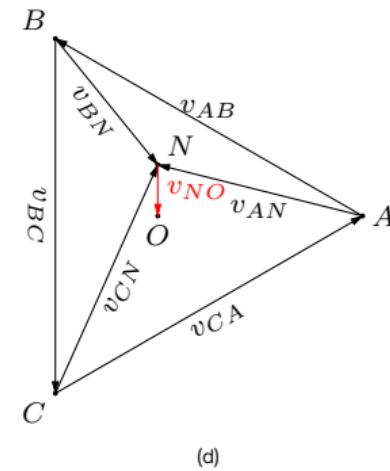

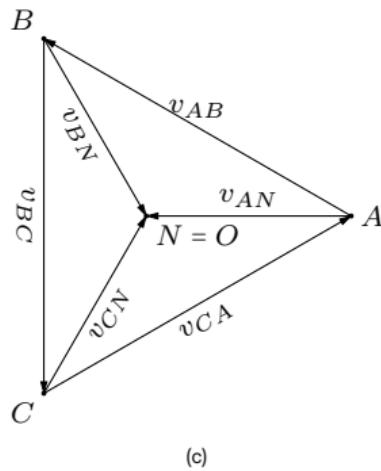

# 3-PHASE 2-L INVERTER

- ▶ Obtained by combining  $3 \times 2\text{-L}$  phase-legs

- ▶  $N$  and  $O$  are not connected together! - but can be used as references for various calculations

- ▶ 3-phase load can be brought in only a limited number of configurations

- ▶ 3-phase 2-level inverter has only 8 switching states (configurations)

(a)

Figure 2 (a) 2L three-phase inverter scheme and (b)  $2^3 = 8$  switch combinations.

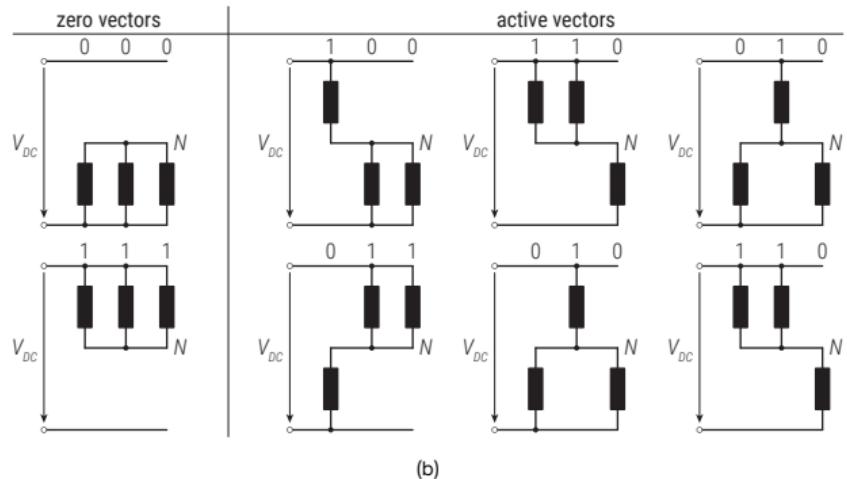

# 3-PHASE 2-L INVERTER

Table 1 Instantaneous phase to neutral and common mode voltages for all 8 space vectors, assuming identical phase impedances  $Z$ .

|                | $s_A$ | $s_B$ | $s_C$ | $v_{AN}$     | $v_{BN}$     | $v_{CN}$     | $v_{NO}$    |

|----------------|-------|-------|-------|--------------|--------------|--------------|-------------|

| $\mathbf{V}_0$ | 0     | 0     | 0     | 0            | 0            | 0            | $-V_{DC}/2$ |

| $\mathbf{V}_1$ | 1     | 0     | 0     | $2V_{DC}/3$  | $-V_{DC}/3$  | $-V_{DC}/3$  | $-V_{DC}/6$ |

| $\mathbf{V}_2$ | 1     | 1     | 0     | $V_{DC}/3$   | $V_{DC}/3$   | $-2V_{DC}/3$ | $V_{DC}/6$  |

| $\mathbf{V}_3$ | 0     | 1     | 0     | $-V_{DC}/3$  | $2V_{DC}/3$  | $-V_{DC}/3$  | $-V_{DC}/6$ |

| $\mathbf{V}_4$ | 0     | 1     | 1     | $-2V_{DC}/3$ | $V_{DC}/3$   | $V_{DC}/3$   | $V_{DC}/6$  |

| $\mathbf{V}_5$ | 0     | 0     | 1     | $-V_{DC}/3$  | $-V_{DC}/3$  | $2V_{DC}/3$  | $-V_{DC}/6$ |

| $\mathbf{V}_6$ | 1     | 0     | 1     | $V_{DC}/3$   | $-2V_{DC}/3$ | $V_{DC}/3$   | $V_{DC}/6$  |

| $\mathbf{V}_7$ | 1     | 1     | 1     | 0            | 0            | 0            | $V_{DC}/2$  |

Figure 3 Voltage synthesis capability for a 2-L 3-ph inverter.

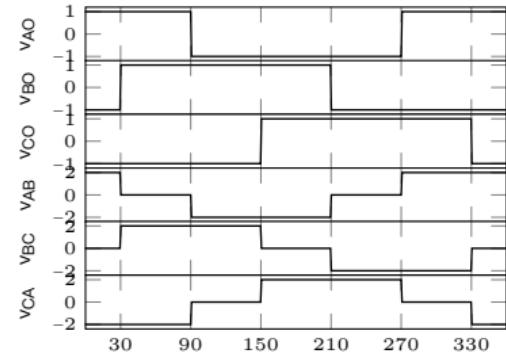

# SQUARE-WAVE (SIX-STEP) OPERATION FOR 2-L INVERTERS

- ▶ Leg voltage is a simple square-wave type - contains all odd harmonics

- ▶ Only the active vectors are used (6 out of 8)

- ▶ Each leg is driven by  $180^\circ$  pulse,  $120^\circ$  delay between the phase-legs

- ▶ It is described by a geometric progression. In phase  $a$ , the voltage with respect to the negative bus terminal is:

$$v_A(t) = V_{DC} \frac{2}{\pi} \left( \frac{\pi}{4} + \frac{1}{3} \sin(3\omega_0 t) + \frac{1}{5} \sin(5\omega_0 t) + \dots \right)$$

- ▶ The magnitudes of the harmonics are  $\|v[k]\|_{\text{phase}} = V_{DC} \frac{2}{\pi} \frac{1}{k}, k \in \{1, 3, 5, \dots\}$

- ▶ Line-to-line voltage can be determined by subtracting phase voltages, leading to cancellation of triplen harmonics:  $v_{AB}(t) = V_{DC} \frac{2\sqrt{3}}{\pi} \left( \sin(\omega_0 t + \pi/6) + \frac{1}{5} \sin(5\omega_0 t - \pi/6) + \frac{1}{7} \sin(7\omega_0 t + \pi/6) + \dots \right)$

- ▶ The magnitudes of the harmonics are  $\|v[k]\|_{\text{line}} = V_{DC} \frac{2\sqrt{3}}{\pi} \frac{1}{k}, k \in \{1, 5, 7, \dots\}$

- ▶ Inverter does frequency control / voltage control through external DC link control

- ▶  $M = 4/\pi \approx 1.27$

(a)

(b)

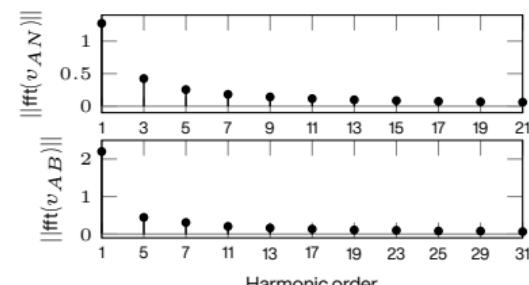

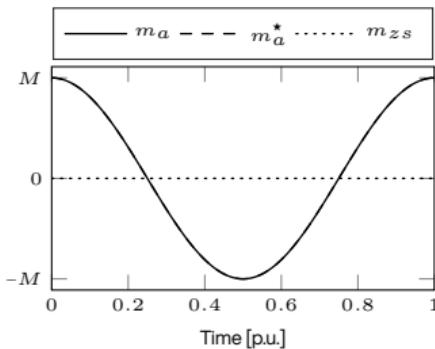

# SINUSOIDAL PWM - SPWM

- ▶ Normally, we want sinusoidal line-to-line voltages

- ▶ Fundamental three-phase reference signals:

$$\begin{cases} v_a^* = V_m \cos(\omega t) \\ v_b^* = V_m \cos(\omega t - 2\pi/3) \\ v_c^* = V_m \cos(\omega t + 2\pi/3) \end{cases}$$

- ▶ The modulation index is defined as  $M = \frac{V_m}{V_{DC}/2}$

- ▶ It relates the output peak phase voltage and  $V_{DC}$

- ▶ Reference normalization:

$$\begin{cases} m_a^* = M \cos(\omega t) \\ m_b^* = M \cos(\omega t - 2\pi/3) \\ m_c^* = M \cos(\omega t + 2\pi/3) \end{cases}$$

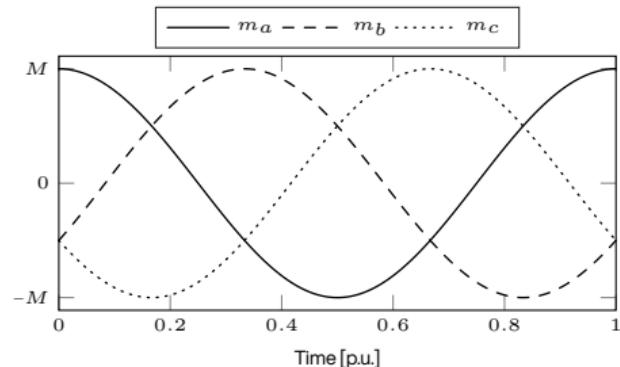

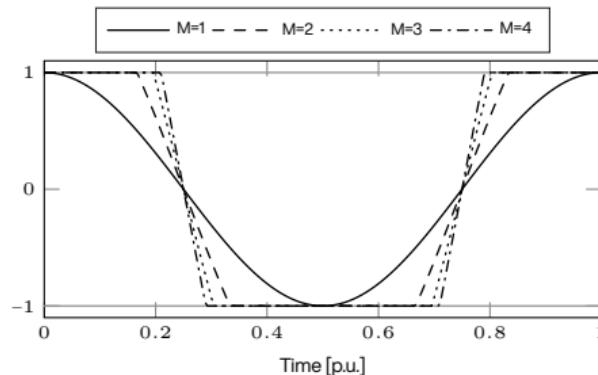

# OVERMODULATION

- ▶ Normally, we have carrier bounded to  $\pm 1$  range

- ▶ SPWM is bounded by  $M_{\max} = 1$ , else low-order harmonics appear

- ▶ Non-triplet harmonics are difficult to filter out (low filter cut-off frequency required, means large filters!)

- ▶ In the worst case, it becomes six-step (square-wave) modulation

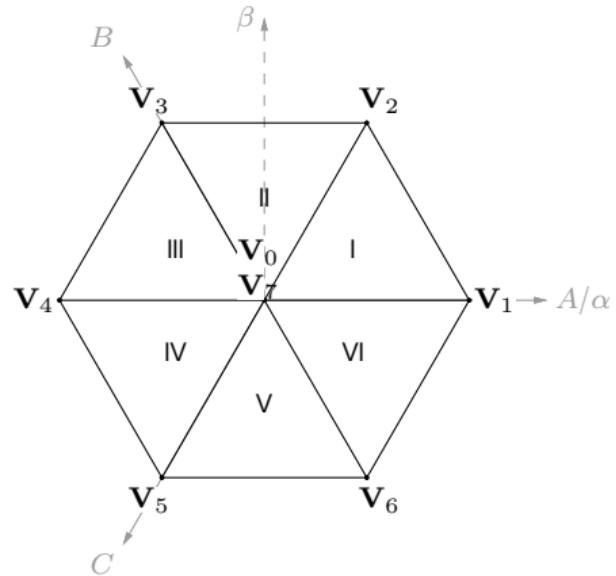

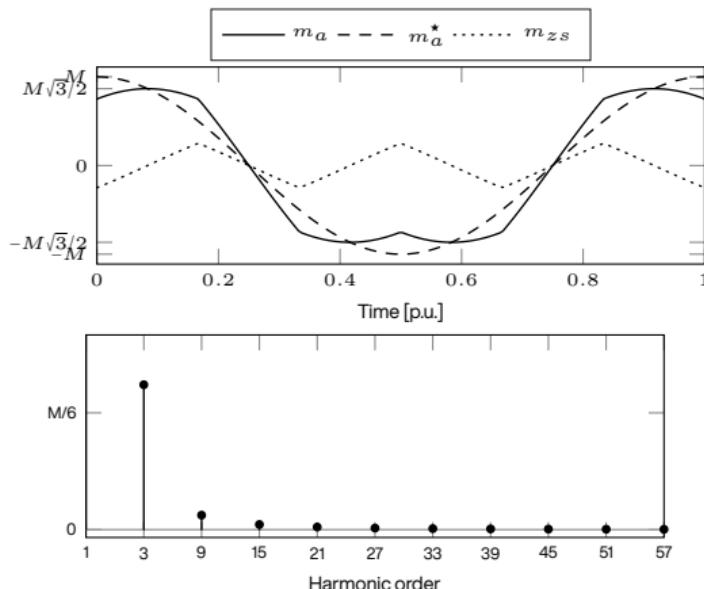

# ZERO-SEQUENCE INJECTION

- ▶ From power systems theory for three-phase system (if  $\omega = \text{cst}$ ): there exists a linear decomposition into positive, negative and zero sequence of balanced (with same amplitude) symmetrical components (with  $\pm 120^\circ$  shift)

- ▶ In star-connected systems, no zero-sequence current can flow  $\rightarrow$  degree of freedom to be used for extending the DC bus utilization, i.e. allow  $M_{\max} > 1$

- ▶ Zero-sequence component is obtained as:  $m_{zs} = (m_a + m_b + m_c)/3$

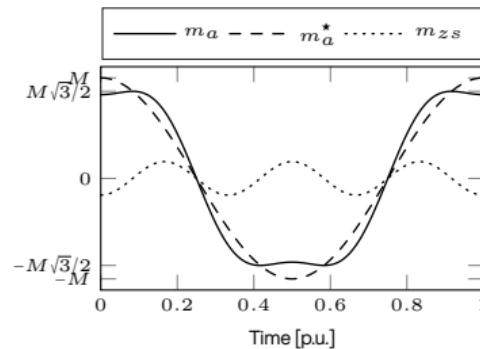

Figure 4 (a) no zero-sequence signal and (b) zero sequence signal, with line-to-line voltage preservation.

# ZERO SEQUENCE SIGNAL INJECTION

- The zero-sequence injection is defined as:

$$\begin{cases} m_a = M \cos(\omega t) + m_{zs} \\ m_b = M \cos(\omega t - 2\pi/3) + m_{zs} \\ m_c = M \cos(\omega t + 2\pi/3) + m_{zs} \end{cases}$$

- The harmonic distortion will be reduced, as no low-order non triplen harmonics are injected, contrary to the six-step modulation

- The zero-sequence signal doesn't appear in the line-to-line voltages as the triplen harmonics cancel each other:  $v_{AB} = v_{AN} - v_{BN}$

- No zero-sequence current will flow in star-connected loads

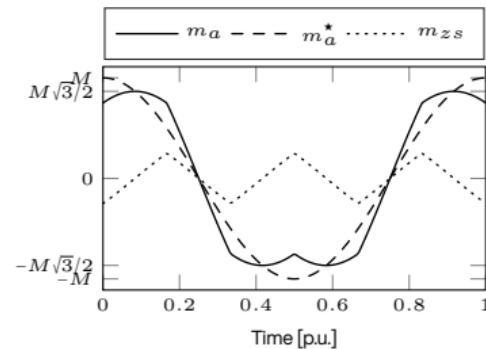

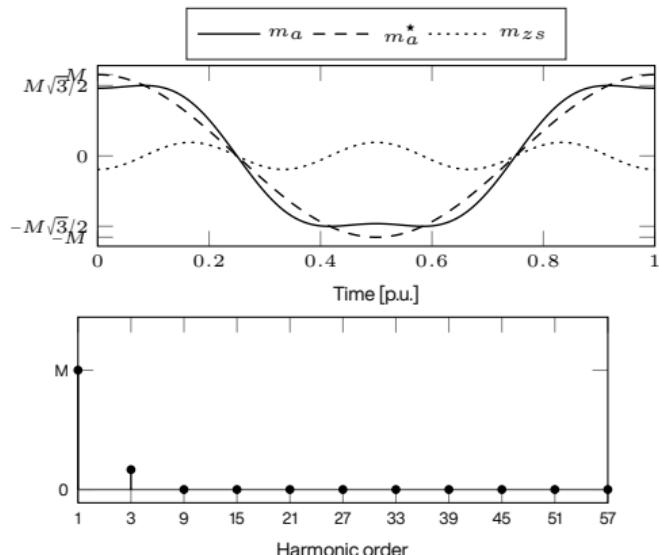

(a)

(b)

(c)

Figure 5 Zero-sequence injection methods illustration: (a) sinusoidal PWM, (b) third harmonic injection and (c) min/max injection.

# THIRD HARMONIC INJECTION

- ▶ The third harmonic is the lowest triplen harmonic. It might very likely have the largest impact.

- ▶ Let  $b$  the relative amount of third harmonic that we want to add to the fundamental

- ▶ Taking phase  $a$  as example:

$$m_a^* = M \cos(\omega t) + bM \cos(3\omega t)$$

- ▶ Extreme of the function is found by equalizing the derivative to 0:

$$\frac{dm_a}{dt} = -M\omega \sin(\omega t) - b3M\omega \sin(3\omega t) = 0$$

$$b = -\frac{\sin(\omega t)}{3 \sin(3\omega t)}$$

- ▶ The peak of the modulating signal is found at  $\omega t = \pi/6$

- ▶ Result:  $b = -\frac{\sin(\pi/6)}{3 \sin(3\pi/6)} = -\frac{\sin(\pi/6)}{3} = -1/6$

- ▶ At peak value:

$$M_{\max} \cos(\omega t) + bM_{\max} \cos(3\omega t) = 1 \rightarrow M_{\max} = \frac{1}{\cos(\pi/6)}$$

- ▶ The increase is around 15 %:  $M_{\max} = \frac{1}{\cos(\pi/6)} = \frac{2}{\sqrt{3}} \approx 1.15$

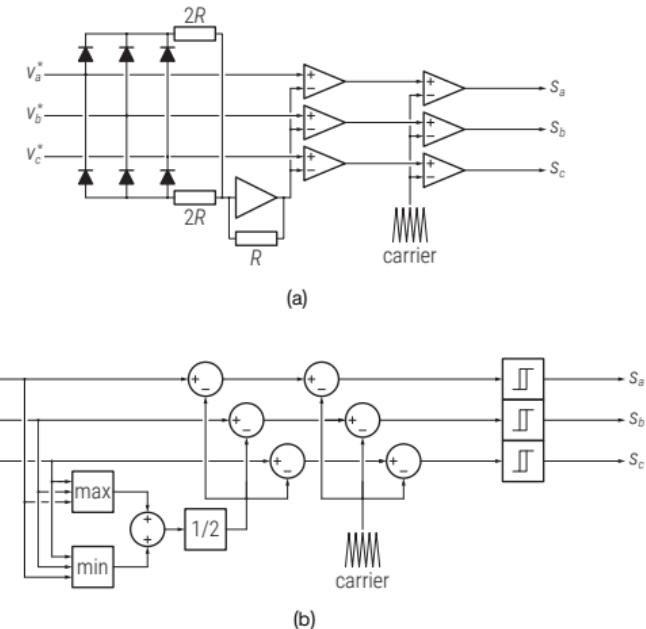

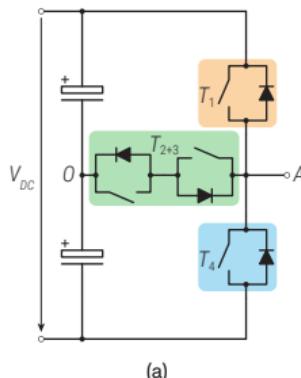

# MIN/MAX SIGNAL INJECTION

- ▶ It is not convenient to inject a third harmonic, as the magnitude and frequency of the reference signal cannot be directly determined from the instantaneous sampled modulation index references

- ▶ The harmonic content is an infinite sum of odd triplen harmonics!

Figure 6 Min/max zero-sequence injection: (a) analog scheme and (b) digital PWM.

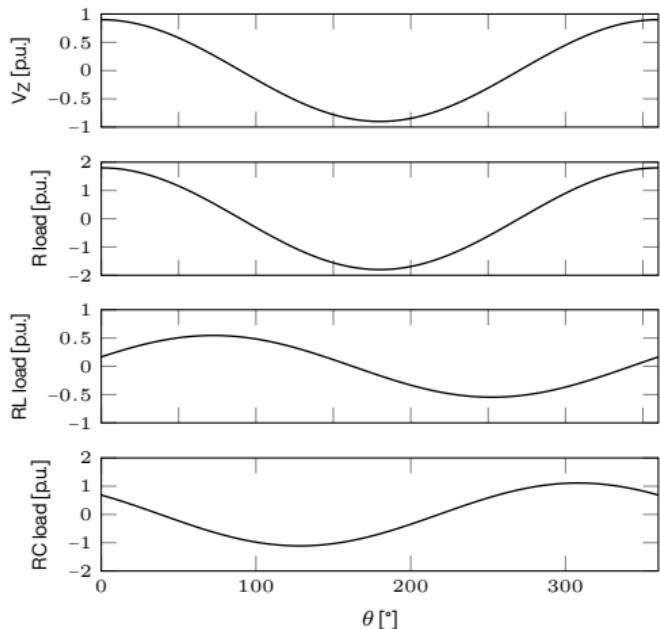

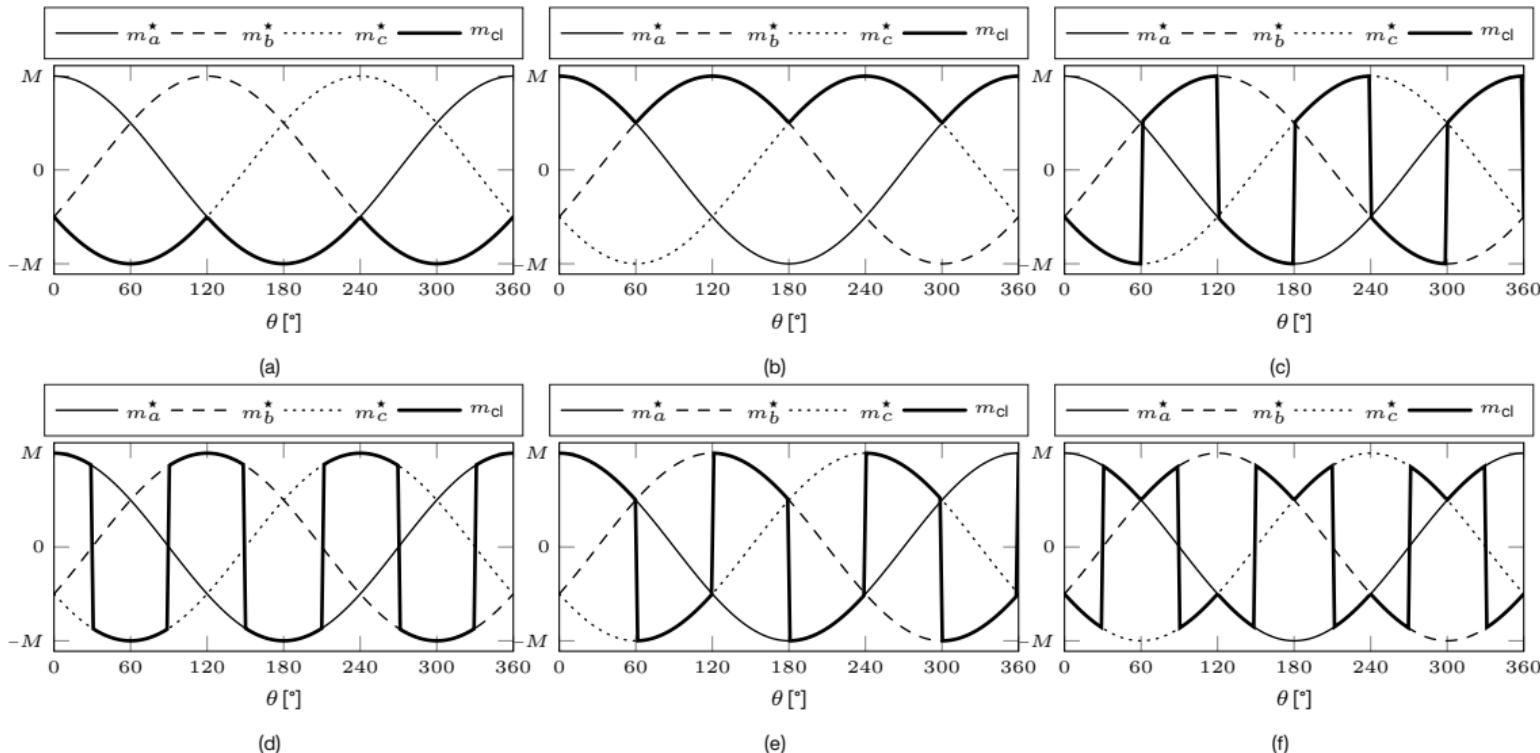

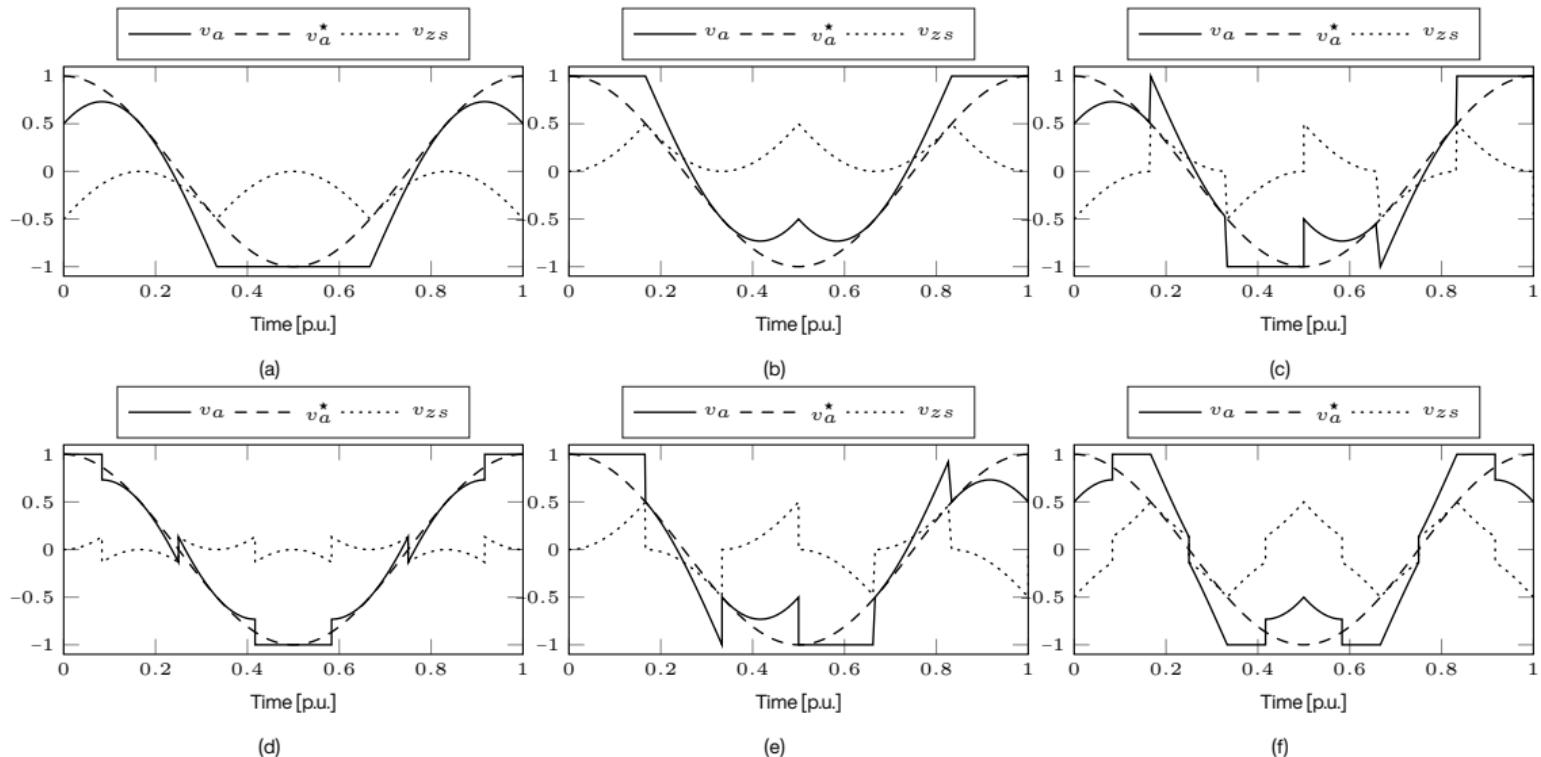

# DISCONTINUOUS PWM - DPWM

- ▶ Depending on the load type (resistive, inductive, capacitive), switching losses ( $\sim v \cdot i$ ) are high when the load current is large

- ▶ Discontinuous PWM avoids switching for a certain time in a period ( $2 \times 60^\circ$ )

- ▶ That region has to be adapted depending on the load type

- ▶  $M_{\max} = 2/\sqrt{3}$

- ▶ Not switching = clamping one phase voltage to  $V_{DC}$  or 0

Figure 7 Load types: resistive (current in phase), inductive (current lagging) and capacitive (current leading).

# DISCONTINUOUS PWM - DPWM

Figure 8 Discontinuous PWM clamping regions: (a) DPWMMIN, (b) DPWMMAX, (c) DPWMO, (d) DPWM1, (e) DPWM2 and (f) DPWM3.

# DISCONTINUOUS PWM - DPWM

Figure 9 Discontinuous PWM,  $M = 1$ : (a) DPWMMIN, (b) DPWMMAX, (c) DPWM0, (d) DPWM1, (e) DPWM2 and (f) DPWM3.

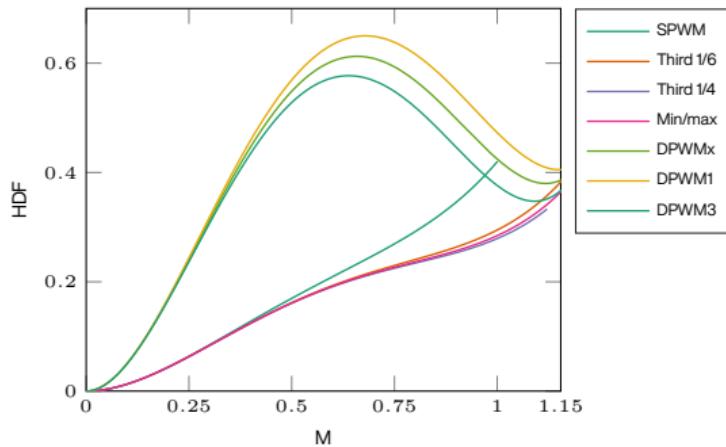

# HARMONIC DISTORTION FACTOR - HDF

- ▶ Figure of merit for harmonic losses caused by switching harmonics

- ▶ DPWM schemes allow for effective increase of switching frequency of 1.5 times of CPWM

- ▶ Switching losses of CPWM and DPWM can be maintained at the same level

(a)

(b)

Figure 10 HDF plot for: (a)  $f_{sw,CPPWM} = f_{sw,DPWM}$  and (b)  $f_{sw,CPPWM} = 2f_{sw,DPWM}/3$ .

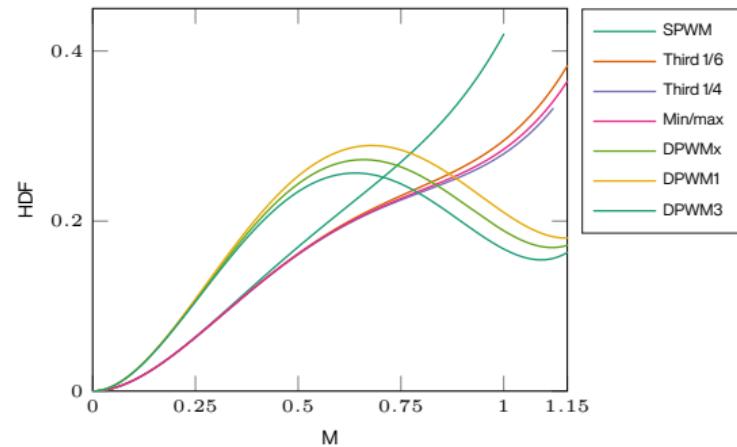

# EFFECTIVE MODULATION INDEX

- ▶ In overmodulation region ( $M > 1$  for SPWM or  $M > 2/\sqrt{3}$  for zero-sequence injection methods), the real modulation index (i.e. fundamental term of the Fourier series) is not anymore given by a linear expression

- ▶ The effective modulation index saturation at  $4/\pi$  (six-step modulation)

Figure 11 Effective modulation index in linear and overmodulation regions.

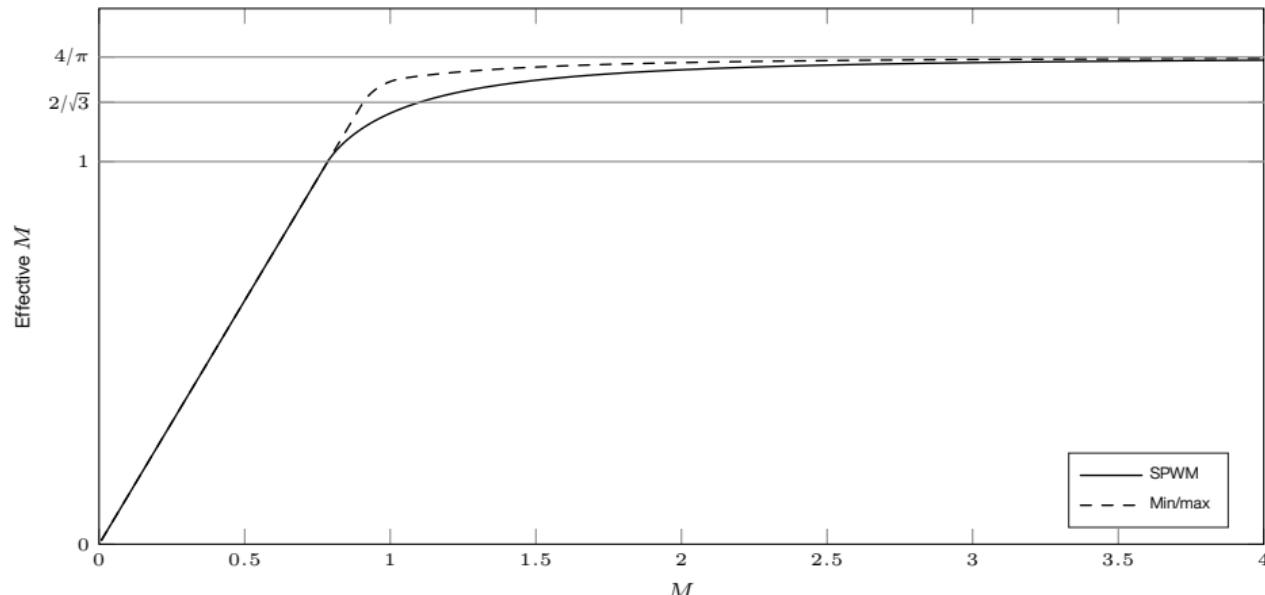

# MULTILEVEL CONVERTERS

- Advantages

- Higher DC link voltage accessible with same semiconductor technology

- Improved resolution/quality of the output voltage with lower  $f_{sw}$

- Drawbacks

- Higher complexity in the modulator

- Device failure

- Examples of three-level topologies

- 3L Neutral Point Piloted (Holtz 1977)

- 3L Neutral Point Clamped (Nabae 1981)

- 3L Flying Capacitor (Meynard 1992)

- Can be extended to  $> 3\text{-L}$

- Intermediate voltage levels must be kept balanced

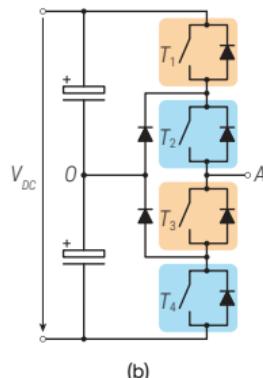

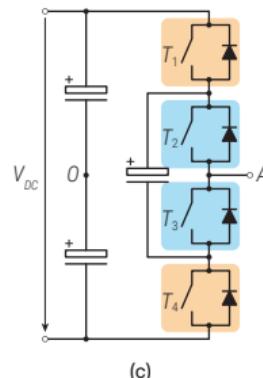

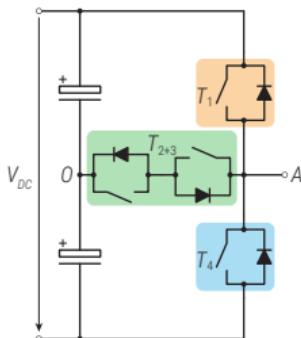

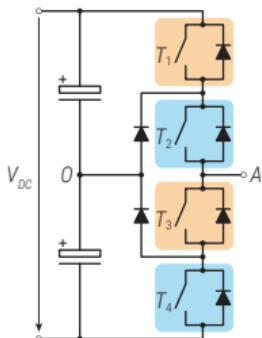

(a)

(b)

(c)

Figure 12 Multilevel phase-legs: (a) 3L NPP, (b) 3L NPC and (c) 3L FC.

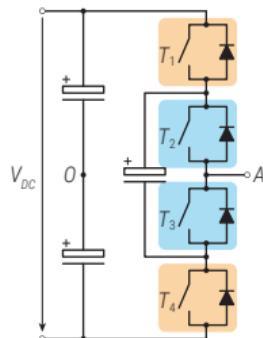

# MULTILEVEL CONVERTERS

3-L NPP

| $s_1$ | $s_4$ | $v_{AO}$    |

|-------|-------|-------------|

| 0     | 1     | $-V_{DC}/2$ |

| 1     | 0     | 0           |

| 0     | 1     | 0           |

| 1     | 0     | $V_{DC}/2$  |

► Switching logic

$$\triangleright s_{2+3} = \text{and}(\bar{s}_1, \bar{s}_4)$$

► Can operate as 2L

3-L NPC

| $s_1$ | $s_2$ | $v_{AO}$    |

|-------|-------|-------------|

| 0     | 0     | $-V_{DC}/2$ |

| 1     | 0     | 0           |

| 0     | 1     | 0           |

| 1     | 1     | $V_{DC}/2$  |

► Switching logic

$$\begin{aligned} \triangleright s_3 &= \bar{s}_1 \\ \triangleright s_4 &= \bar{s}_2 \end{aligned}$$

3-L FC

| $s_1$ | $s_2$ | $v_{AO}$    |

|-------|-------|-------------|

| 0     | 0     | $-V_{DC}/2$ |

| 1     | 0     | 0           |

| 0     | 1     | 0           |

| 1     | 1     | $V_{DC}/2$  |

► Switching logic

$$\begin{aligned} \triangleright s_3 &= \bar{s}_2 \\ \triangleright s_4 &= \bar{s}_1 \end{aligned}$$

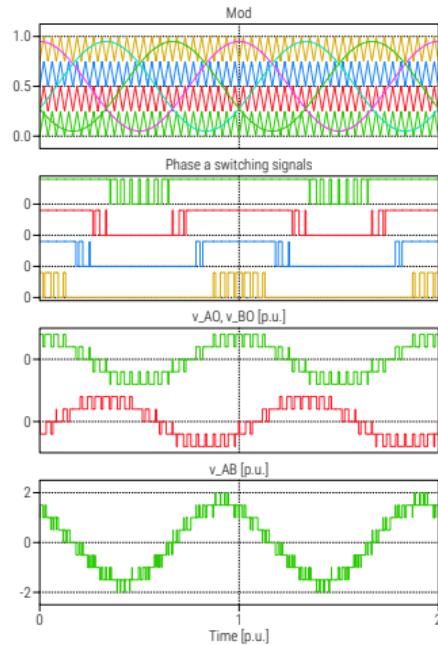

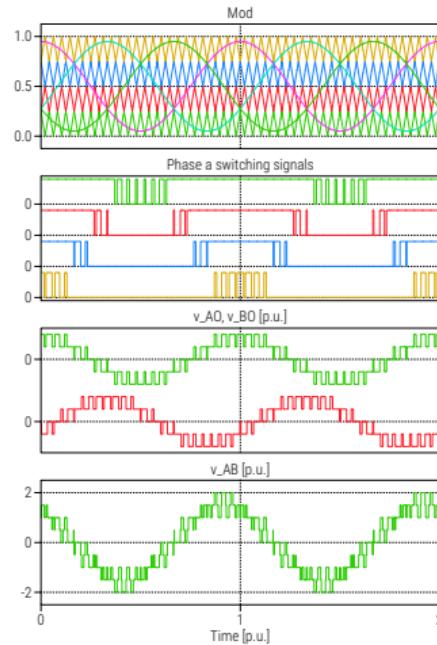

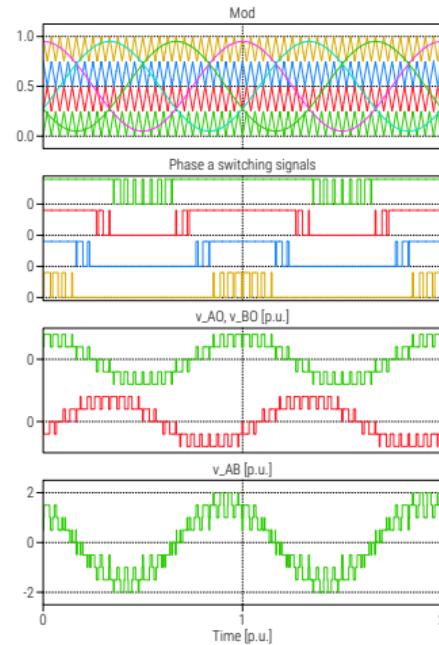

# MULTILEVEL MODULATION METHODS

- One carrier assigned per pair of complementary switches

(a)

(b)

(c)

Figure 13 Multilevel PWM methods illustrated for the 5L case for  $f_{sw} = 24 f_g$ : (a) PD-PWM → all carriers in phase, (b) APOD-PWM → 180° shift between carrier bands and (c) POD-PWM → 180° shift between the carrier above and below 0.5.

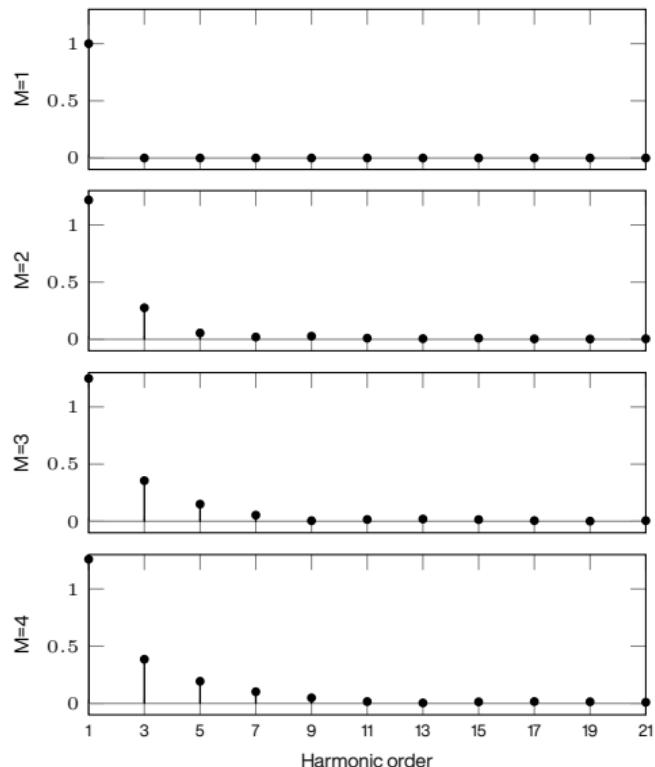

# 3-L INVERTER WAVEFORMS

- PD-PWM is the best multilevel PWM method (cf. line-to-line voltage waveforms)

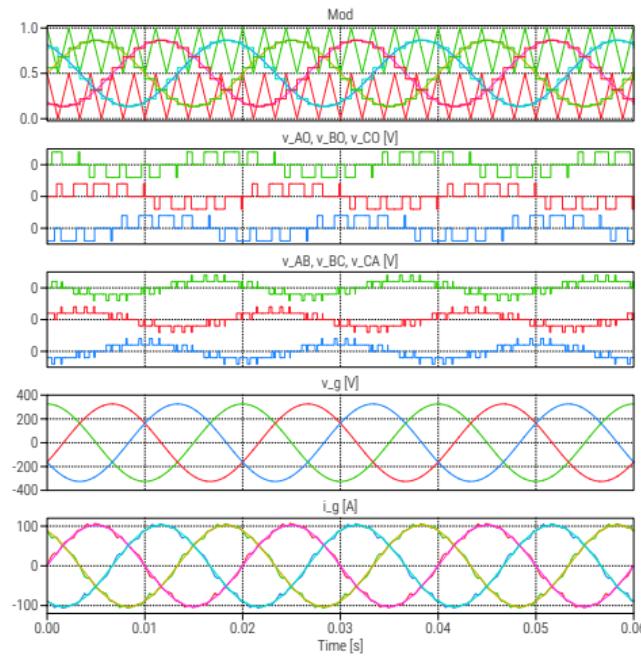

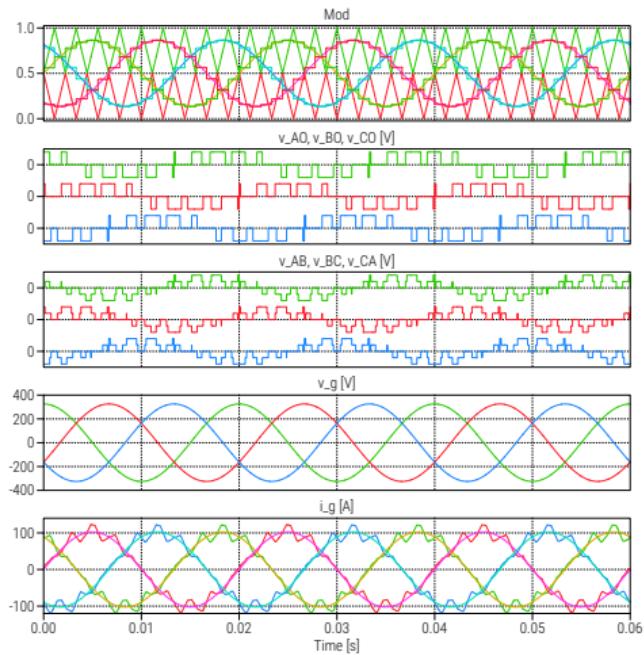

(a)

(b)

Figure 14 Typical waveform for a 3L NPC inverter,  $V_{DC} = 800$  V,  $f_{sw} = 450$  Hz,  $S = 50$  kVA,  $\phi = \pi/6$ , asymmetrical sampling: (a) PD-PWM and (b) APOD-PWM (POD-PWM is identical to APOD-PWM for 3L).

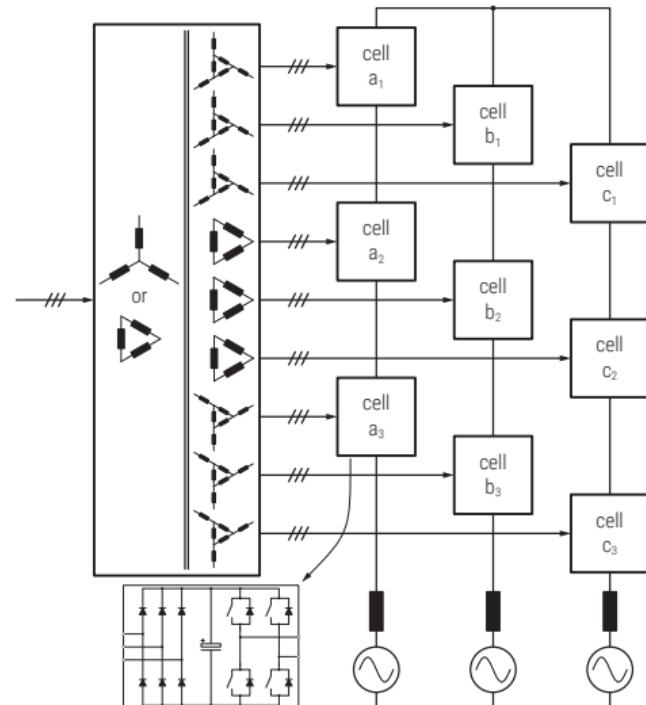

# CASCADED H-BRIDGE

- Enhanced reliability (operation with failed cells possible)

- Extension to higher voltages

- Series-connection of LV cells

- Externally supplied series-connected cells (McMurray 1969)

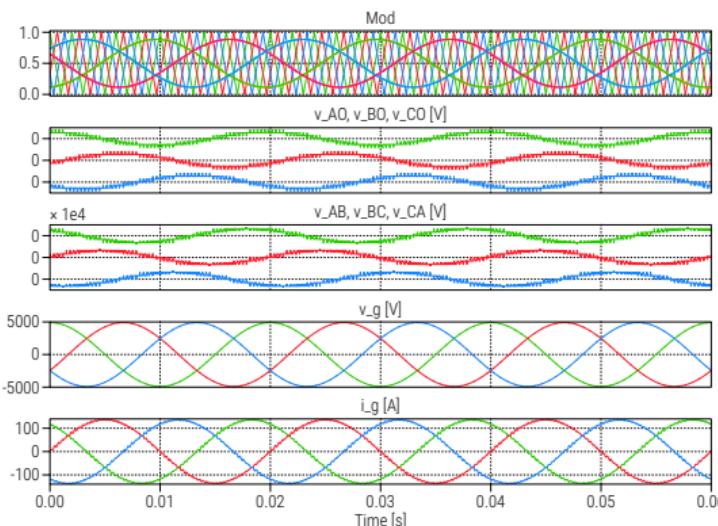

Figure 15 Operation waveforms for  $v_{g,LL} = 6 \text{ kV}$ ,  $S = 1 \text{ MVA}$ ,  $\phi = \pi/6$ ,  $N_{\text{cells}} = 3$ ,  $f_{\text{sw/GBT}} = 500 \text{ Hz}$ , PS-PWM, bipolar modulation for the cell.

Figure 16 Cascaded H-bridge with externally supplied cells (Robicon drive). Unidirectional power flow!

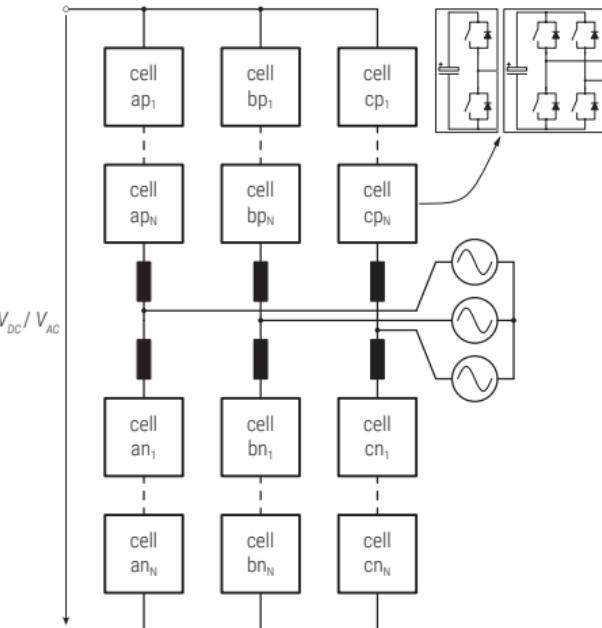

# MODULAR MULTILEVEL CONVERTER

- ▶ Avoid large bulky transformer(s) of CHB

- ▶ For MV and HV applications

- ▶ HVDC, grid support & frequency support (STATCOM), frequency conversion (rail interties), MV drives, shaft generator, etc.

Figure 17 HVDC hall from Siemens.

Figure 18 Double-star modular multilevel converter (Marquardt 2002).