Slobodan N. Vukosavic

# Grid-Side Converters Control and Design

Interfacing Between the AC Grid and

Renewable Power Sources

# **Power Electronics and Power Systems**

## **Series Editors**

Joe H. Chow, Rensselaer Polytechnic Institute, Troy, New York, USA

Alex M. Stankovic, Tufts University, Medford, Massachusetts, USA

David J. Hill, University of Hong Kong, Pok Fu Lam, Hong Kong

The Power Electronics and Power Systems Series encompasses power electronics, electric power restructuring, and holistic coverage of power systems. The Series comprises advanced textbooks, state-of-the-art titles, research monographs, professional books, and reference works related to the areas of electric power transmission and distribution, energy markets and regulation, electronic devices, electric machines and drives, computational techniques, and power converters and inverters. The Series features leading international scholars and researchers within authored books and edited compilations. All titles are peer reviewed prior to publication to ensure the highest quality content. To inquire about contributing to the Power Electronics and Power Systems Series, please contact Dr. Joe Chow, Administrative Dean of the College of Engineering and Professor of Electrical, Computer and Systems Engineering, Rensselaer Polytechnic Institute, Jonsson Engineering Center, Office 7012, 110 8th Street, Troy, NY USA, 518-276-6374, [chowj@rpi.edu](mailto:chowj@rpi.edu).

More information about this series at <http://www.springer.com/series/6403>

Slobodan N. Vukosavic

# Grid-Side Converters Control and Design

Interfacing Between the AC Grid and

Renewable Power Sources

Springer

Slobodan N. Vukosavic

Department of Electrical Engineering

University of Belgrade

Belgrade, Serbia

Serbian Academy of Sciences and Arts

Belgrade, Serbia

Library of Congress Control Number: 2018932557

© Springer International Publishing AG, part of Springer Nature 2018

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part

of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations,

recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or

information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar

methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by the registered company Springer International Publishing AG part of Springer Nature.

The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

*To my parents, Anka and Nikota Vukosavić,

whose love and guidance remain with me.*

# Preface

This textbook is intended for undergraduate students at final years of electrical engineering. It is also recommended for students preparing capstone project where they need to understand, model, supply, control, and specify grid-side converters in micro-grids, distribution grids, and residential, commercial, and industrial applications. At the same time, it can be used as a valuable reference for other engineering disciplines involved with smart grids, renewable sources, and energy accumulation. It is also suggested to postgraduates and engineers aspired to development of electronically controlled production, transmission, distribution, and use of electrical energy. Unlike majority of textbooks on this subject, this book requires a rather limited background. Wherever possible, an effort is made to provide the text approachable to students and engineers in engineering disciplines other than electrical.

The scope of this textbook is to provide basic knowledge and skills in designing and controlling the grid-side inverters, in the electronically controlled static power converters that are becoming a key part in smart grids, as well as in new, power electronics-based systems for production, transmission, distribution, and use of electrical energy. Basic engineering considerations are used to introduce the salient features of grid-side power converters in intuitive manner, easy to recall and repeat. The book prepares the reader to comprehend the key properties and roles of grid-side converters, to analyze their steady-state and transient characteristics, to obtain basic notions on their design and control, to evaluate the effect of electronically controlled loads in ac grids, to understand the changes introduced by replacing traditional synchronous machines by source-side converters, to consider the effects of an increased number of power electronic devices on power system controls and protections, and to foresee the future developments and related requirements.

Discussion, analysis, and knowledge development on grid-side power converters and the introduction of basic skills are suited for the electrical engineering students in their final year of undergraduate studies. Required background includes mathematics, physics, and introductory courses of power electronics, control theory, and power engineering. The textbook is made accessible to readers without the advanced

background in the subject matters. An attempt is made to prepare a self-contained book. The book comprises questions and answers and solved problems wherever the learning process requires an overview. The chapters comprise an appropriate set of exercises, problems, and design tasks, arranged to reinstate and use the relevant knowledge. Wherever it is needed, the book includes extended reinstatements and explanations of the required skill and prerequisites. The approach and method used in this textbook comes from the 22 years of author's experience in teaching electrical engineering at the University of Belgrade.

## Readership

This book is primarily suited for the electrical engineering undergraduates in their final year. It is also suggested to postgraduates of all engineering disciplines that plan to major in power electronics, renewables, smart grids, and other areas focused on developing a novel, power electronics-based production, transmission, distribution, and use of electrical energy. The book is also recommended to students that prepare capstone project in one of the areas. The book may also serve as a valuable reference for engineers in other engineering disciplines that are involved with the subject matter.

## Prerequisites

Required background includes basic mathematics, physics, engineering fundamentals, as well as introductory courses of power electronics, control theory, and power engineering. The textbook is made accessible to readers without the advanced background in these disciplines. It is suited for the students of electrical engineering on their last year of undergraduate studies. Discussion, analysis, and knowledge development on grid-side power converters and the introduction of basic skills are also suited for other engineering students on their postgraduate studies. Individual chapters comprise questions and answers, as well as solved problems wherever it is required by the learning process. Wherever it is needed, the book includes extended reinstatements and explanations of the required skill and prerequisites.

## Objectives

- Using basic engineering considerations to introduce principles of energy conversion within basic topologies of grid-side converters

- Providing relevant knowledge and skills in pulse width modulation of two-level and multilevel converters. Comprehending the PWM noise, the current ripple, and the necessary passive filters

- Acquiring skills in analyzing and designing stationary frame, synchronous frame, and resonant current controllers. Comprehending the controller capability to suppress the input disturbances and the voltage disturbances, to provide a well-damped, overshoot-free step response, and to secure the desired robustness

- Studying the process of the feedback acquisition, understanding the basic current sensors, recalling the sampling process and the sampling theorem, designing anti-aliasing filters, and introducing oversampling, decimation, and one-PWM-period averaging

- Mastering the skills of modeling discrete-time current control systems, designing the controller structure, compensating the transport delays, and deriving the optimum feedback gains

- Analyzing the need to suppress the low-order harmonics, comprehending the role of the voltage-disturbance rejection of the current controller, introduction of the active resistance feedback, and designing the controller which encompasses the active resistance feedback

- Studying and apprehending the control of the active and reactive power injected into the ac grid by means of  $d$ -axis and  $q$ -axis current

- Understanding control of the dc-bus voltage between the two back-to-back inverters used in a wind-power converter set which includes the generator-side inverter and the grid-side converter

- Analyzing the synchronization of the grid-side converter by means of the phase-locked loop. The impact of the phase-locked loop on the power transients caused by the grid frequency change. Control means for the grid-side power converters which emulate the transient response of conventional synchronous machine

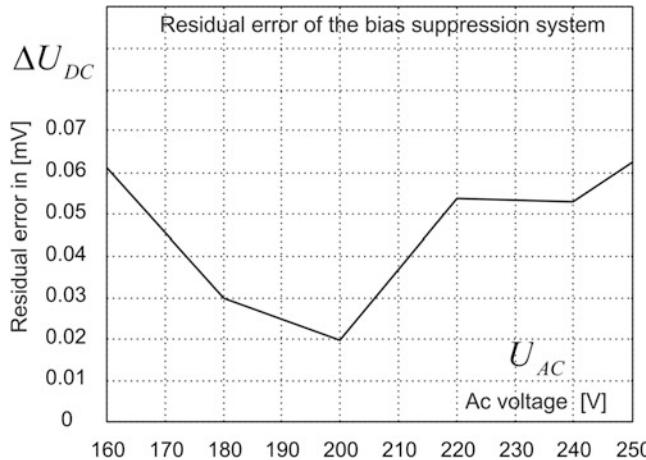

- Understanding injection of parasitic dc-bias into ac grids. Study of sensitivity of distribution transformers to the bias. The sensors for detection of small dc-bias voltages embedded into ac voltages. Active suppression of the dc-bias voltages by means of grid-side converters equipped with the dc-bias sensors and the bias-suppression algorithm

## Teaching Approach

- The emphasis is given to the system view, explaining external characteristics of grid-side converters. The basic functionality and controls are of the main interest. Design and construction aspects are of secondary importance.

- Where needed, introductory parts of teaching units comprise repetition of the required background which is applied through solved problems.

- Mathematics is reduced to a necessary minimum.

- The main goal is development and use of mathematical models and transfer functions of grid-side converters. At the same time, the focus is kept on physical insight of the power conversion processes.

- Although the hardware design is out of the scope, some most relevant concepts and design skills are introduced and explained. The book also explains some secondary effects, indicating the cases and conditions where the secondary phenomena cannot be neglected.

## Field of Application

This book discusses power electronics, power systems, smart grids, and other application of electronically controlled static power converters in production, transmission, and distribution of electrical energy. Analysis and considerations are focused on basic functionality, topologies, controls, and static and dynamic characteristics of power electronic systems used in conjunction with micro-grids, smart grids, renewable sources, static transformers, bus converters, load-side converters, accumulation devices, static VAR compensators, and other similar applications. Contemporary trends in power systems include the introduction of dc voltages and currents in transmission and distribution of electrical energy, the integration of advanced communication networks that enable remote commands and controls, distributed generation of electrical energy, distributed accumulation resources, and new, online negotiated energy transactions that contribute to the benefit of both the utilities and the clients.

Design, control, and use of power electronic systems in electrical power applications requires the knowledge and skills in power converter topologies, pulse width modulation algorithms, acquisition and filtering of the feedback signals, designing and tuning of the digital current controller, controlling the active and reactive power, suppressing the low-frequency line harmonics, measuring and suppressing the parasitic dc-bias in ac grids, using the phase-locked loop to synchronize the grid-side converters to the ac grid voltages, and setting up the converter controls so as to mimic the behavior of conventional synchronous machines. This book comprises considerations, analysis, studies, and examples that facilitate the engineering efforts in designated area.

Belgrade, Serbia

Slobodan N. Vukosavic

# Acknowledgment

The author is indebted to Prof. Aleksandar Stanković, Dr. Igor Cvetković, Ing. Ljiljana Perić, Dr. Petar Matić, Dr. Žarko Janda, Ing. Luka Lopin and Dr. Željko Despotović who read through the first edition of the book and made suggestion for improvements.

The author is grateful to his young colleagues, teaching assistants, postgraduate students, PhD students, and young professors who provided comments and suggestions, read through the chapters and commented the questions, problems, solutions and index terms.

The author would also like to thank Darko Marčetić, Nikola Perić, Branko Blanuša, Petar Grbović, Dragan Mihić, and Nikola Lepojević.

# Contents

|          |                                                  |    |

|----------|--------------------------------------------------|----|

| <b>1</b> | <b>Introduction</b>                              | 1  |

| 1.1      | DC and AC Grids                                  | 2  |

| 1.1.1    | Conventional AC Grids                            | 2  |

| 1.1.2    | DC Transmission Lines                            | 2  |

| 1.1.3    | DC Distribution                                  | 3  |

| 1.1.4    | DC Versus AC                                     | 4  |

| 1.2      | Topologies and Functionality                     | 4  |

| 1.2.1    | Medium- and High-Voltage Converters              | 4  |

| 1.2.2    | The Voltage Control in Grid-Side Converters      | 6  |

| 1.2.3    | Current Control in Grid-Side Converters          | 6  |

| 1.3      | The Impact of Grid-Side Converters               | 7  |

| 1.3.1    | DC Bias and Line Harmonics                       | 7  |

| 1.3.2    | Behavioral Model of Load-Side Converters         | 8  |

| 1.3.3    | Behavioral Model of Source-Side Converters       | 9  |

| 1.4      | Control Techniques for Grid-Side Converters      | 10 |

| 1.4.1    | Robust and Error-Free Feedback Acquisition       | 10 |

| 1.4.2    | High Bandwidth Digital Current Controllers       | 11 |

| 1.4.3    | Suppression of Low-Order Harmonics               | 12 |

| 1.4.4    | Synchronization and Power-Frequency Change       | 12 |

|          | References                                       | 13 |

| <b>2</b> | <b>PWM Voltage Actuator</b>                      | 15 |

| 2.1      | Two-Level Inverters with Symmetrical PWM         | 16 |

| 2.1.1    | Pulse Width Modulation                           | 16 |

| 2.1.2    | Pulsed Voltages and the Current Ripple           | 18 |

| 2.1.3    | Star Connection and Line Voltages                | 19 |

| 2.1.4    | Symmetrical and Asymmetrical PWM Carrier         | 22 |

| 2.1.5    | Double Update Rate                               | 23 |

| 2.1.6    | The Output Voltage Waveform and Spectrum         | 24 |

| 2.2      | Space Vector Modulation with DI and DD Sequences | 28 |

| 2.2.1    | The Switching States and the Voltage Vectors     | 28 |

|          |                                                                        |            |

|----------|------------------------------------------------------------------------|------------|

| 2.2.2    | The Switching Sequence and Dwell Times . . . . .                       | 31         |

| 2.2.3    | DD Switching Sequence . . . . .                                        | 34         |

| 2.2.4    | DI Switching Sequence . . . . .                                        | 34         |

| 2.2.5    | The Maximum Output Voltage with DI Sequence . . . . .                  | 36         |

| 2.2.6    | Symmetrical PWM with Common Mode Signals . . . . .                     | 39         |

| 2.3      | Lockout Time Error and Compensation . . . . .                          | 42         |

| 2.3.1    | Implementation of the Lockout Time . . . . .                           | 42         |

| 2.3.2    | The Voltage Error Caused by the Lockout Time . . . . .                 | 44         |

| 2.3.3    | Compensation of the Lockout Time Voltage Errors . . . . .              | 45         |

| 2.4      | Design of the Output L Filters and LCL Filters . . . . .               | 47         |

| 2.4.1    | The rms Value of the Current Ripple . . . . .                          | 47         |

| 2.4.2    | The L-Type Output Filter . . . . .                                     | 48         |

| 2.4.3    | The LCL-Type Output Filter . . . . .                                   | 49         |

| 2.5      | Multilevel Inverters and Their PWM Techniques . . . . .                | 53         |

| 2.5.1    | Three-Level Inverters . . . . .                                        | 54         |

| 2.5.2    | The Phase Voltages and Line Voltages . . . . .                         | 55         |

| 2.5.3    | Space Vector Modulation in Multilevel Inverters . . . . .              | 57         |

| 2.6      | Summary . . . . .                                                      | 60         |

| <b>3</b> | <b>Acquisition of the Feedback Signals . . . . .</b>                   | <b>61</b>  |

| 3.1      | Current Sensors and Galvanic Insulation . . . . .                      | 61         |

| 3.1.1    | Shunt-Based Current Sensing . . . . .                                  | 62         |

| 3.1.2    | Current Transformers . . . . .                                         | 63         |

| 3.1.3    | Rogowski Coils . . . . .                                               | 66         |

| 3.1.4    | Hall Effect and Fluxgate Current Sensors . . . . .                     | 69         |

| 3.2      | Analogue Filtering and Sampling . . . . .                              | 71         |

| 3.2.1    | Gain and Offset Adjustment . . . . .                                   | 71         |

| 3.2.2    | Analogue-to-Digital Conversion . . . . .                               | 75         |

| 3.2.3    | Sampling Process . . . . .                                             | 76         |

| 3.2.4    | The Alias-Free Sampling . . . . .                                      | 80         |

| 3.2.5    | Low-Pass RC Filter as an Anti-alias Filter . . . . .                   | 87         |

| 3.2.6    | Second-Order Low-Pass Anti-alias Filter . . . . .                      | 89         |

| 3.2.7    | Center-Pulse Sampling . . . . .                                        | 90         |

| 3.3      | Oversampling-Based Feedback Acquisition . . . . .                      | 93         |

| 3.3.1    | One-PWM-Period Averaging . . . . .                                     | 93         |

| 3.3.2    | Oversampling and Averaging . . . . .                                   | 94         |

| 3.3.3    | Practical Implementation . . . . .                                     | 95         |

| 3.3.4    | Pulse Transfer Function of the Feedback Subsystem . . . . .            | 96         |

| 3.3.5    | Current Measurement in LCL Filters . . . . .                           | 98         |

| <b>4</b> | <b>Introduction to Current Control . . . . .</b>                       | <b>103</b> |

| 4.1      | The Model of the Load . . . . .                                        | 105        |

| 4.1.1    | The Three-Phase Load . . . . .                                         | 105        |

| 4.1.2    | The Model of the Load in $\alpha$ - $\beta$ Coordinate Frame . . . . . | 106        |

| 4.1.3    | The Model of the Load in $d$ - $q$ Frame . . . . .                     | 108        |

|            |                                                                                        |     |

|------------|----------------------------------------------------------------------------------------|-----|

| <b>4.2</b> | <b>The PI Current Controllers . . . . .</b>                                            | 110 |

| 4.2.1      | The PI Controller in $\alpha$ - $\beta$ Frame . . . . .                                | 111 |

| 4.2.2      | The PI Controller in $d$ - $q$ Frame . . . . .                                         | 112 |

| <b>4.3</b> | <b>Decoupling Current Controller in <math>d</math>-<math>q</math> Frame . . . . .</b>  | 114 |

| 4.3.1      | Basic Principles of Internal Model Control . . . . .                                   | 115 |

| 4.3.2      | Decoupling Controller . . . . .                                                        | 115 |

| <b>4.4</b> | <b>Resonant Current Controllers . . . . .</b>                                          | 116 |

| 4.4.1      | Transformation of the $d$ - $q$ Frame Controller in $\alpha$ - $\beta$ Frame . . . . . | 117 |

| 4.4.2      | The Resonant Controller in $\alpha$ - $\beta$ Frame . . . . .                          | 118 |

| 4.4.3      | Dynamic Properties of the Resonant Controller . . . . .                                | 119 |

| <b>4.5</b> | <b>Disturbance Rejection . . . . .</b>                                                 | 121 |

| 4.5.1      | Disturbance Rejection with $d$ - $q$ Frame PI Controller . . . . .                     | 121 |

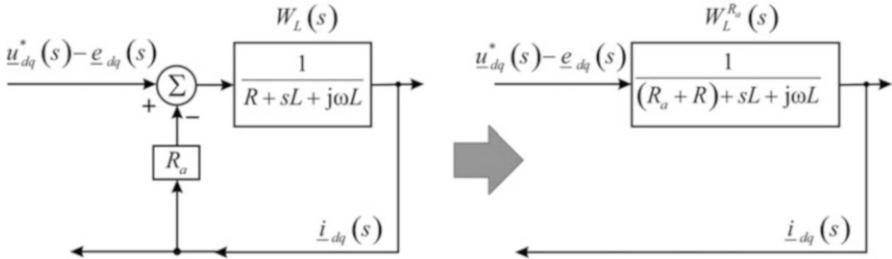

| 4.5.2      | Active Resistance Feedback . . . . .                                                   | 123 |

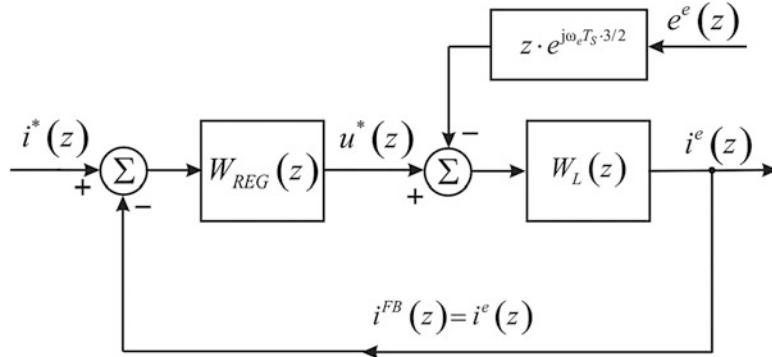

| <b>5</b>   | <b>Discrete-Time Synchronous Frame Controller . . . . .</b>                            | 129 |

| <b>5.1</b> | <b>Discrete-Time Controller with Center-Pulse Sampling . . . . .</b>                   | 130 |

| 5.1.1      | The Pulse Transfer Function of the Load . . . . .                                      | 130 |

| 5.1.2      | Design of the Controller Structure . . . . .                                           | 132 |

| 5.1.3      | Parameter Setting . . . . .                                                            | 134 |

| 5.1.4      | Disturbance Rejection . . . . .                                                        | 136 |

| <b>5.2</b> | <b>Current Controller with Oversampling-Based Feedback . . . . .</b>                   | 139 |

| 5.2.1      | The Pulse Transfer Function of the Feedback Path . . . . .                             | 139 |

| 5.2.2      | Design of the Controller Structure . . . . .                                           | 140 |

| 5.2.3      | Parameter Setting . . . . .                                                            | 141 |

| 5.2.4      | Disturbance Rejection . . . . .                                                        | 143 |

| <b>5.3</b> | <b>Current Controllers with Series Compensator . . . . .</b>                           | 144 |

| 5.3.1      | Synchronous Sampling with Series Compensator . . . . .                                 | 144 |

| 5.3.2      | One-PWM-Period Averaging with Series Compensator . . . . .                             | 146 |

| <b>5.4</b> | <b>Experimental Runs with IMC-Based Controllers . . . . .</b>                          | 148 |

| 5.4.1      | Parameters of the Experimental Setup . . . . .                                         | 149 |

| 5.4.2      | Experimental Results . . . . .                                                         | 149 |

| <b>6</b>   | <b>Scheduling of the Control Tasks . . . . .</b>                                       | 157 |

| <b>6.1</b> | <b>Scheduling Schemes . . . . .</b>                                                    | 157 |

| 6.1.1      | Conventional Scheduling . . . . .                                                      | 158 |

| 6.1.2      | Advanced Scheduling . . . . .                                                          | 160 |

| <b>6.2</b> | <b>Pulse Transfer Function with Advanced Scheduling . . . . .</b>                      | 161 |

| 6.2.1      | Pulse Transfer Function of the Load . . . . .                                          | 161 |

| 6.2.2      | Design of the Controller Structure . . . . .                                           | 163 |

| 6.2.3      | Closed-Loop and Disturbance Transfer Functions . . . . .                               | 163 |

| 6.2.4      | Parameter Setting and the Closed-Loop Performance . . . . .                            | 165 |

| <b>6.3</b> | <b>Advanced Scheduling with Series Compensator . . . . .</b>                           | 167 |

| 6.3.1      | Closed-Loop and Disturbance Transfer Functions . . . . .                               | 167 |

| 6.3.2      | Parameter Setting and the Closed-Loop Performance . . . . .                            | 169 |

|          |                                                                |            |

|----------|----------------------------------------------------------------|------------|

| 6.4      | Experimental Results . . . . .                                 | 170        |

| 6.4.1    | The Impact of the Computation Delay . . . . .                  | 171        |

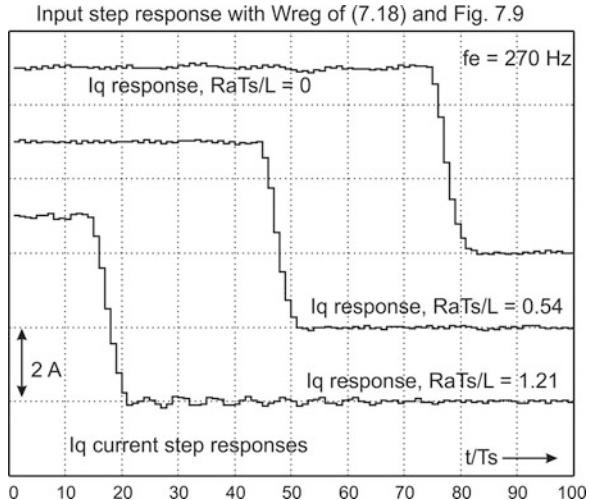

| 6.4.2    | Input Step Response . . . . .                                  | 172        |

| 6.4.3    | Robustness Against the Parameter Changes . . . . .             | 173        |

| <b>7</b> | <b>Disturbance Rejection . . . . .</b>                         | <b>183</b> |

| 7.1      | Active Resistance Feedback . . . . .                           | 183        |

| 7.1.1    | Equivalent Load with Synchronous Sampling . . . . .            | 184        |

| 7.1.2    | Equivalent Load with One-PWM-Period Averaging . . . . .        | 185        |

| 7.1.3    | Equivalent Load with the Advanced Scheduling . . . . .         | 186        |

| 7.1.4    | The Range of Stable $R_a$ Gains . . . . .                      | 187        |

| 7.2      | Design of Decoupling Controllers . . . . .                     | 188        |

| 7.2.1    | Conventional Scheduling with Synchronous Sampling . . . . .    | 188        |

| 7.2.2    | Conventional Scheduling with Feedback Averaging . . . . .      | 190        |

| 7.2.3    | Advanced Scheduling with Feedback Averaging . . . . .          | 191        |

| 7.3      | Disturbance Suppression in Synchronous Frame . . . . .         | 192        |

| 7.3.1    | The Applicable Range of $R_a$ Gains . . . . .                  | 193        |

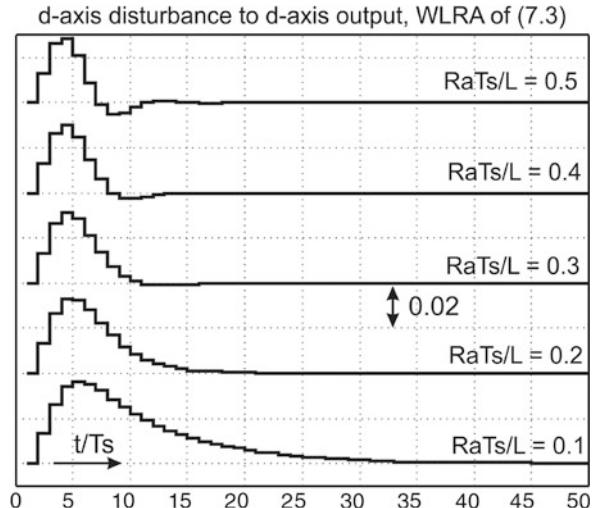

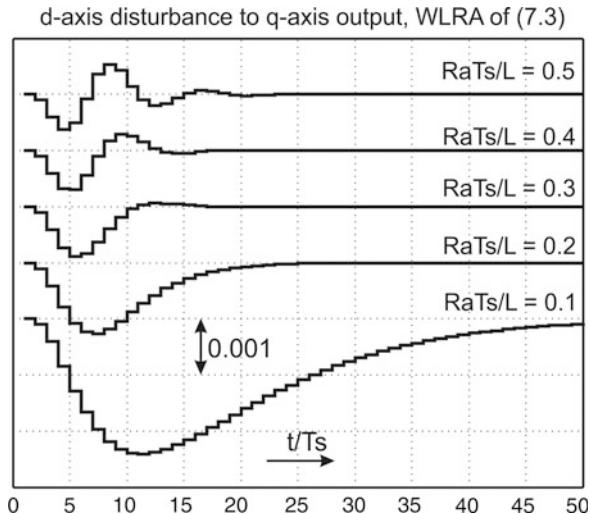

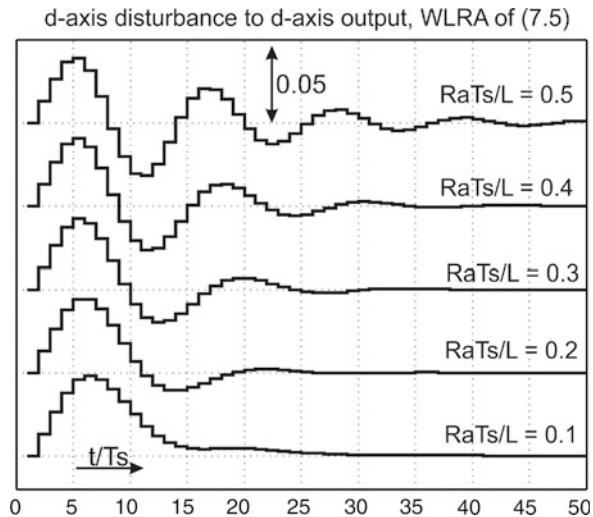

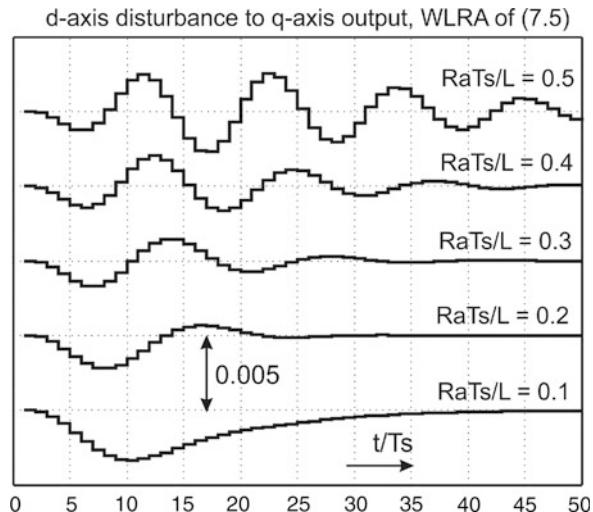

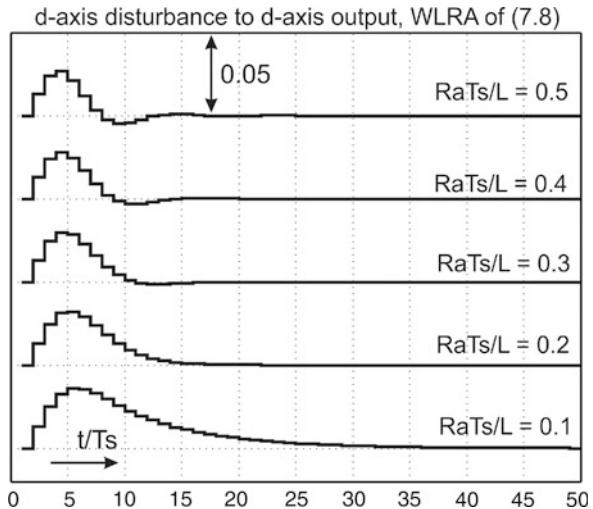

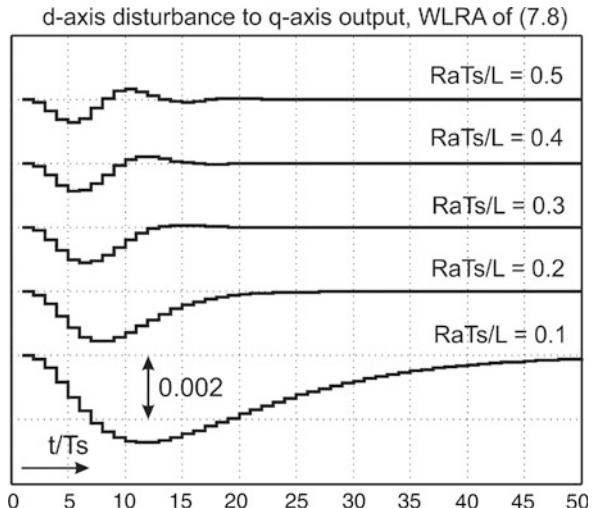

| 7.3.2    | Simulation of the Dynamic Response . . . . .                   | 194        |

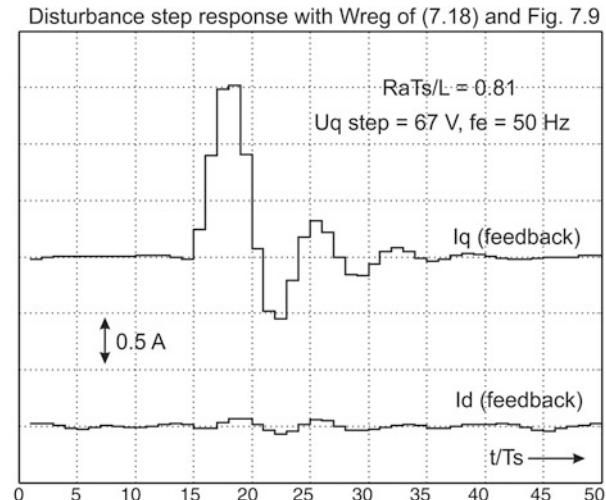

| 7.3.3    | Dynamic Response . . . . .                                     | 194        |

| 7.4      | Disturbance Suppression in Stationary Frame . . . . .          | 196        |

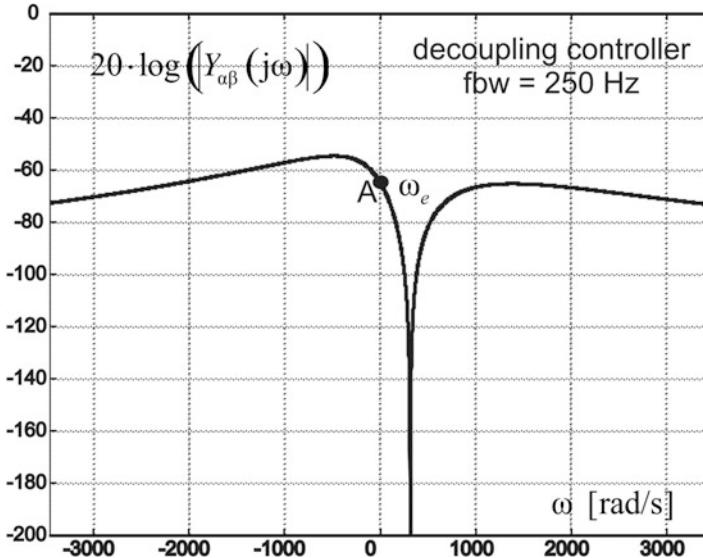

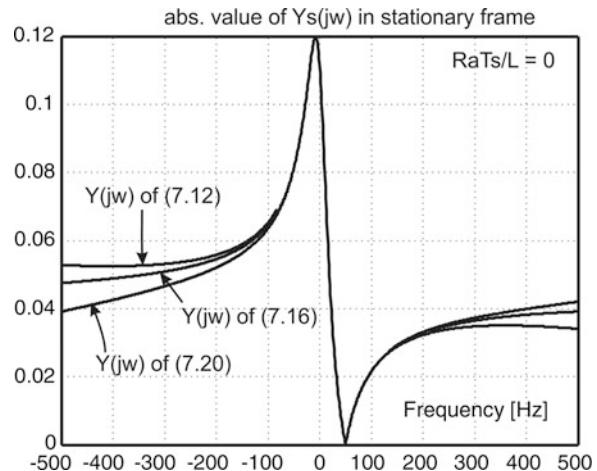

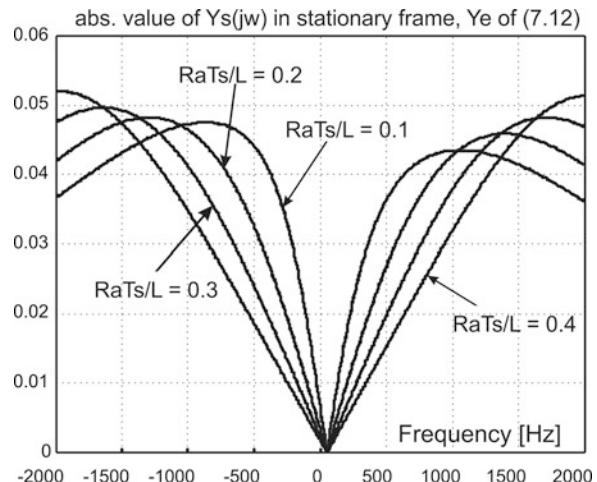

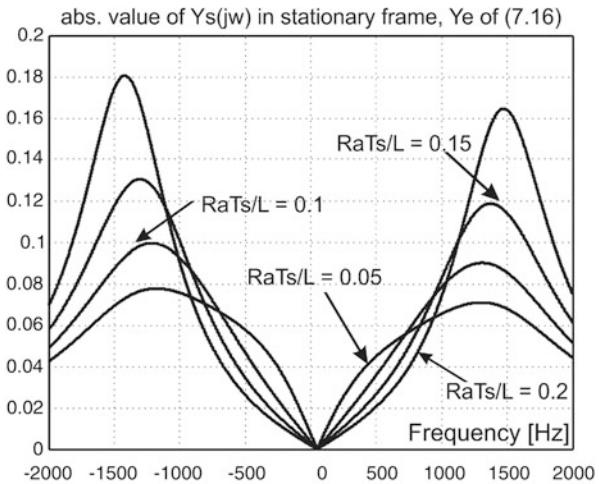

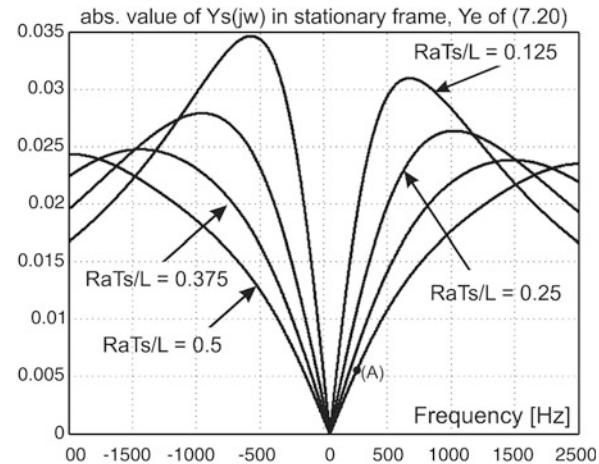

| 7.4.1    | The Frequency Characteristic of $Y^s$ with $R_a = 0$ . . . . . | 199        |

| 7.4.2    | The Frequency Characteristic of $Y^s$ with $R_a > 0$ . . . . . | 199        |

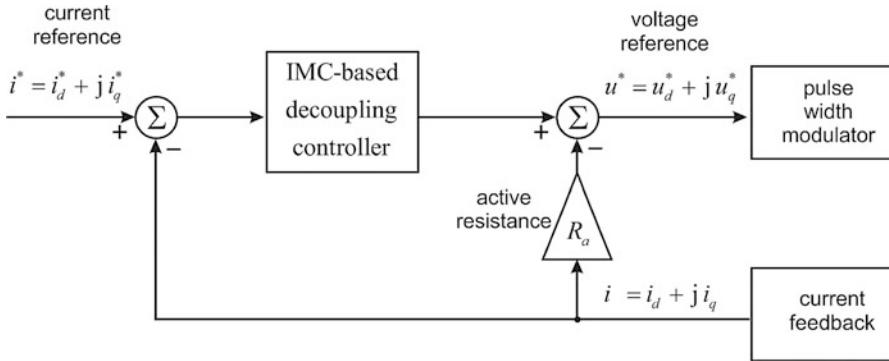

| 7.5      | Experimental Results . . . . .                                 | 202        |

| 7.5.1    | Parameters of the Experimental Setup . . . . .                 | 203        |

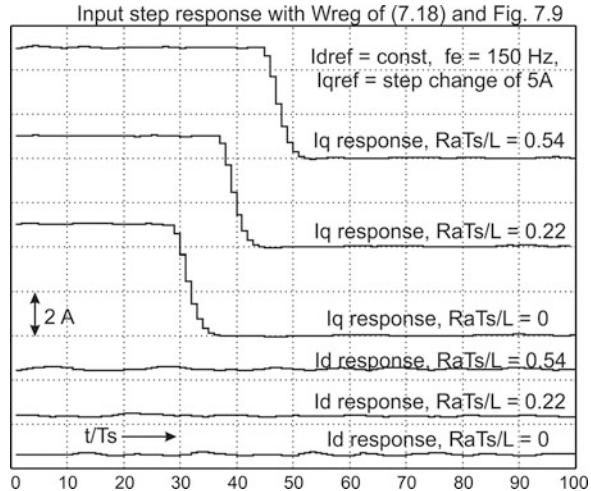

| 7.5.2    | Input Step Response . . . . .                                  | 203        |

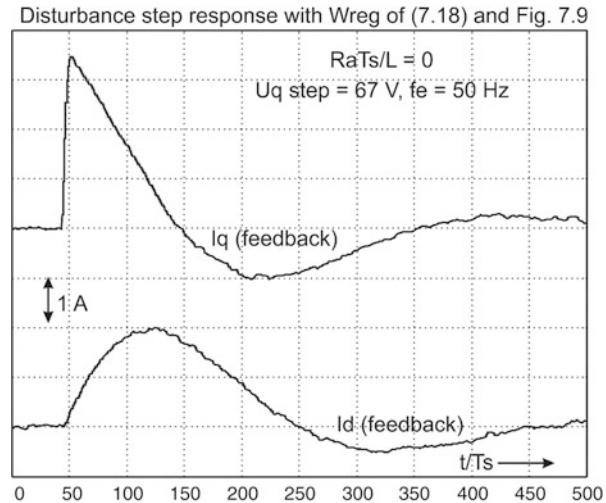

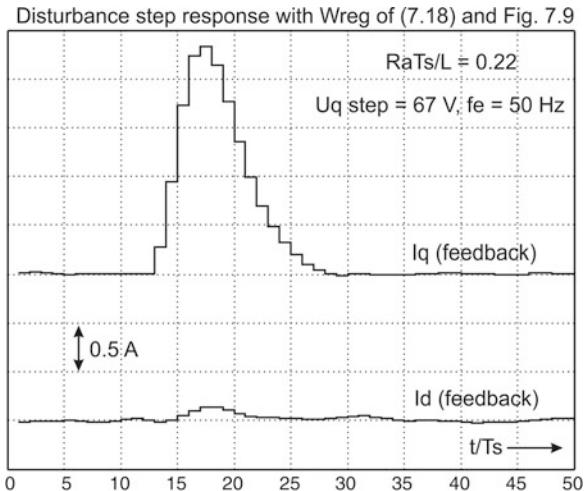

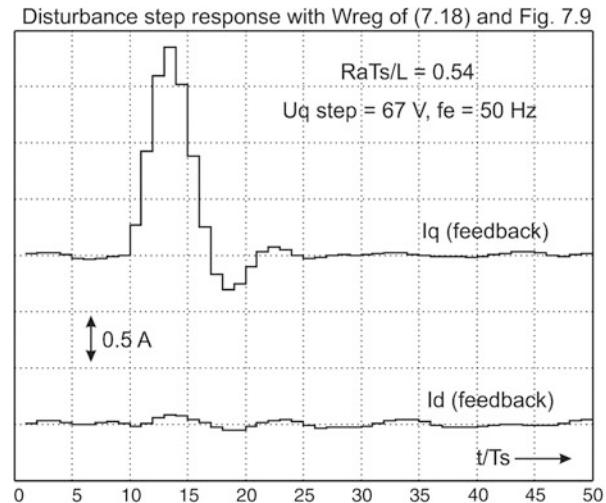

| 7.5.3    | Disturbance Rejection . . . . .                                | 204        |

| 7.6      | Concluding Remarks . . . . .                                   | 206        |

| <b>8</b> | <b>Synchronization and Control . . . . .</b>                   | <b>211</b> |

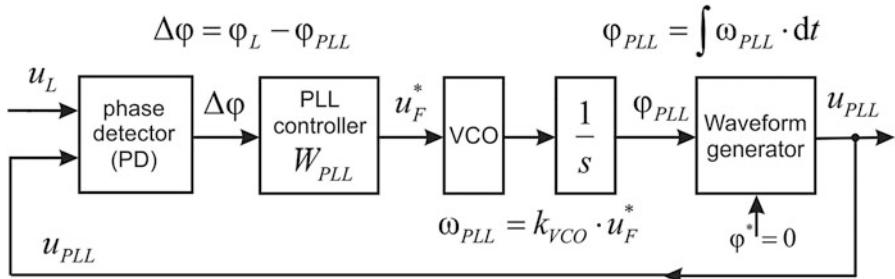

| 8.1      | Phase-Locked Loop . . . . .                                    | 212        |

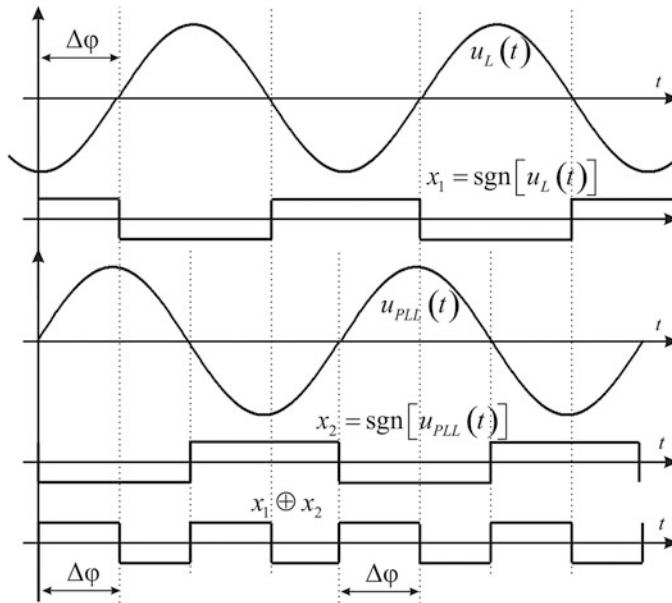

| 8.1.1    | The Phase Detector with a Multiplier . . . . .                 | 213        |

| 8.1.2    | Phase Detector with XOR Function . . . . .                     | 214        |

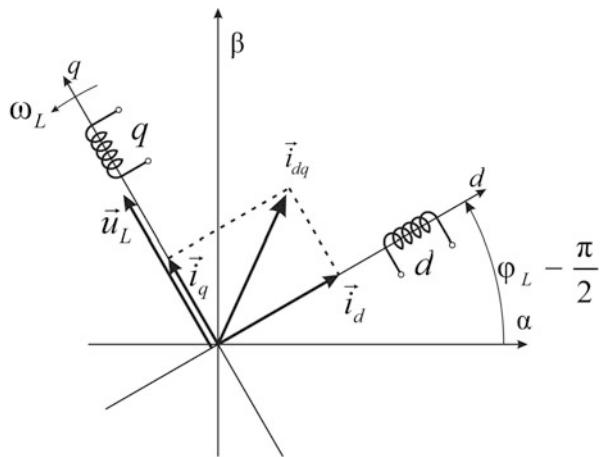

| 8.1.3    | The Phase Detector Based on the $d$ -Axis Voltage . . . . .    | 214        |

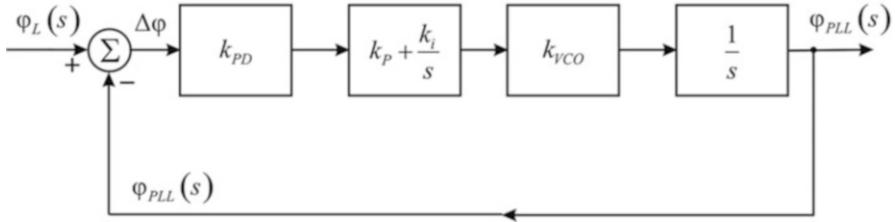

| 8.1.4    | The Closed-Loop Operation of the PLL . . . . .                 | 216        |

| 8.2      | Dynamic Response of Grid-Side Converters . . . . .             | 218        |

| 8.2.1    | Dynamic Response of Conventional Generators . . . . .          | 218        |

| 8.2.2    | The Impact of the Damper Winding . . . . .                     | 223        |

| 8.2.3    | Dynamic Response of the PLL-Driven Converter . . . . .         | 224        |

| 8.2.4    | Emulation of Synchronous Machines . . . . .                    | 228        |

| 8.2.5    | Negative Impedance . . . . .                                   | 230        |

| 8.3      | DC-Bus Control and Droop Control . . . . .                     | 232        |

| 8.3.1    | DC-Bus Control . . . . .                                       | 233        |

| 8.3.2    | Droop Control . . . . .                                        | 234        |

| 8.4      | DC-Bias Detection and Suppression . . . . .                    | 237        |

| 8.4.1    | Sensitivity of Distribution Transformers to DC-Bias . . . . .  | 238        |

|                                                   |      |

|---------------------------------------------------|------|

| <b>Contents</b>                                   | xvii |

| 8.4.2 Peak-Detection Methods . . . . .            | 241  |

| 8.4.3 Optimum Form of the Core . . . . .          | 244  |

| 8.4.4 Detection Based on Even Harmonics . . . . . | 248  |

| 8.4.5 Closed-Loop DC-Bias Suppression . . . . .   | 250  |

| References . . . . .                              | 257  |

| <b>Bibliography</b> . . . . .                     | 259  |

| <b>Index</b> . . . . .                            | 261  |

# List of Figures

|           |                                                                                                                                                         |    |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

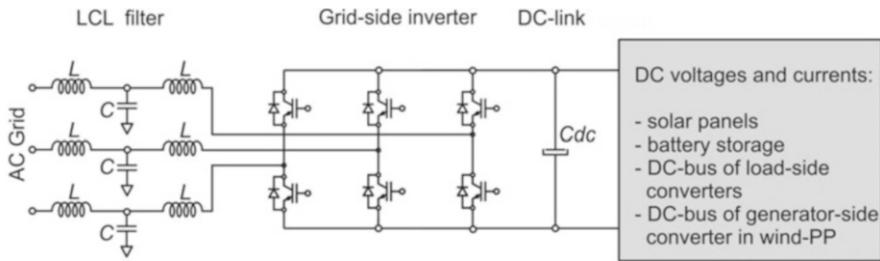

| Fig. 1.1  | Grid-side inverter in 0.4 kV ac grids .....                                                                                                             | 5  |

| Fig. 1.2  | One phase of three-level converter .....                                                                                                                | 5  |

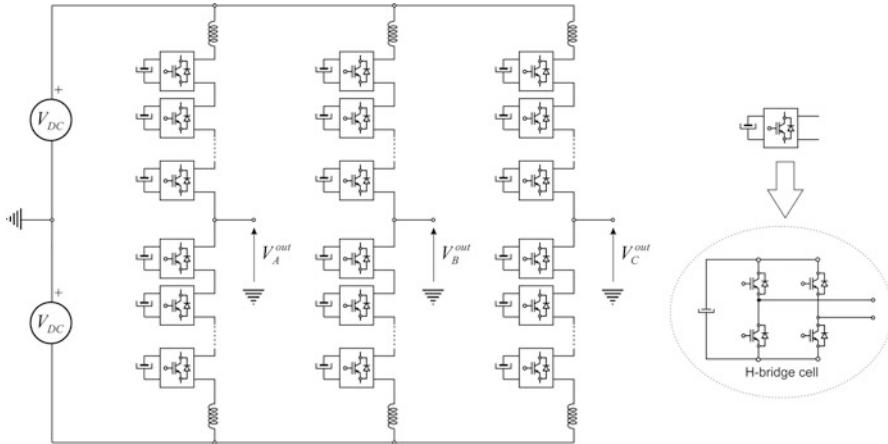

| Fig. 1.3  | Basic principle of multilevel multicell converters .....                                                                                                | 6  |

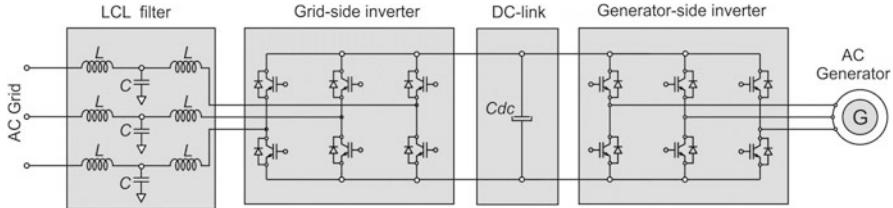

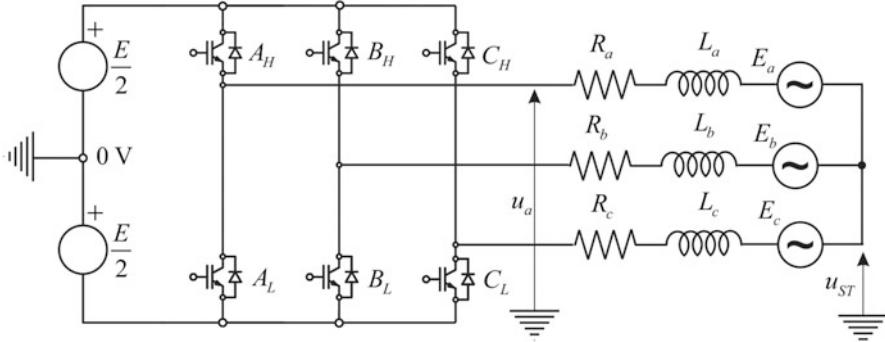

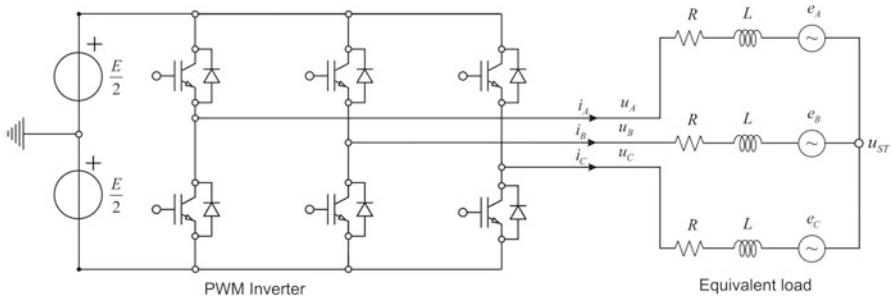

| Fig. 2.1  | Three-phase IGBT inverters as the voltage actuators in grid-side and generator-side converters of the wind power setup .....                            | 16 |

| Fig. 2.2  | Three-phase IGBT inverter with the three-phase load, approximated by $R-L$ series impedance and an electromotive force .....                            | 17 |

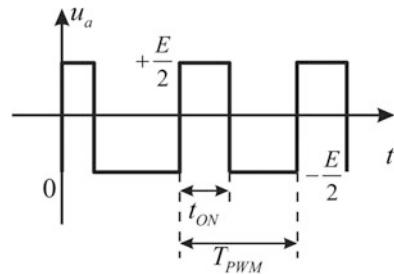

| Fig. 2.3  | Pulse-shaped phase voltage $u_a$ at the output of the inverter .....                                                                                    | 17 |

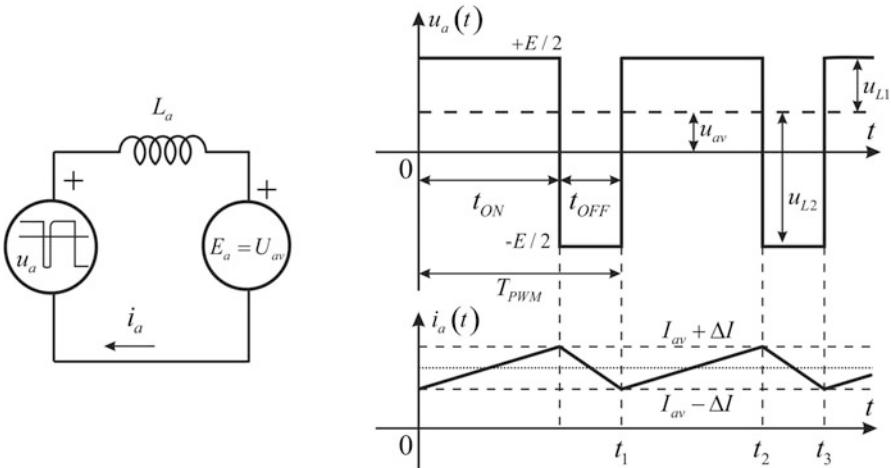

| Fig. 2.4  | The ripple $\Delta I$ of the phase current obtained from Fig. 2.2 with $u_{ST} = 0$ .....                                                               | 18 |

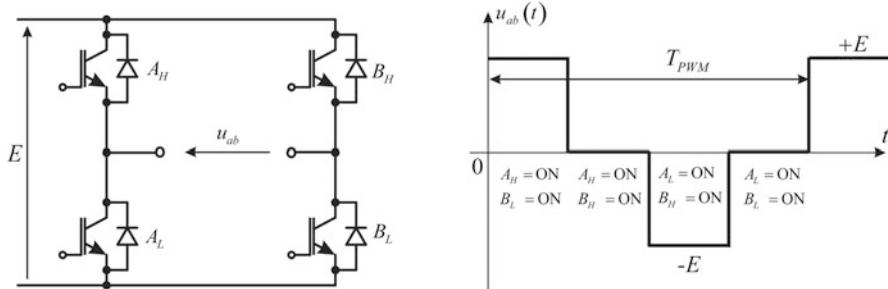

| Fig. 2.5  | Line-to-line voltage at the output of the inverter: four switching states and three levels .....                                                        | 20 |

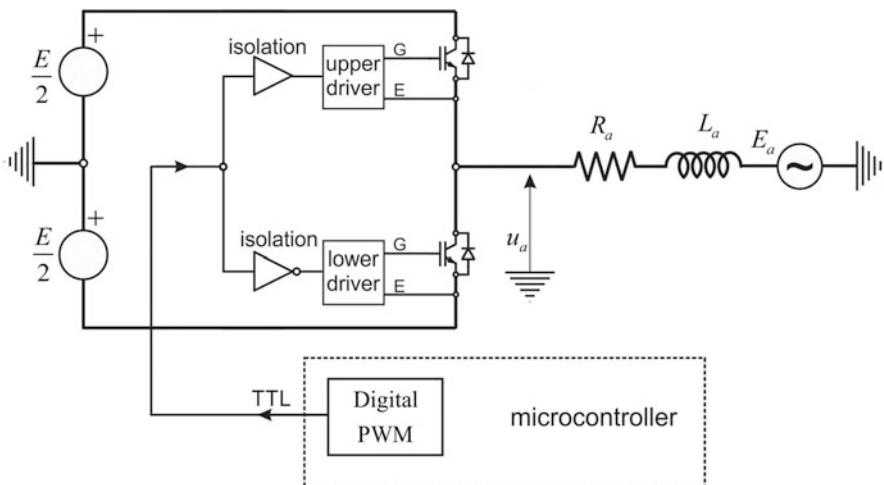

| Fig. 2.6  | The state of the power switches is controlled from a peripheral unit of the microcontroller which comprises programmable timers .....                   | 21 |

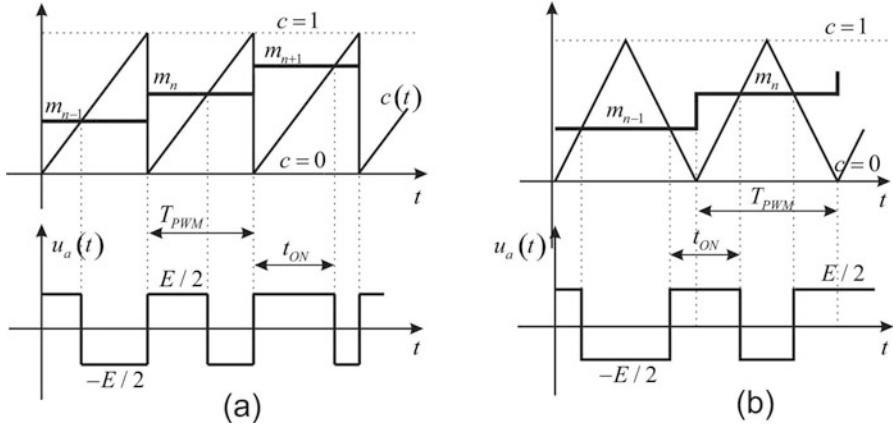

| Fig. 2.7  | Line-to-line voltage at the output of the inverter: four switching states and three levels .....                                                        | 23 |

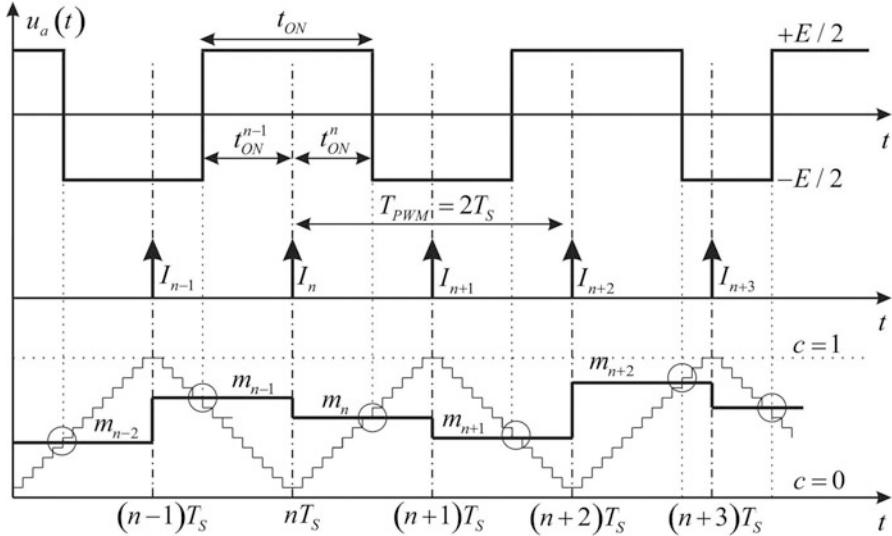

| Fig. 2.8  | Double-rate symmetrical PWM with corresponding phase voltage $u_a(t)$ .....                                                                             | 24 |

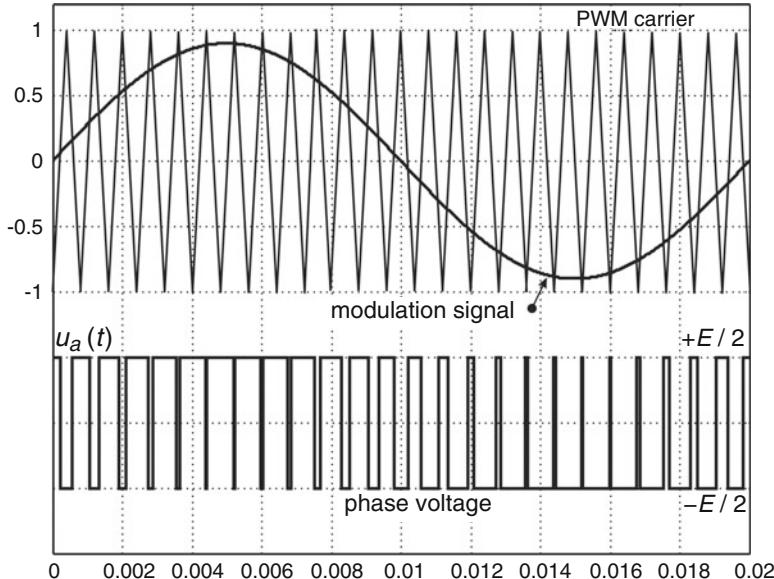

| Fig. 2.9  | PWM carrier, modulation signal, and the phase voltage $u_a(t)$ with symmetrical pulse width modulation .....                                            | 25 |

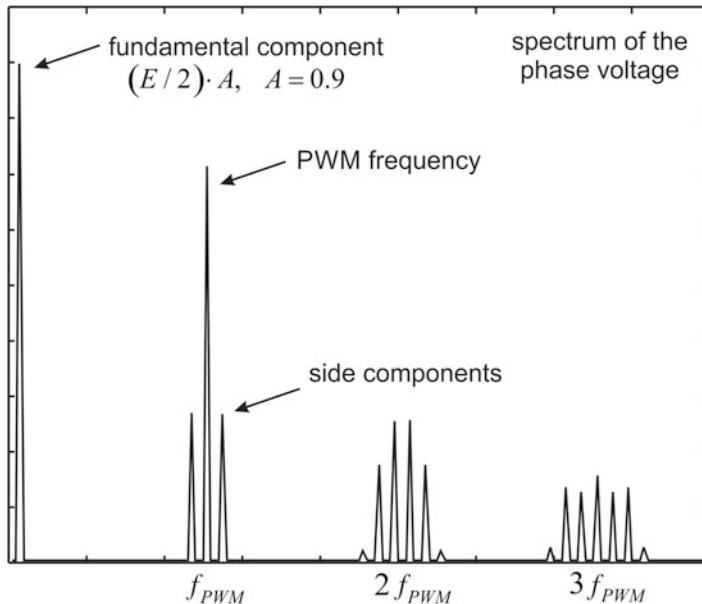

| Fig. 2.10 | The spectrum of the phase voltage $u_a(t)$ obtained with symmetrical pulse width modulation .....                                                       | 26 |

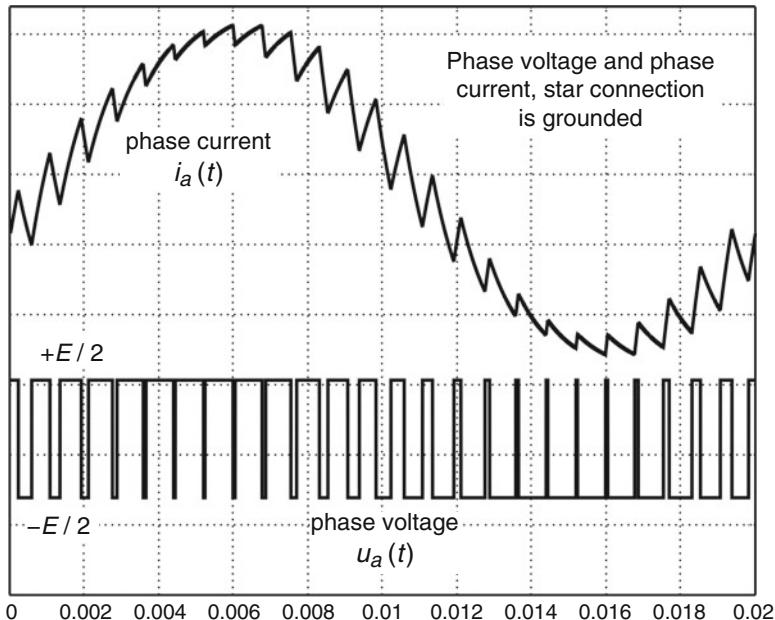

| Fig. 2.11 | The phase current and the phase voltage obtained at $f_F = 50$ Hz, with $U_m/U_{\max} = 0.9$ , $L/R = 1$ ms and with the star connection grounded ..... | 27 |

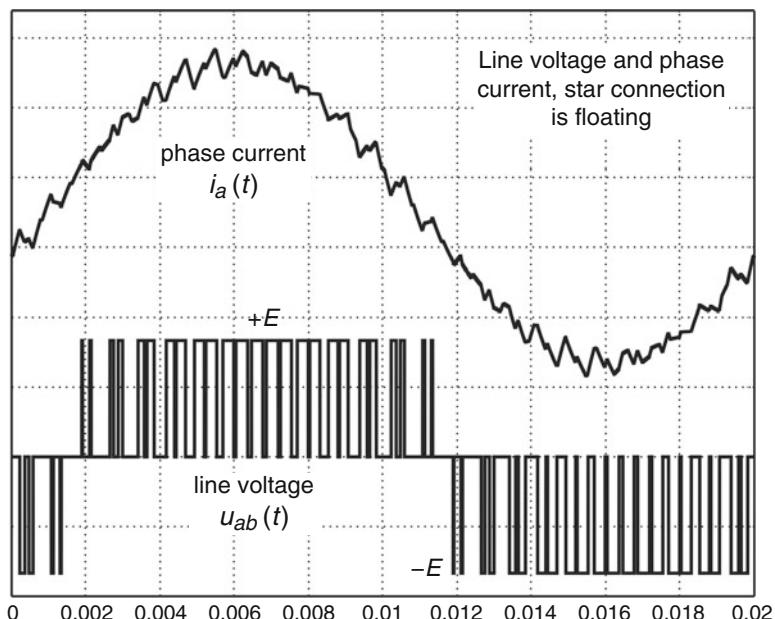

| Fig. 2.12 | The phase current and the line voltage obtained at $f_F = 50$ Hz, with $U_m/U_{\max} = 0.9$ , $L/R = 1$ ms and with the star connection floating .....  | 27 |

|           |                                                                                                                                                                                                                                                     |    |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

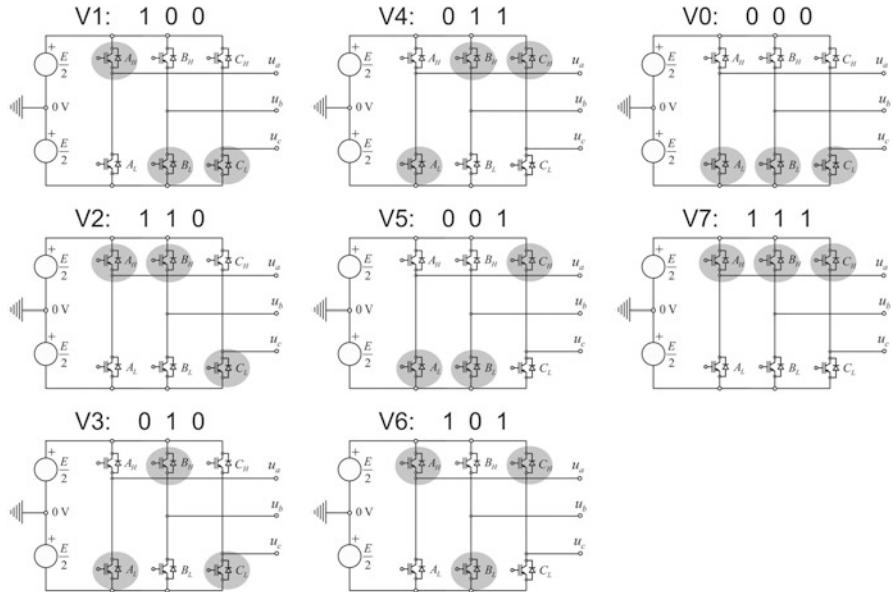

| Fig. 2.13 | The eight switching states of a three-phase inverter .....                                                                                                                                                                                          | 29 |

| Fig. 2.14 | Clarke's transformation represents the phase voltages $u_a$ , $u_b$ , and $u_c$ as a voltage vector in orthogonal $\alpha$ - $\beta$ frame .....                                                                                                    | 30 |

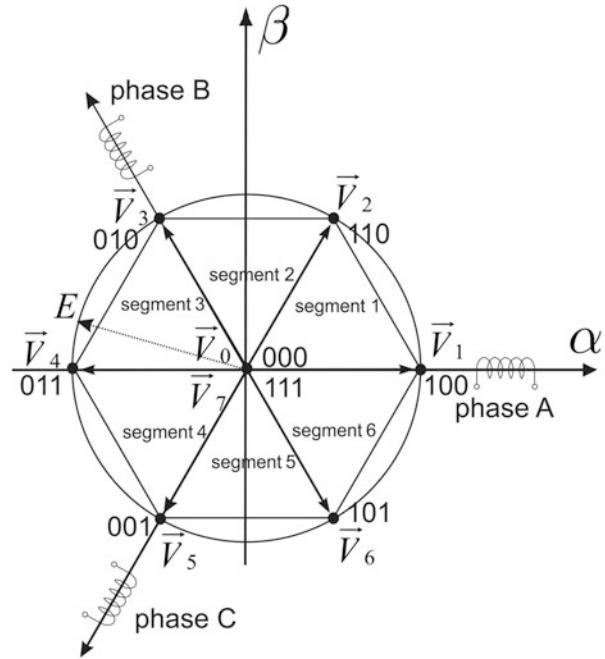

| Fig. 2.15 | Position of eight voltage vectors in orthogonal $\alpha$ - $\beta$ frame .....                                                                                                                                                                      | 31 |

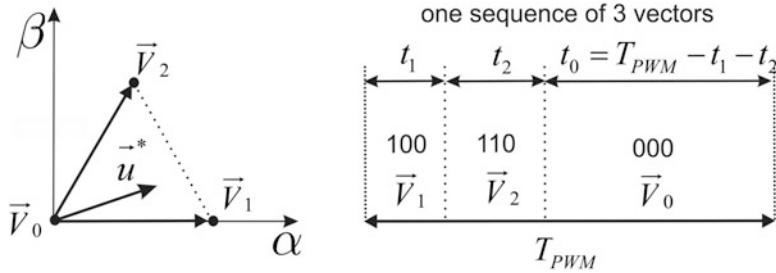

| Fig. 2.16 | The sequence of three voltage vectors .....                                                                                                                                                                                                         | 32 |

| Fig. 2.17 | Counterclockwise sequence of two non-zero vectors and one zero vector make up a "DD" sequence of space vector modulation .....                                                                                                                      | 34 |

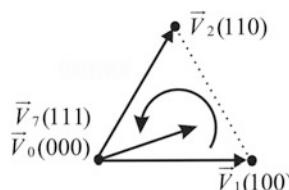

| Fig. 2.18 | DD vector sequences of the space vector modulation and the waveforms of corresponding phase voltages .....                                                                                                                                          | 35 |

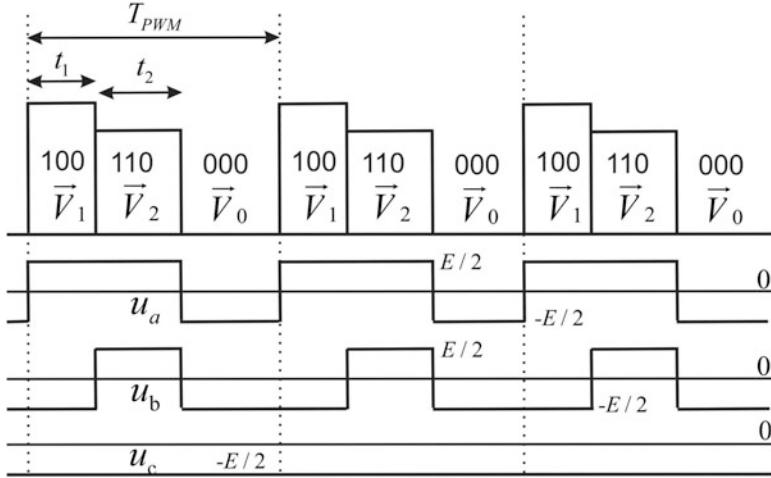

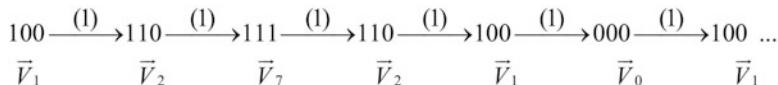

| Fig. 2.19 | The switching pattern with one counterclockwise sequence of voltage vectors followed by clockwise sequence makes up the "DI" sequence of the space vector modulation .....                                                                          | 35 |

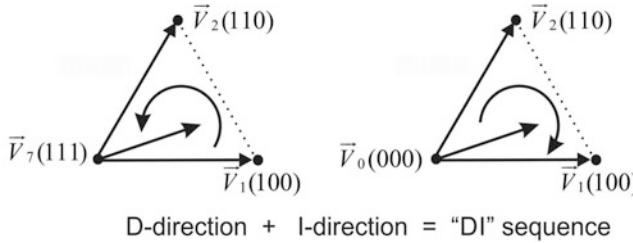

| Fig. 2.20 | DI vector sequences of the space vector modulation and the waveforms of corresponding phase voltages .....                                                                                                                                          | 36 |

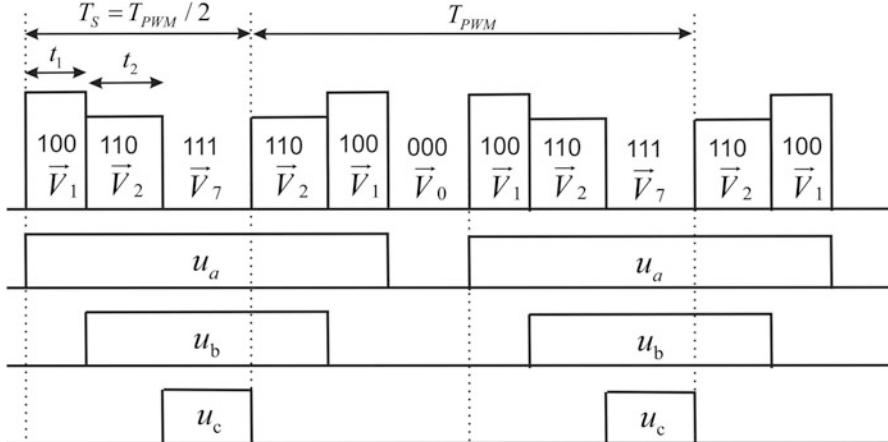

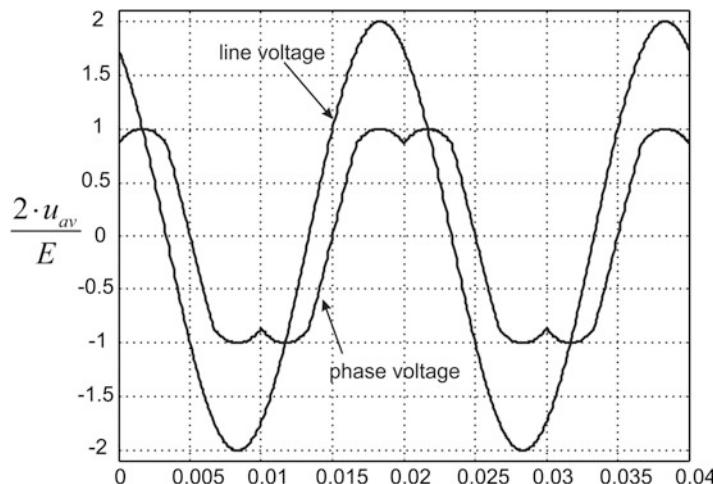

| Fig. 2.21 | The average value of phase and line-to-line voltages obtained with DI vector sequences of the space vector modulation .....                                                                                                                         | 37 |

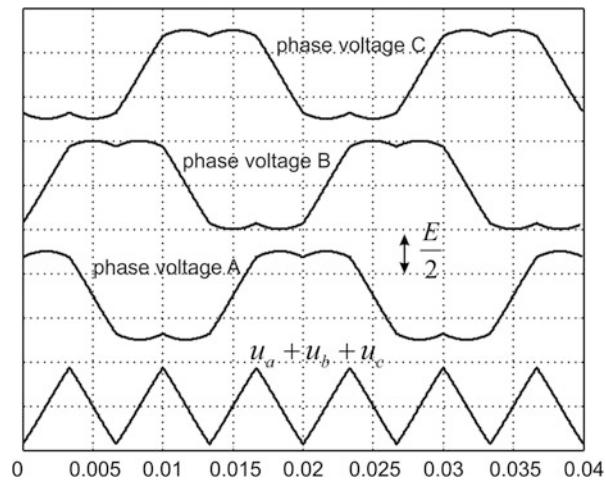

| Fig. 2.22 | The average value of the three-phase voltages and their sum obtained with DI vector sequences of the space vector modulation .....                                                                                                                  | 38 |

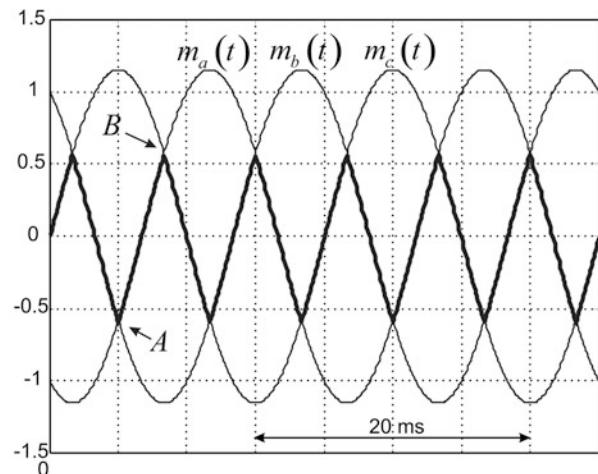

| Fig. 2.23 | Generation of the triangular-shaped correction of (2.19) and Fig. 2.22 from the three sinusoidal modulation signals .....                                                                                                                           | 40 |

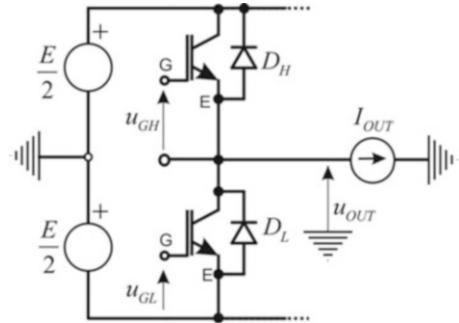

| Fig. 2.24 | With $u_{GH} = u_{GL} = -15$ V, both transistor switches are off, and the output current $I_{OUT} > 0$ closes through the lower diode $D_L$ .....                                                                                                   | 42 |

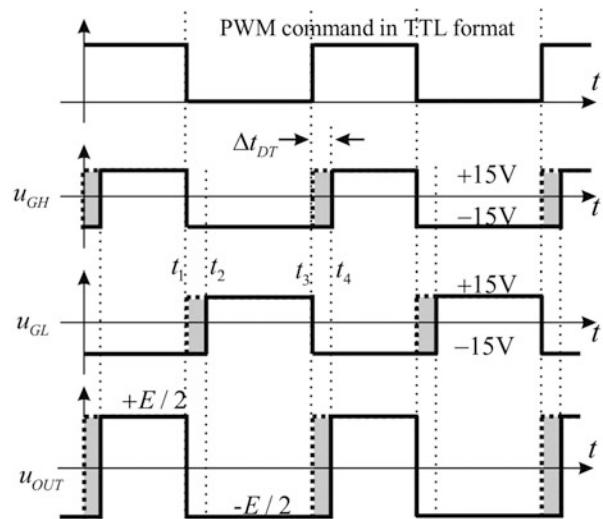

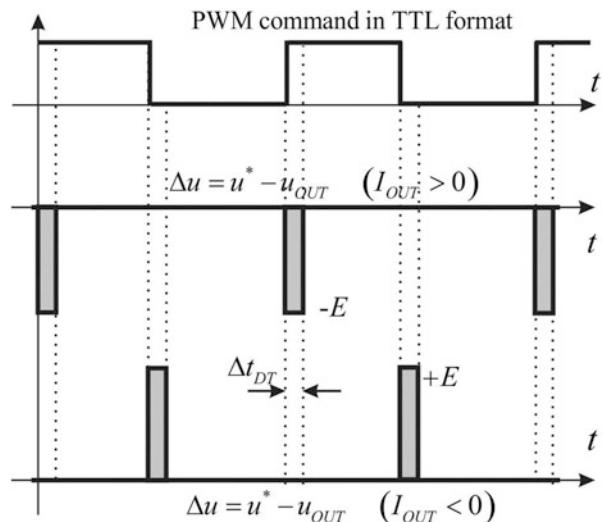

| Fig. 2.25 | The lockout time $\Delta t_{DT}$ is the delay between the instant of turning off the preceding switch ( $t_1, t_3$ ) and turning on the subsequent switch ( $t_2, t_4$ ). The PWM command is obtained from Fig. 2.6 as logic-level TTL signal ..... | 43 |

| Fig. 2.26 | The voltage error caused by the lockout time and its change with the sign of the output current $I_{OUT}$ .....                                                                                                                                     | 44 |

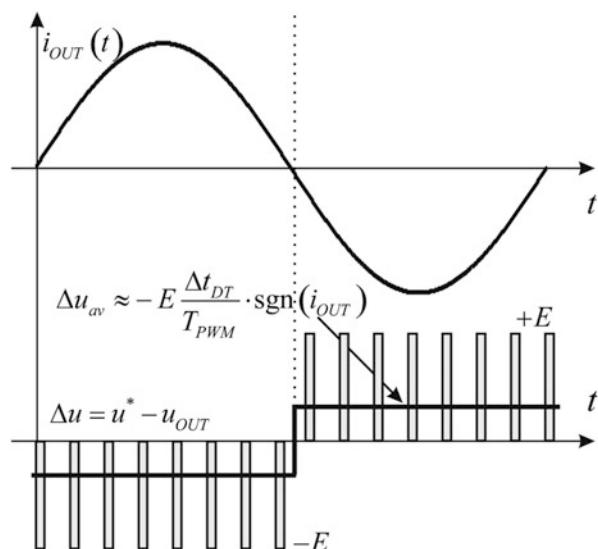

| Fig. 2.27 | The average voltage error and its change with the sign of the output current $I_{OUT}$ .....                                                                                                                                                        | 45 |

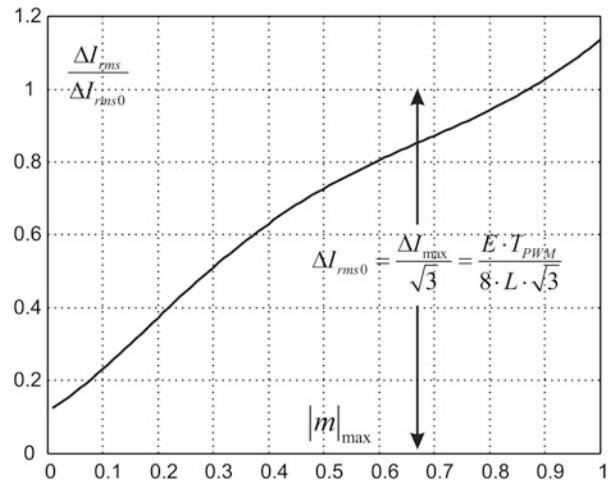

| Fig. 2.28 | The change of the relative rms value of the current ripple with the amplitude of modulation signals .....                                                                                                                                           | 48 |

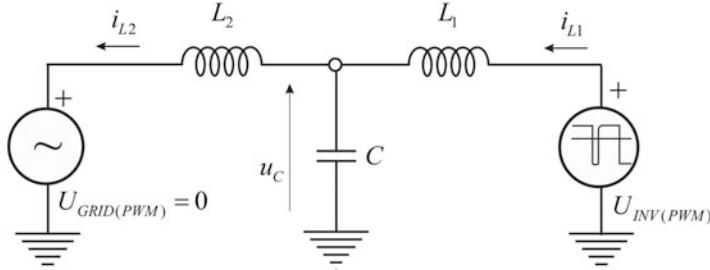

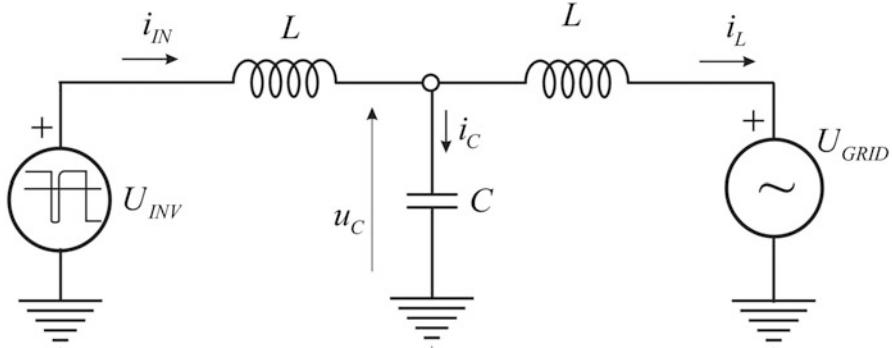

| Fig. 2.29 | LCL filter that suppresses the injection of PWM-related ripple from the grid-side inverter (on the right) into the ac grid (on the left) .....                                                                                                      | 50 |

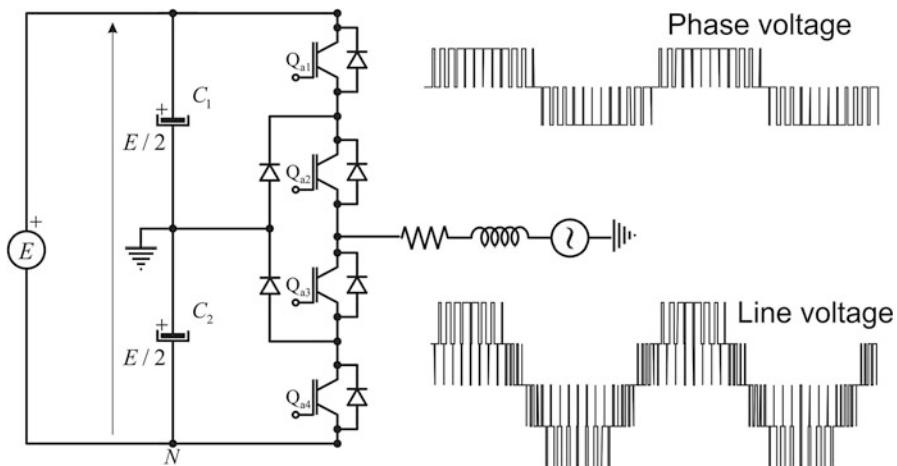

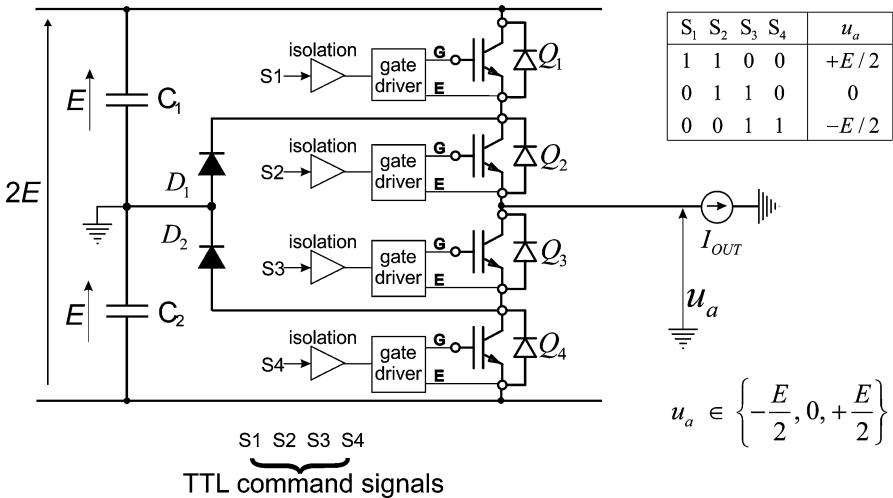

| Fig. 2.30 | One phase of the three-level inverter. It takes four power transistors, four TTL commands, and six diodes to generate $u_a(t)$ with three discrete levels .....                                                                                     | 55 |

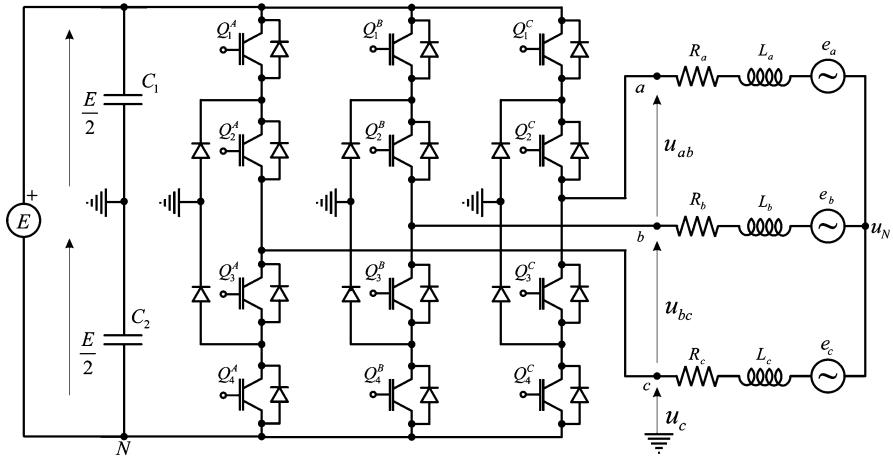

| Fig. 2.31 | Three-phase three-level inverter connected to the three-phase load .....                                                                                                                                                                            | 56 |

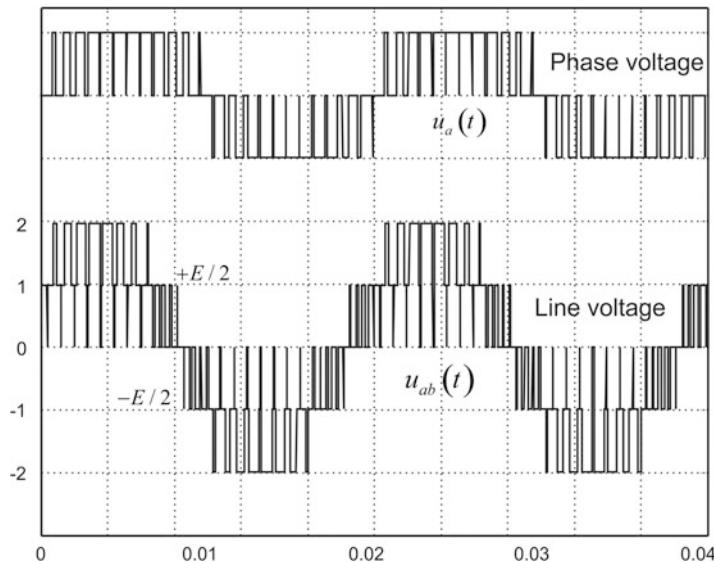

| Fig. 2.32 | The phase voltage and the line-to-line voltage at the output of the three-phase three-level inverter. The waveforms are obtained with modified triangular carrier-based modulation of Fig. 2.9 .....                                                | 56 |

|           |                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

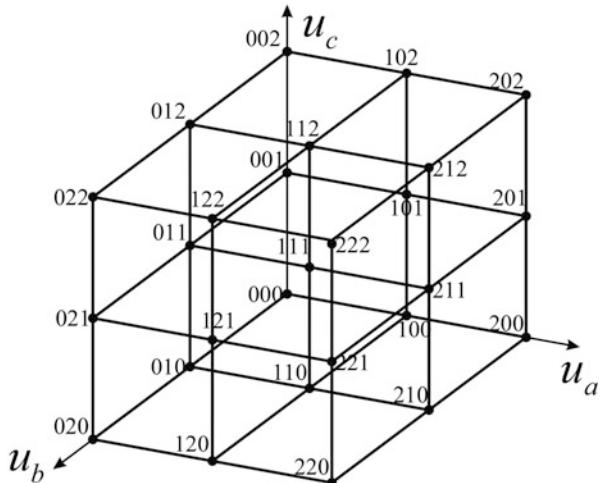

| Fig. 2.33 | The switching states of the three-level three-phase inverter. Each switching state is described by a three-digit code. The digits 0, 1, and 2 correspond to the output voltages $-E/2$ , 0, and $+E/2$ . The first digit in each code corresponds to the phase a, the second to the phase b, and the third to the phase c .....                                                                 | 58 |

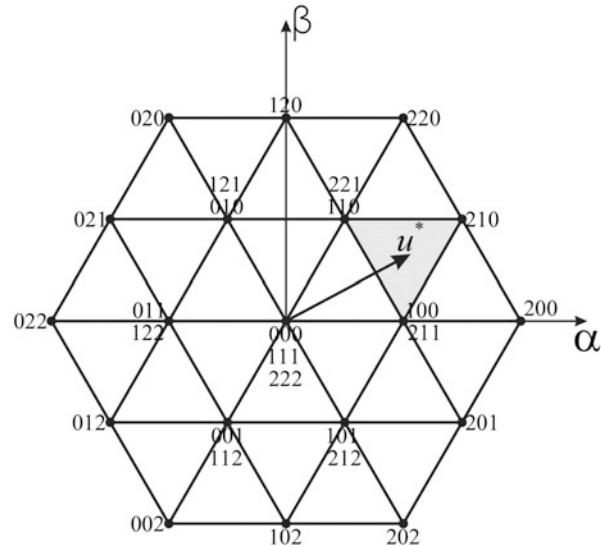

| Fig. 2.34 | The output voltage vectors of the three-phase three-level inverter in $\alpha$ - $\beta$ coordinate frame. The reference voltage vector resides within the shaded triangle .....                                                                                                                                                                                                                | 59 |

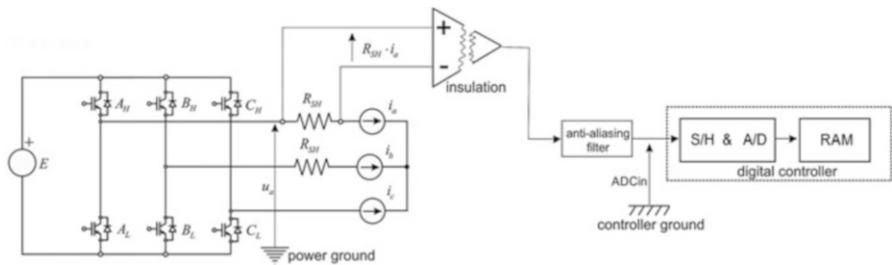

| Fig. 3.1  | Current measurement system with shunt resistors $R_{SH}$ . Dangerous power circuit voltages have to be isolated from the digital controller. Thus, the analogue signal $R_{SH}i_a$ has to pass through isolation amplifiers .....                                                                                                                                                               | 62 |

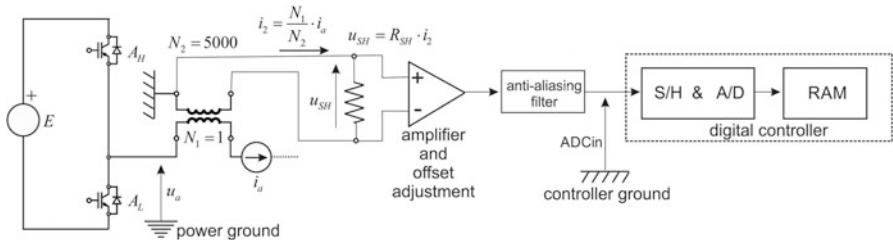

| Fig. 3.2  | Current measurement system with the current transformer. The primary and secondary circuits are isolated. The secondary current $i_2$ is $N_2/N_1$ times lower than the primary current $i_a$ , and it provides the analogue signal $R_{SH}i_a$ proportional to the current being measured .....                                                                                                | 64 |

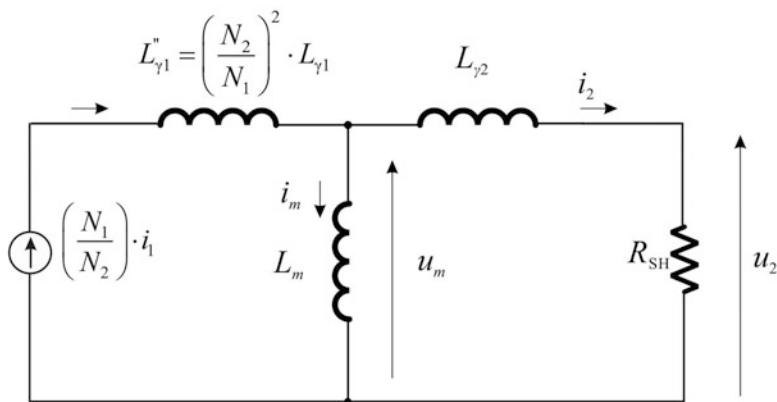

| Fig. 3.3  | Simplified equivalent circuit of the current transformer .....                                                                                                                                                                                                                                                                                                                                  | 64 |

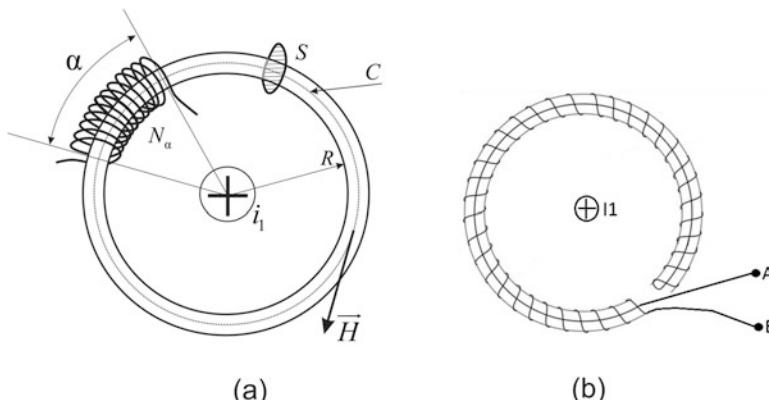

| Fig. 3.4  | Rogowski coil: (a) The cross section $S$ of the coil is constant along the coil length. The number of turns per unit length is also constant. (b) Upon reaching the end of the coil, the wire returns to the beginning through the center of the coil. Thus, both terminals (A and B) are at the same end of the coil. In use, the coil envelops the current-carrying conductor ( $i_1$ ) ..... | 66 |

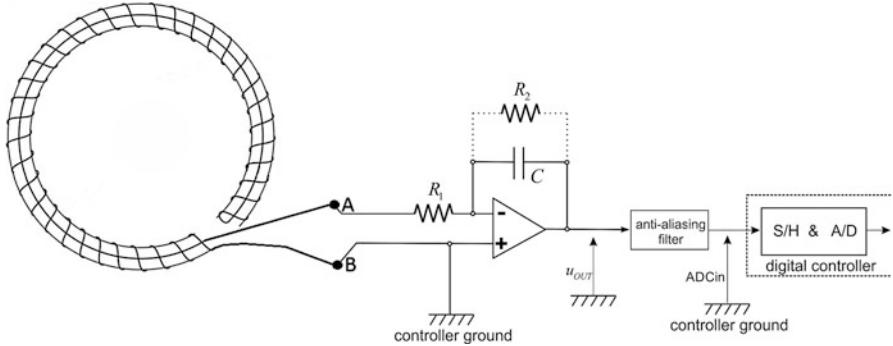

| Fig. 3.5  | Integration of the voltage detected by the Rogowski coil. Additional resistance $R_2$ is required in order to suppress the offset .....                                                                                                                                                                                                                                                         | 68 |

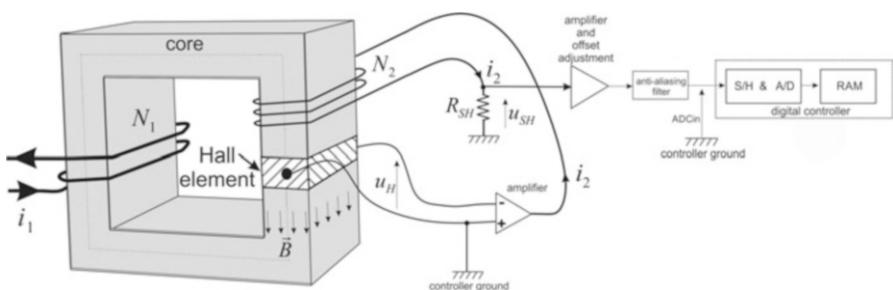

| Fig. 3.6  | Current-sensing transformer with Hall effect sensor placed in the air gap of the magnetic core .....                                                                                                                                                                                                                                                                                            | 69 |

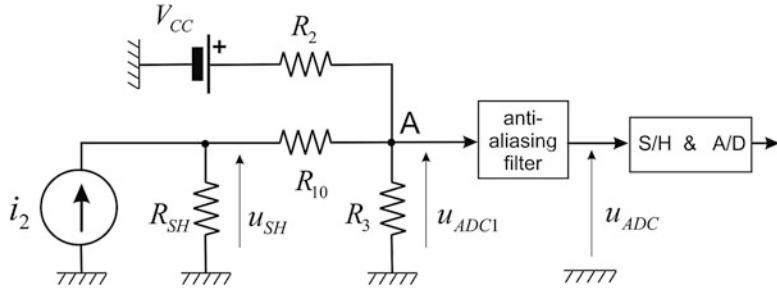

| Fig. 3.7  | Passive circuit for attenuation and offset correction of the feedback signals obtained from the current sensor .....                                                                                                                                                                                                                                                                            | 72 |

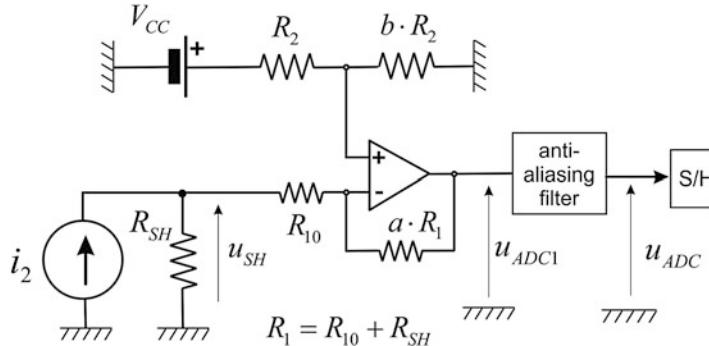

| Fig. 3.8  | Active interface circuit for the gain and offset correction of the feedback signals obtained from the current sensor .....                                                                                                                                                                                                                                                                      | 73 |

| Fig. 3.9  | Amplitude quantization in A/D converter .....                                                                                                                                                                                                                                                                                                                                                   | 75 |

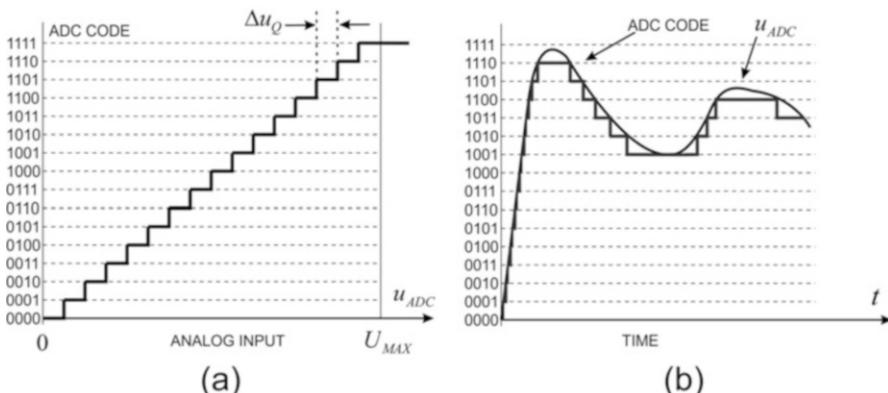

| Fig. 3.10 | Time-discrete nature of digital controllers .....                                                                                                                                                                                                                                                                                                                                               | 77 |

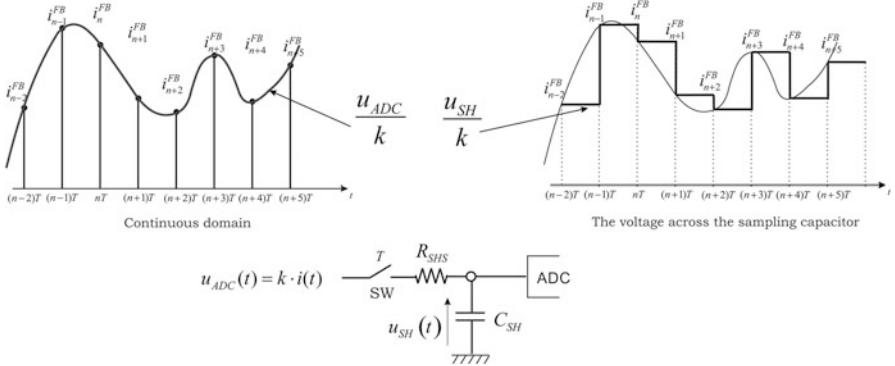

| Fig. 3.11 | Sampling circuit and the voltage across the sampling capacitor .....                                                                                                                                                                                                                                                                                                                            | 78 |

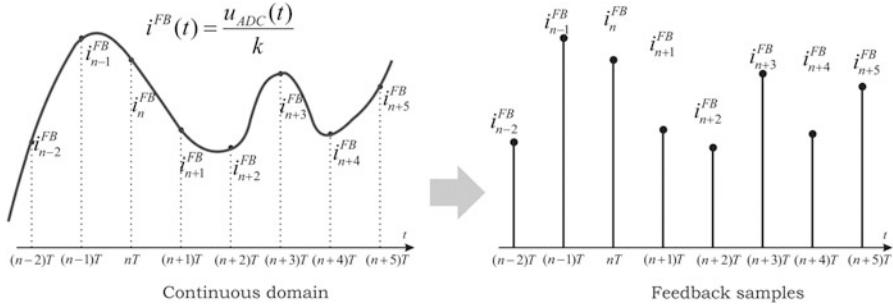

| Fig. 3.12 | Conversion of the analogue feedback signal into the train of samples .....                                                                                                                                                                                                                                                                                                                      | 79 |

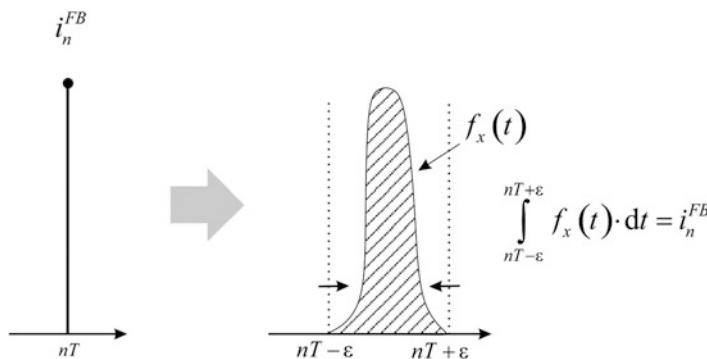

| Fig. 3.13 | Mathematical representation of the sample acquired at instant $nT$ .....                                                                                                                                                                                                                                                                                                                        | 79 |

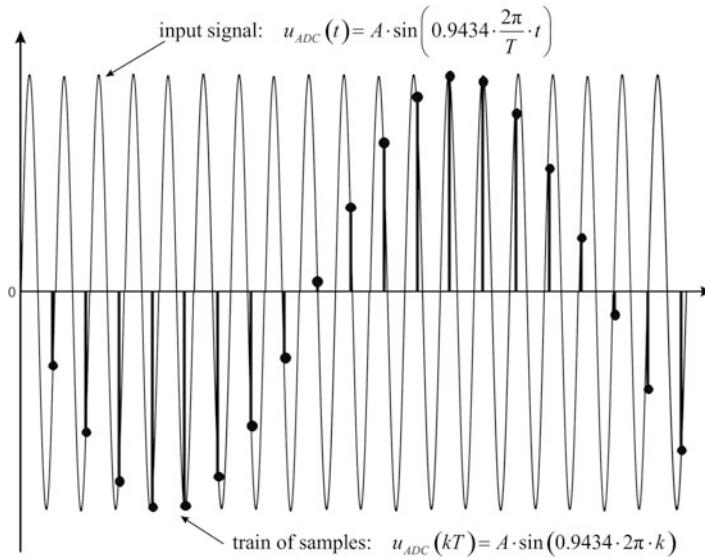

| Fig. 3.14 | A low-frequency alias caused by erroneous sampling .....                                                                                                                                                                                                                                                                                                                                        | 80 |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

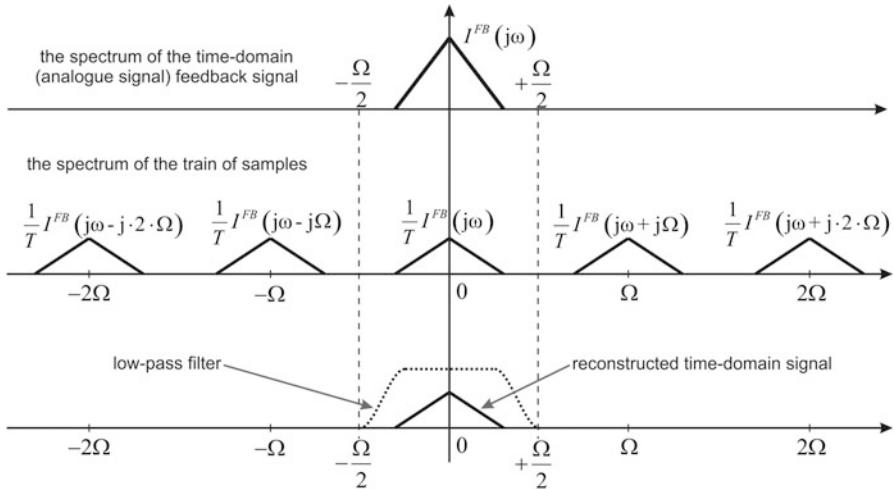

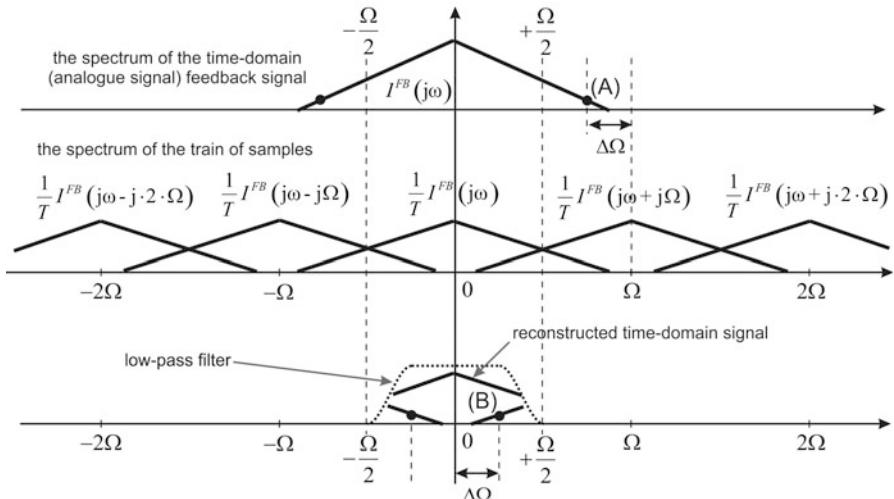

| Fig. 3.15 | The spectrum of the analogue signal $i^{\text{FB}}(t)$ (the upper trace) and the spectrum of the train of samples $i_D^{\text{FB}}(t)$ (in the middle). The lower trace corresponds to the spectrum obtained by using a low-pass filter to reconstruct the time-domain signal from the sampled data .....                                                                                                                                   | 84 |

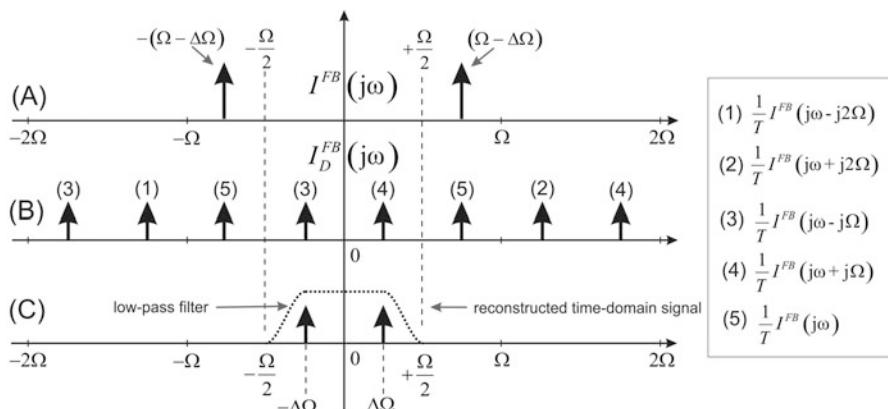

| Fig. 3.16 | The spectrum $I^{\text{FB}}(\omega)$ of the analogue signal $i^{\text{FB}}(t)$ (the upper trace), the spectrum $I_D^{\text{FB}}(\omega)$ of the train of samples $i_D^{\text{FB}}(t)$ (the middle), and the reconstructed spectrum (the lower trace) obtained with $I^{\text{FB}}(\omega)$ which extends beyond $\Omega/2$ .....                                                                                                            | 84 |

| Fig. 3.17 | Illustration of the case where the high-frequency component of the original signal causes a low-frequency alias within the reconstructed signal .....                                                                                                                                                                                                                                                                                       | 85 |

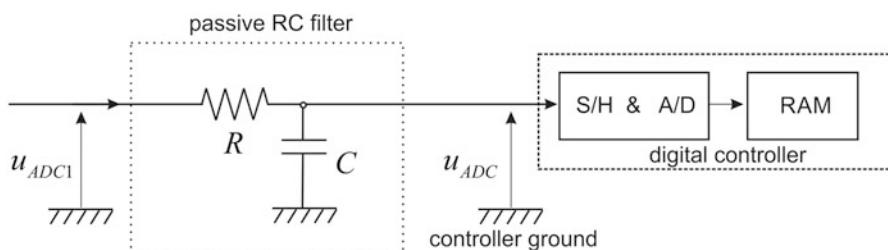

| Fig. 3.18 | Passive anti-aliasing R-C filter .....                                                                                                                                                                                                                                                                                                                                                                                                      | 85 |

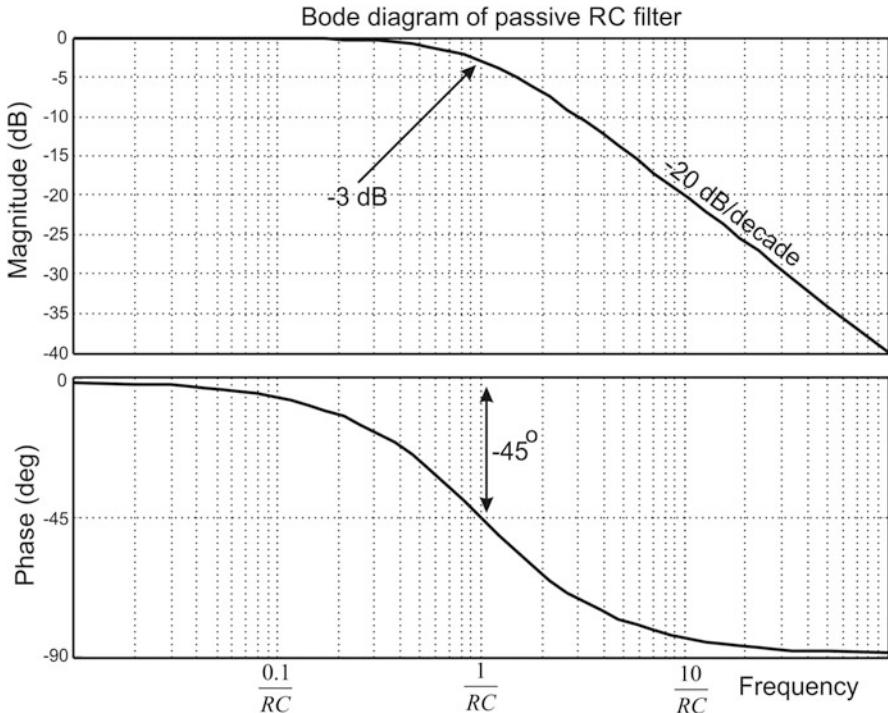

| Fig. 3.19 | Frequency response of the passive anti-aliasing R-C filter .....                                                                                                                                                                                                                                                                                                                                                                            | 88 |

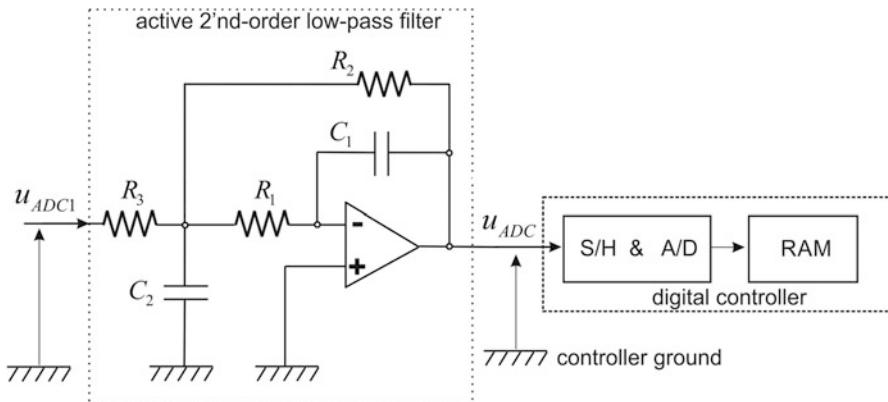

| Fig. 3.20 | Second-order anti-aliasing filter .....                                                                                                                                                                                                                                                                                                                                                                                                     | 90 |

| Fig. 3.21 | Center-pulse sampling with simplified waveform of the current ripple, obtained with the single-phase representation of the load and with the assumption that the series resistance is negligible .....                                                                                                                                                                                                                                      | 91 |

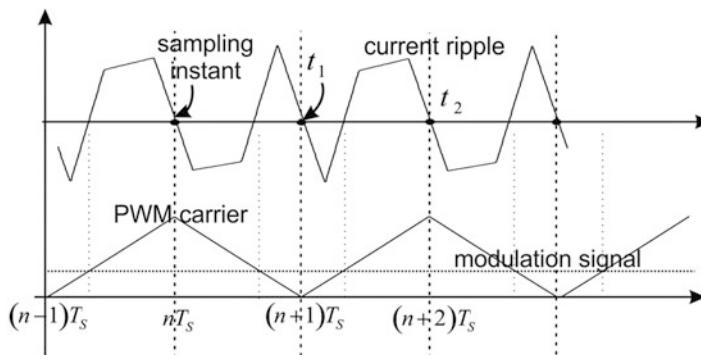

| Fig. 3.22 | Center-pulse sampling with simplified waveform of the current ripple, obtained with the three-phase representation of the load and with $R = 0$ .....                                                                                                                                                                                                                                                                                       | 91 |

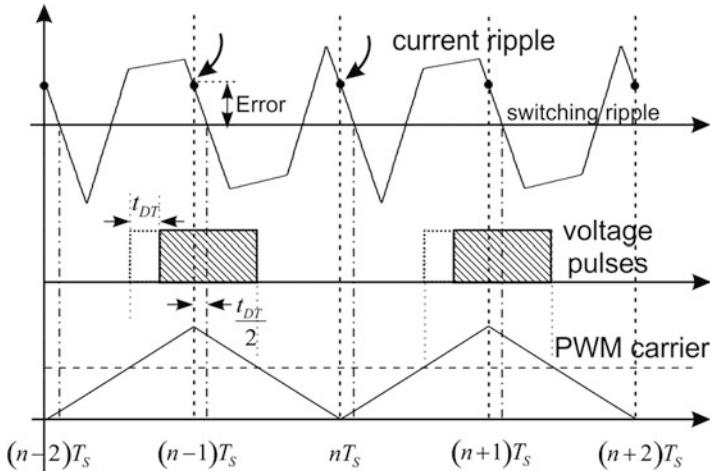

| Fig. 3.23 | Center-pulse sampling with simplified waveform of the current ripple, obtained with the three-phase representation of the load and with $R = 0$ , and with the lockout time $t_{DT}$ .....                                                                                                                                                                                                                                                  | 92 |

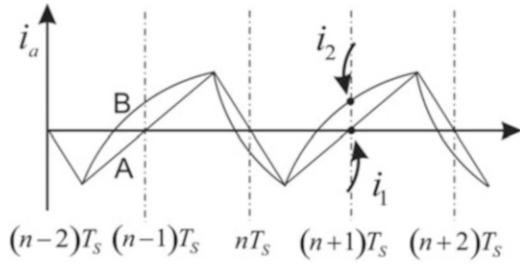

| Fig. 3.24 | The impact of the load resistance on the center-pulse sampling. Simplified waveform of the current ripple is obtained with single-phase representation of the load. The waveform A corresponds to $R = 0$ , while the waveform B corresponds to $R > 0$ .....                                                                                                                                                                               | 93 |

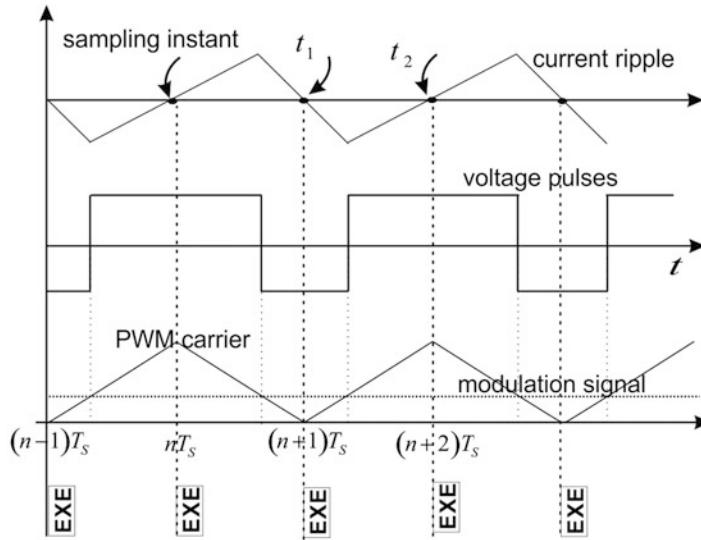

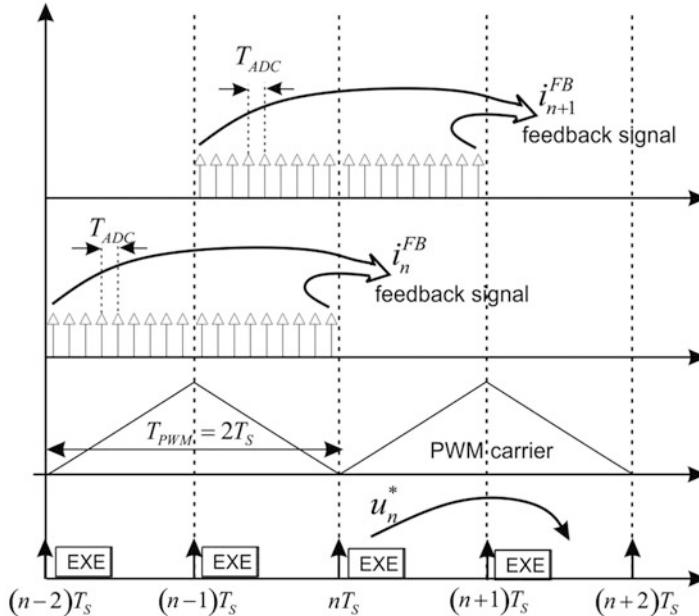

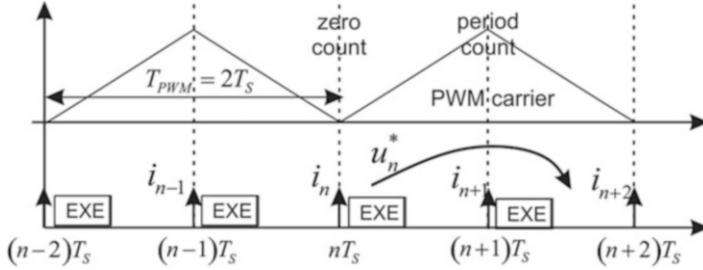

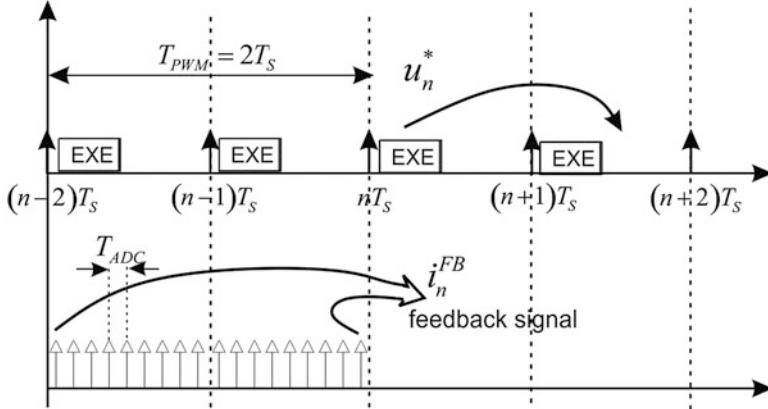

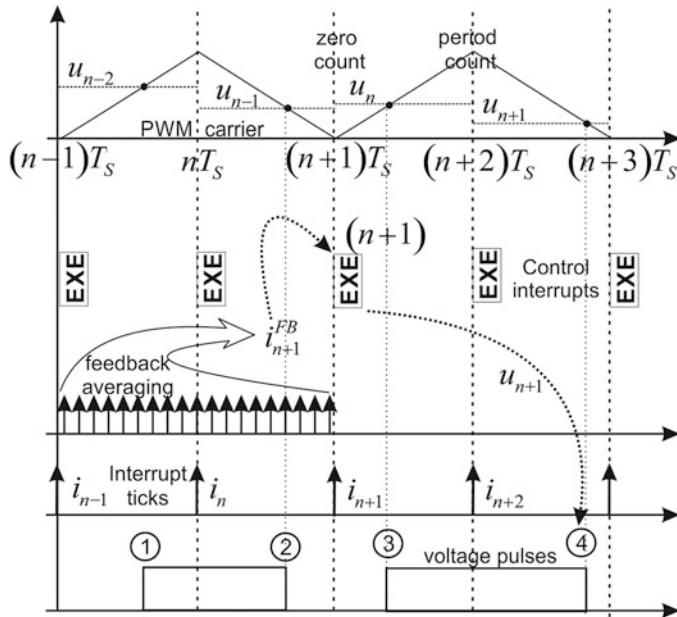

| Fig. 3.25 | The oversampling scheme which collects $N_{\text{OV}} = T_{\text{PWM}}/T_{\text{ADC}}$ samples in each PWM period and calculates the feedback signal $i^{\text{FB}}$ as an average of the samples. Execution of the control interrupts is denoted by EXE. In interrupt session triggered at $nT_S$ , the feedback signal $i_n^{\text{FB}}$ is calculated as the average value of $i_a(t)$ over the interval $[(n - 2)T_S \dots nT_S]$ ..... | 95 |

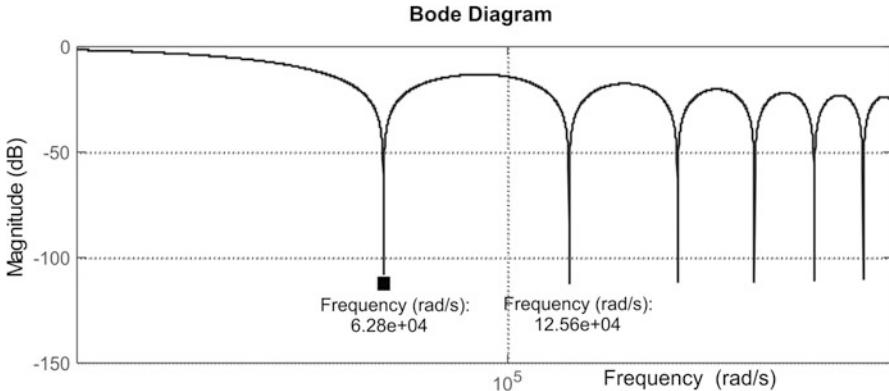

| Fig. 3.26 | The frequency characteristic of the one-period averaging filter in (3.31). The filter $W_{\text{FIR}}(z)$ has an infinite attenuation at frequencies $n \cdot f_{\text{PWM}}$ . In the plot, the attenuation appears limited to $-110$ dB due to the finite wordlength used in Bode plot calculations .....                                                                                                                                 | 97 |

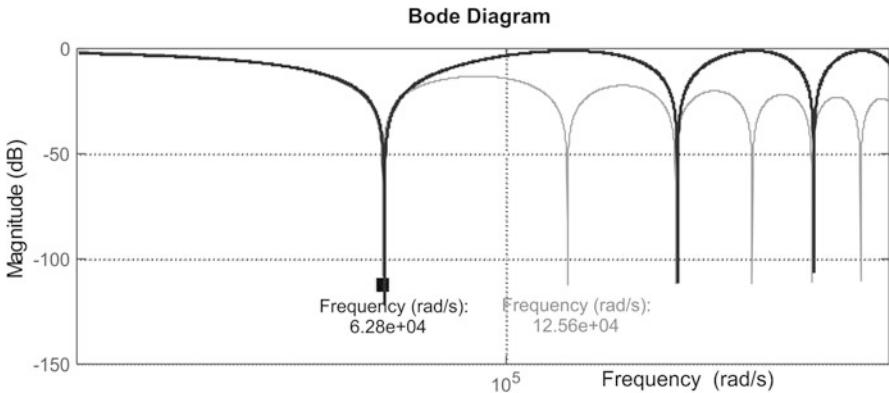

| Fig. 3.27 | The frequency characteristic of the pulse transfer function of (3.32). In the frequency range below one half of the sampling frequency, the frequency characteristic corresponds to the one in Fig. 3.26. The differences are observed beyond one half of the sampling frequency .....                                                                                                                                                      | 98 |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 3.28 | LCL filter with two identical inductances and one parallel capacitor. For the stable operation, it is necessary to introduce the control action proportional to the capacitor current .....                                                                                                                                                                                                                                                                                                                                                   | 99  |

| Fig. 4.1  | In both grid-side inverters and ac drives, the three-phase inverter is connected to the three-phase load which comprises the series impedance and back-electromotive force .....                                                                                                                                                                                                                                                                                                                                                              | 104 |

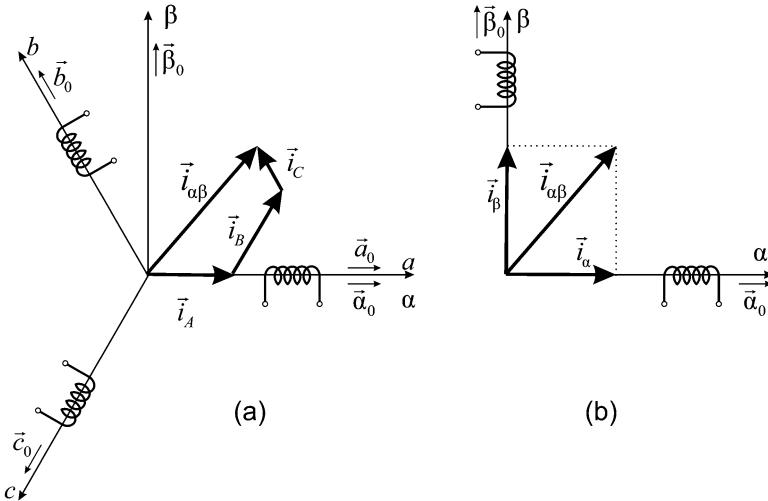

| Fig. 4.2  | (a) The phases $a$ , $b$ , and $c$ are given the unit vectors $a_0$ , $b_0$ , and $c_0$ , spatially displaced by $2\pi/3$ . Each of the currents $i_A$ , $i_B$ , and $i_C$ is represented by the corresponding vector. The vector $i_{\alpha\beta}$ is obtained by summing the three current vectors. (b) The vector $i_{\alpha\beta}$ can be represented in $\alpha$ - $\beta$ frame, in terms of the components $i_\alpha$ and $i_\beta$ , which are the projections of the vector $i_{\alpha\beta}$ on the axes $\alpha$ and $\beta$ ..... | 107 |

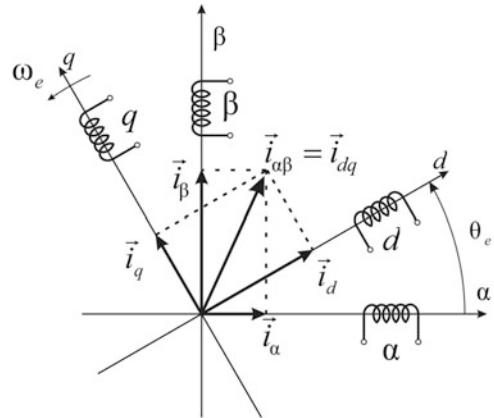

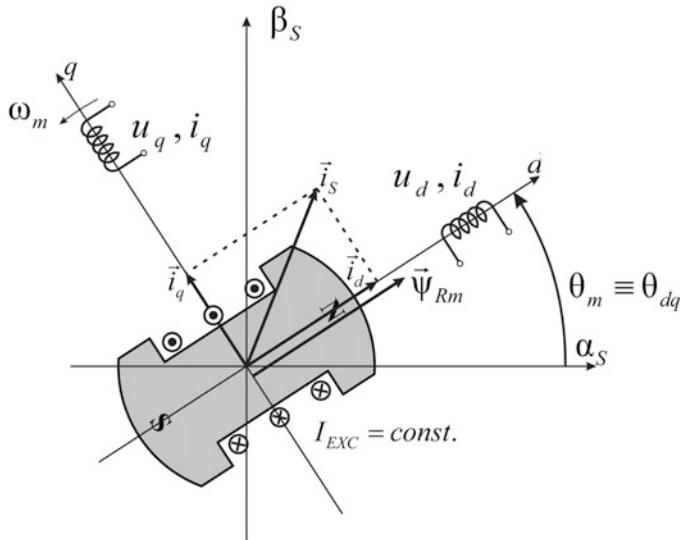

| Fig. 4.3  | Transformation of the output current from the stationary, $\alpha$ - $\beta$ coordinate frame into the synchronously revolving d-q frame ....                                                                                                                                                                                                                                                                                                                                                                                                 | 109 |

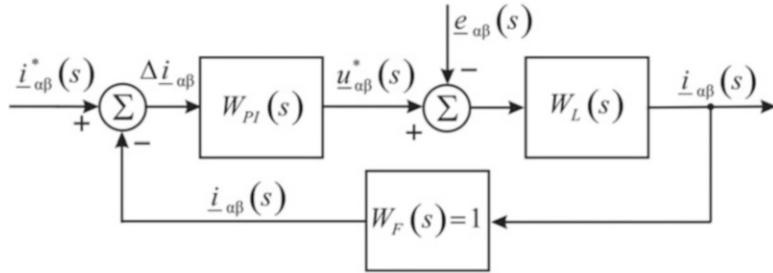

| Fig. 4.4  | Block diagram of the stationary-frame PI controller .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 111 |

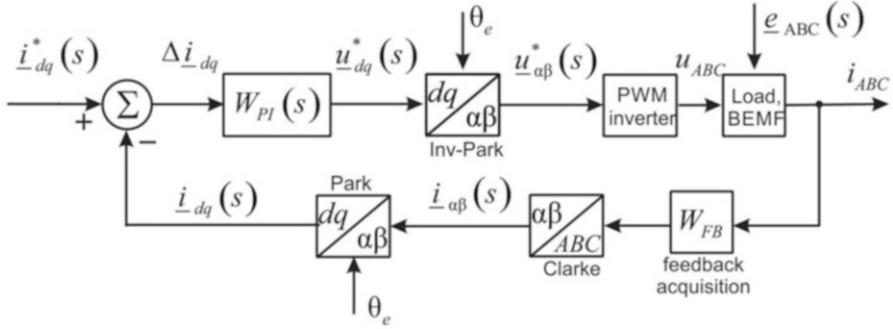

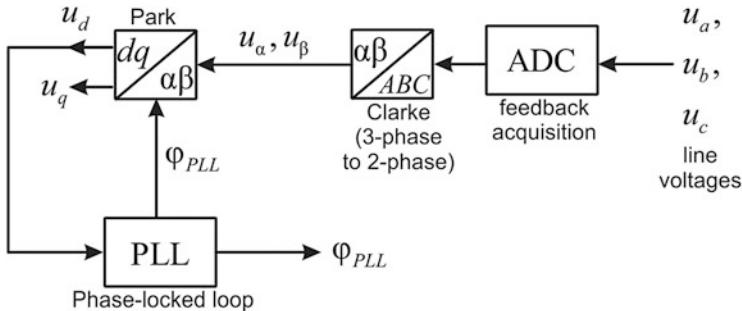

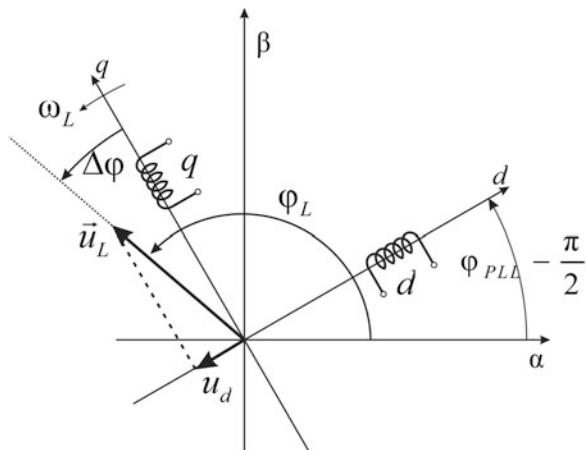

| Fig. 4.5  | Coordinate transformations of the synchronous d-q frame PI controller .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 113 |

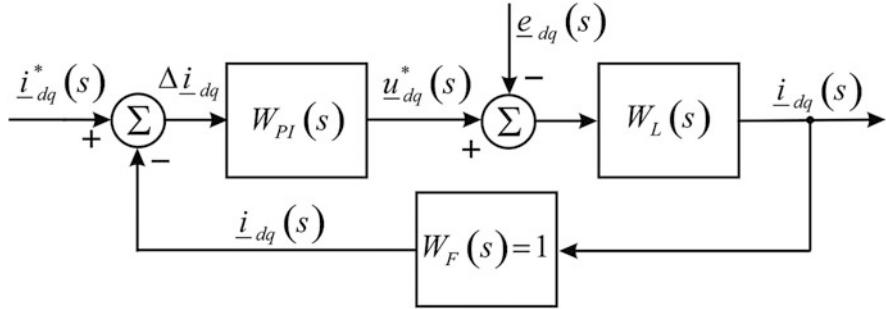

| Fig. 4.6  | Block diagram of the synchronous d-q frame PI controller .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 114 |

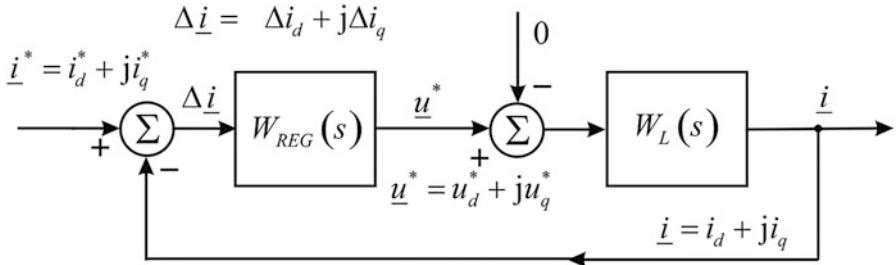

| Fig. 4.7  | In application of internal model control concept, the controller $W_{\text{REG}}$ comprises the inverted dynamics of the object $W_L$ .....                                                                                                                                                                                                                                                                                                                                                                                                   | 116 |

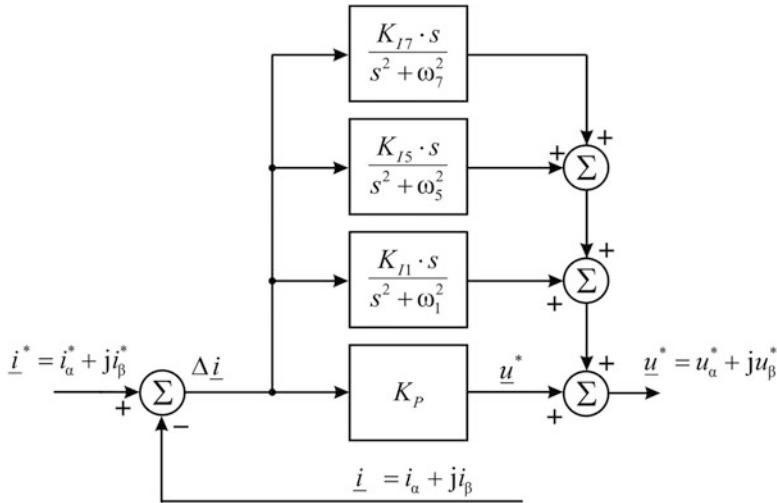

| Fig. 4.8  | The resonant controller tuned for the fundamental frequency and for the fifth and seventh harmonic .....                                                                                                                                                                                                                                                                                                                                                                                                                                      | 119 |

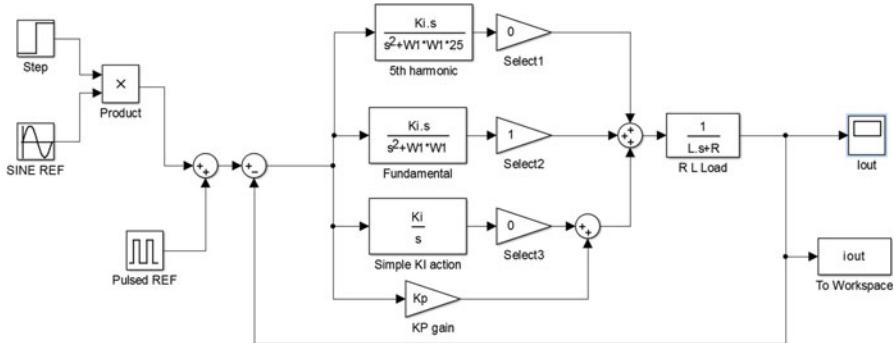

| Fig. 4.9  | Simulation of the resonant current controller with resonant integrators adjusted for the fundamental and for the fifth harmonic .....                                                                                                                                                                                                                                                                                                                                                                                                         | 120 |

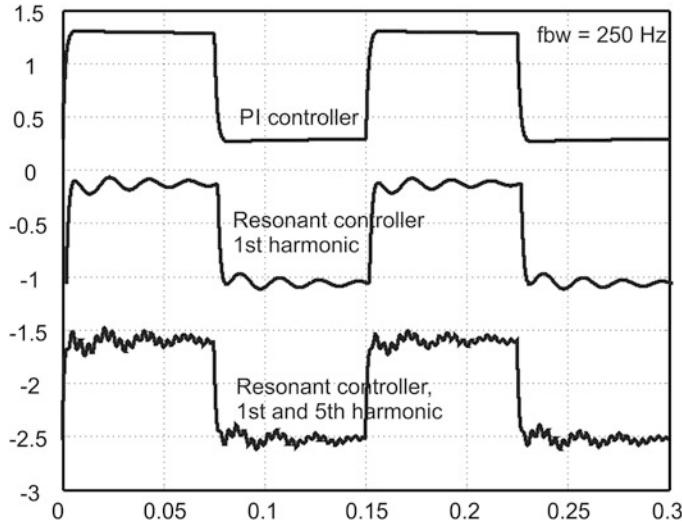

| Fig. 4.10 | Step response of the PI controller, resonant current controller tuned for the line-frequency fundamental component, and resonant controller tuned for the fundamental and the fifth harmonic .....                                                                                                                                                                                                                                                                                                                                            | 121 |

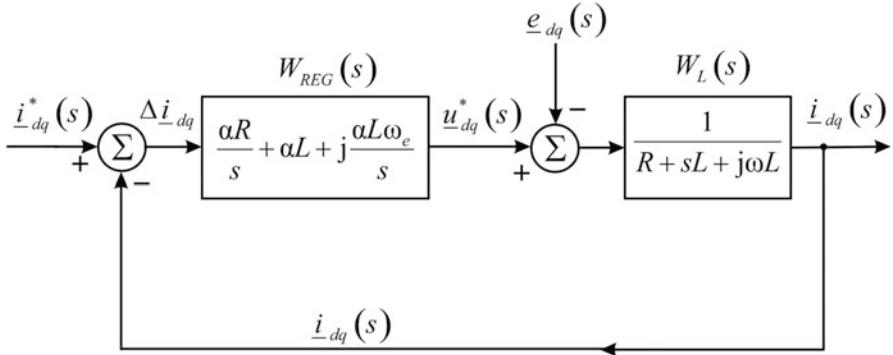

| Fig. 4.11 | Decoupled PI controller in d-q coordinate frame .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 122 |

| Fig. 4.12 | The amplitude characteristic of the output admittance in $\alpha$ - $\beta$ frame .....                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 123 |

| Fig. 4.13 | The implementation of the active resistance feedback .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 124 |

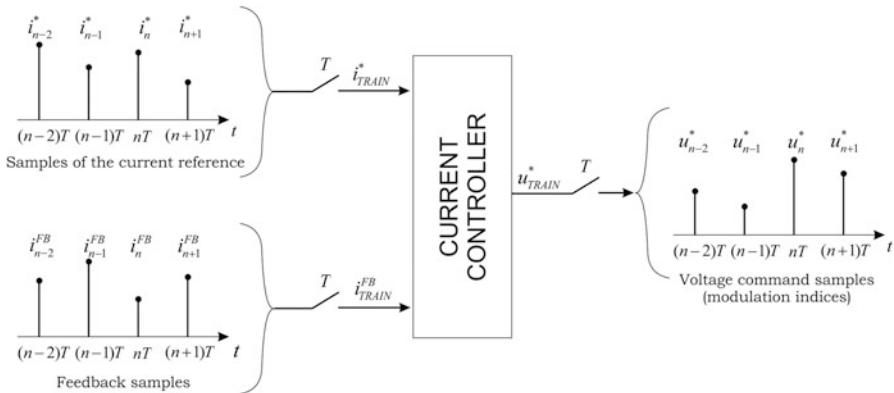

| Fig. 5.1  | Scheduling of the current controller tasks .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 131 |

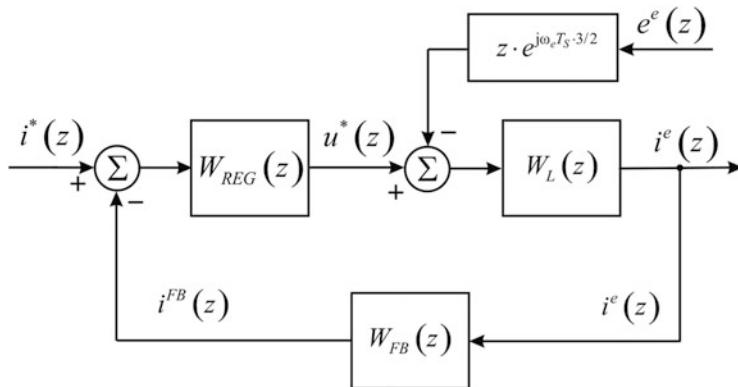

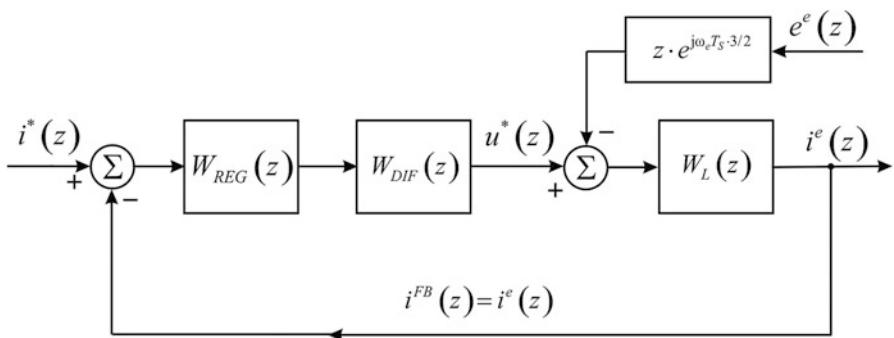

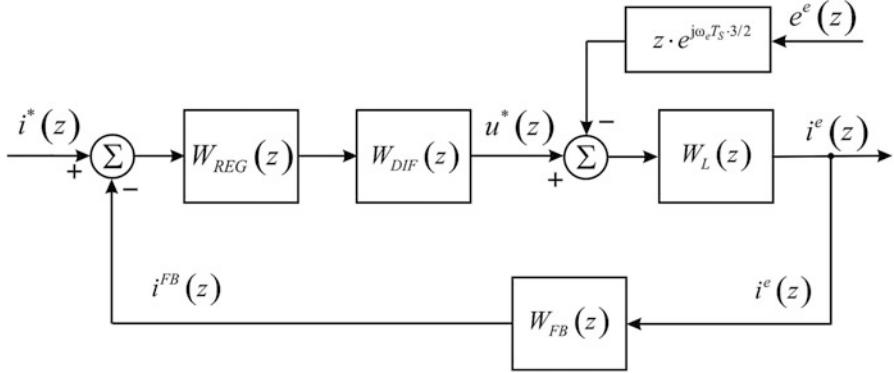

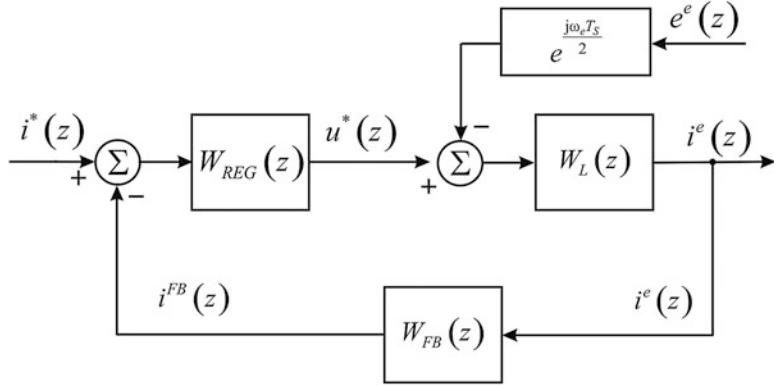

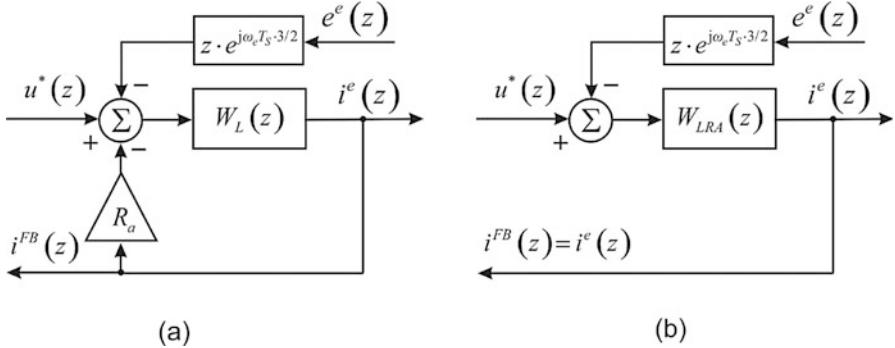

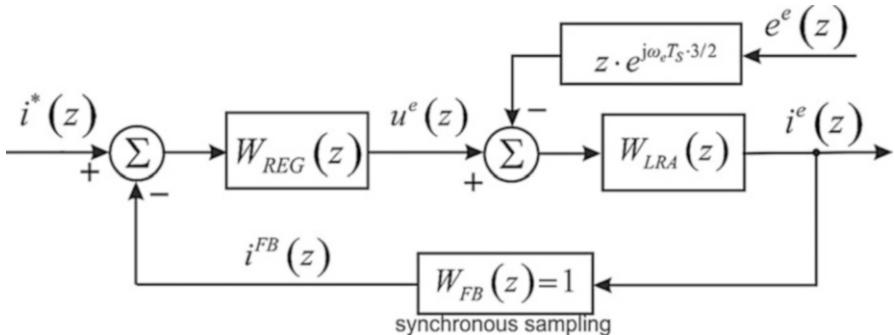

| Fig. 5.2  | The block diagram of the d-q frame current controller which uses the synchronous sampling scheme .....                                                                                                                                                                                                                                                                                                                                                                                                                                        | 133 |

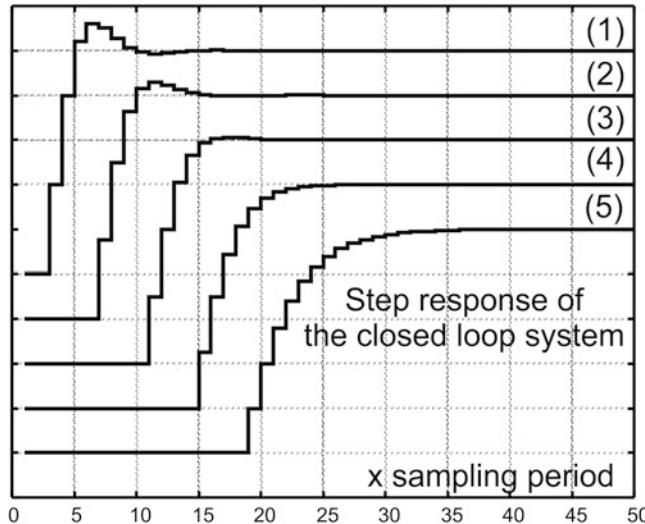

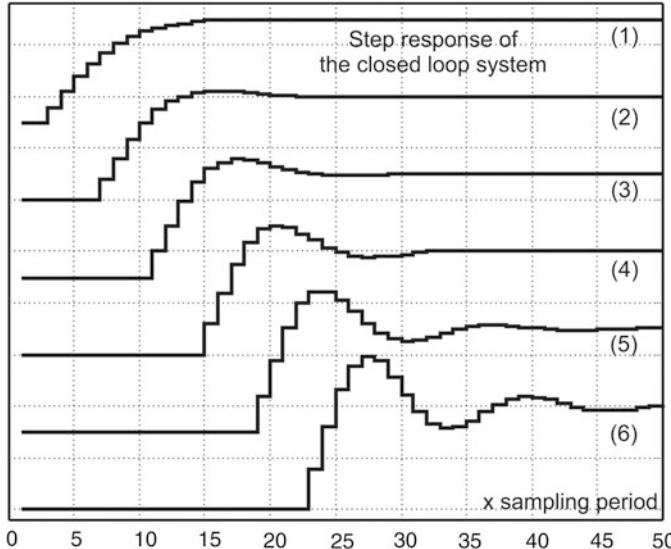

| Fig. 5.3  | Step response of the closed-loop system of (5.14) obtained with the gain $\alpha_D$ equal to 0.4 (trace 1), 0.35 (trace 2), 0.3 (trace 3), 0.25 (trace 4), and 0.2 (trace 5) .....                                                                                                                                                                                                                                                                                                                                                            | 135 |

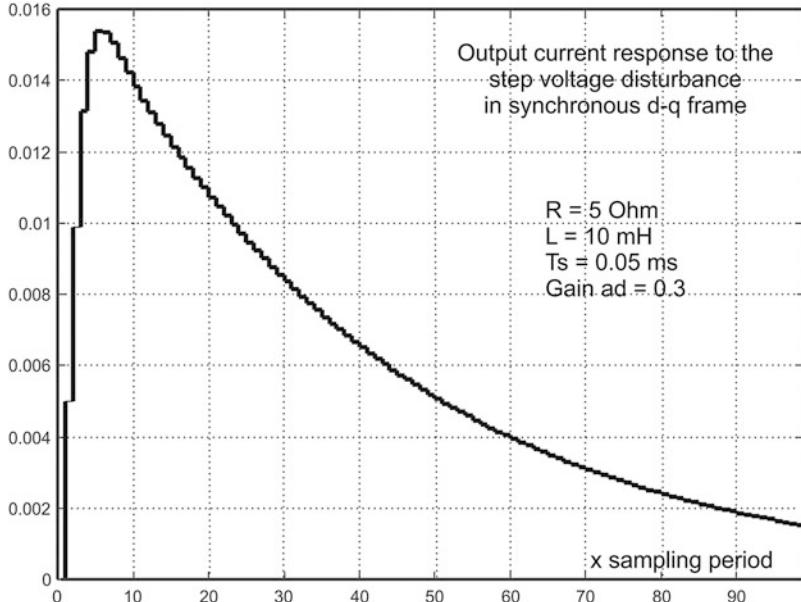

| Fig. 5.4  | Response of the output current to the voltage step disturbance. The response is obtained from (5.18) for the parameters $R$ , $L$ , $T_S$ , and $\alpha_D$ that are listed within the figure .....                                                                                                                                                                                                                                                                                                                                            | 138 |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

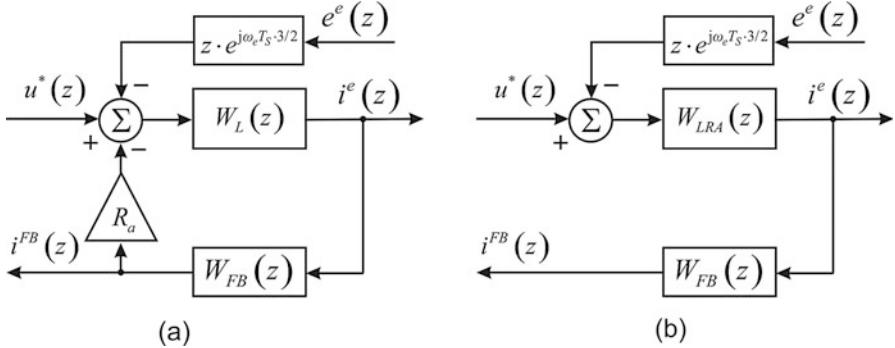

| Fig. 5.5  | Block diagram of the current controller with one-PWM-period averaging oversampling-based feedback .....                                                                                                                                                                                                                                                                                                                                                                                                          | 139 |

| Fig. 5.6  | Time schedule of the feedback acquisition, computation, and pulse width modulation of the digital current controller with one-PWM-period averaging in the feedback path .....                                                                                                                                                                                                                                                                                                                                    | 140 |

| Fig. 5.7  | Step response of the closed-loop system of (5.25) obtained with the gain $\alpha_D$ equal to 0.15 (trace 1), 0.2 (trace 2), 0.25 (trace 3), 0.3 (trace 4), 0.35 (trace 5), and 0.4 (trace 6). ....                                                                                                                                                                                                                                                                                                               | 142 |

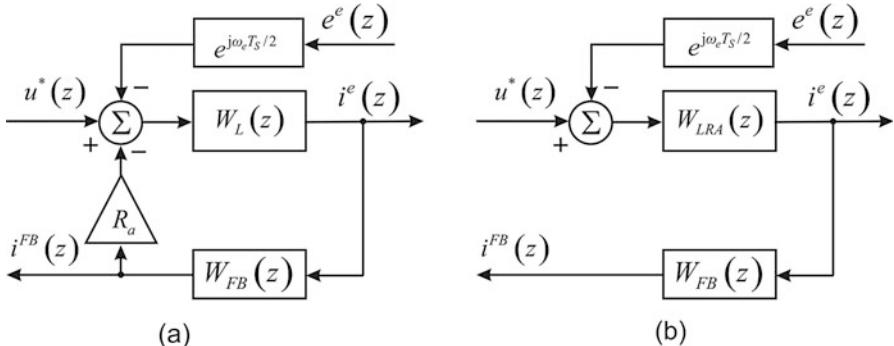

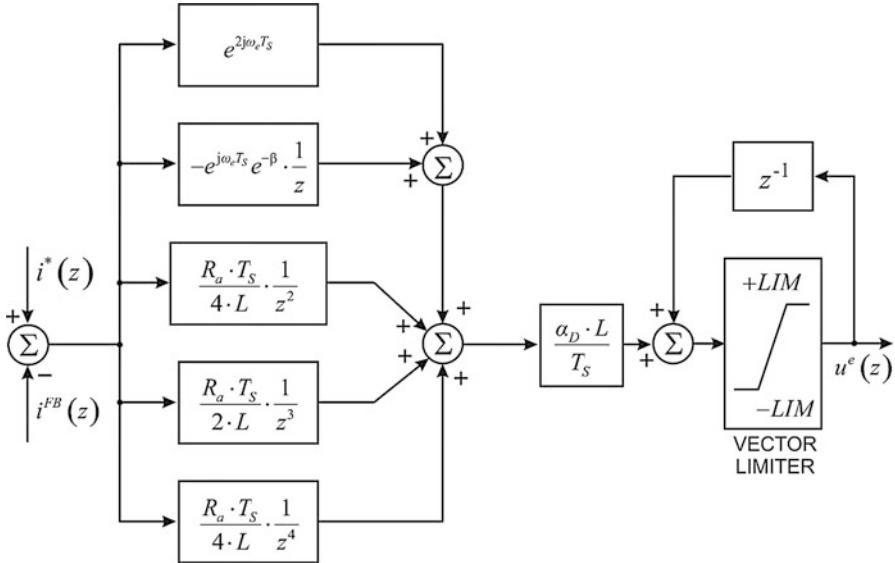

| Fig. 5.8  | IMC-based digital current controller with synchronous, center-pulse sampling and with the differential series compensator .....                                                                                                                                                                                                                                                                                                                                                                                  | 144 |

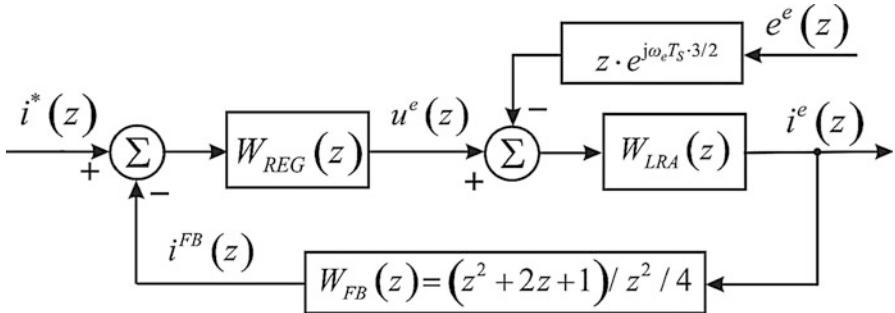

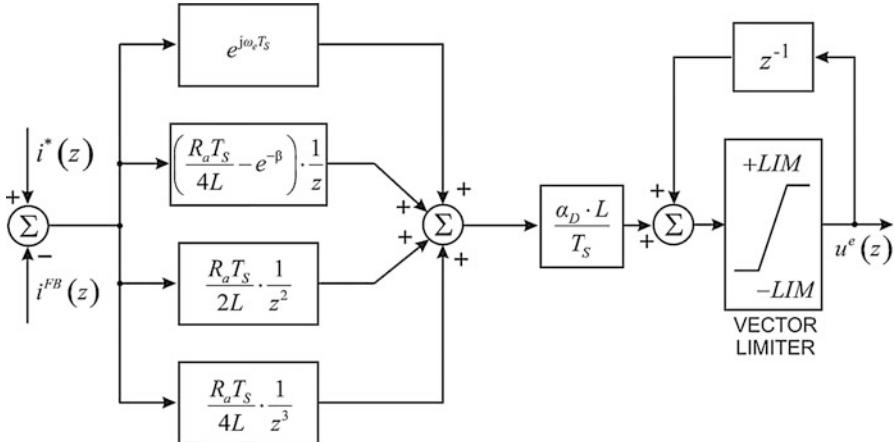

| Fig. 5.9  | IMC-based digital current controller with one-PWM-period feedback averaging and with the differential series compensator .....                                                                                                                                                                                                                                                                                                                                                                                   | 147 |

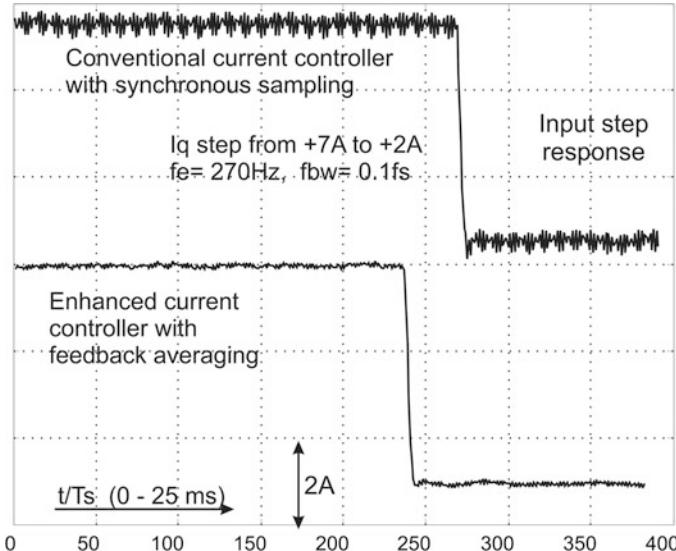

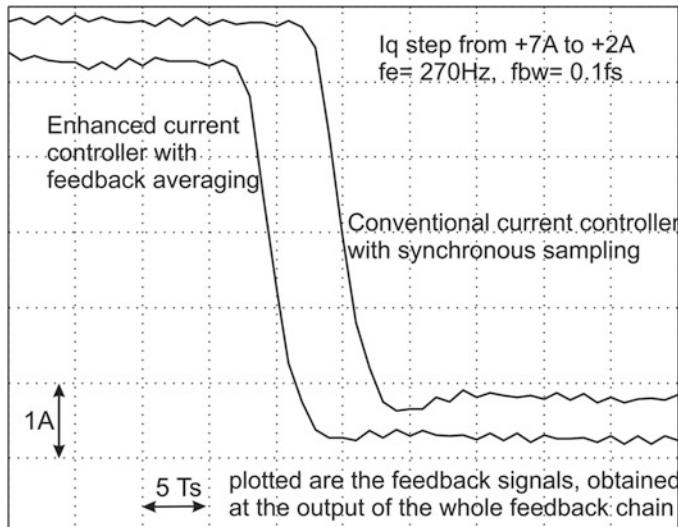

| Fig. 5.10 | Experimental traces of the $q$ -axis current step response at relatively low output frequency $f_e$ and with the closed-loop bandwidth $f_{BW} = 0.1/T_S$ . The upper trace corresponds to synchronous center-pulse sampling feedback acquisition and the controller without the series compensator. The lower trace corresponds to the one-PWM-period feedback averaging and the enhanced controller which includes the feedback averaging .....                                                                | 150 |

| Fig. 5.11 | The traces from the previous figure are enlarged for the ease of comparison .....                                                                                                                                                                                                                                                                                                                                                                                                                                | 150 |

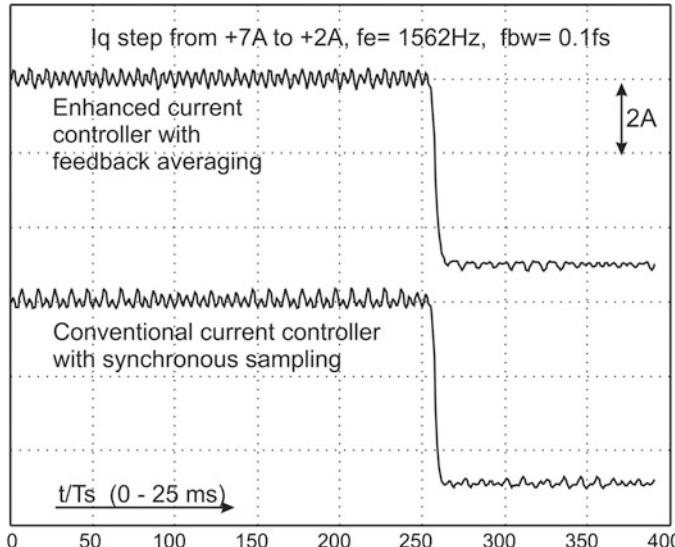

| Fig. 5.12 | Experimental traces of the $q$ -axis current step response at relatively high output frequency $f_e$ , with the closed-loop bandwidth $f_{BW} = 0.1/T_S$ and with the load that includes three star-connected inductances. The upper trace corresponds to synchronous center-pulse sampling feedback acquisition and the controller without the series compensator. The lower trace corresponds to the one-PWM-period feedback averaging and the enhanced controller which includes the feedback averaging ..... | 151 |

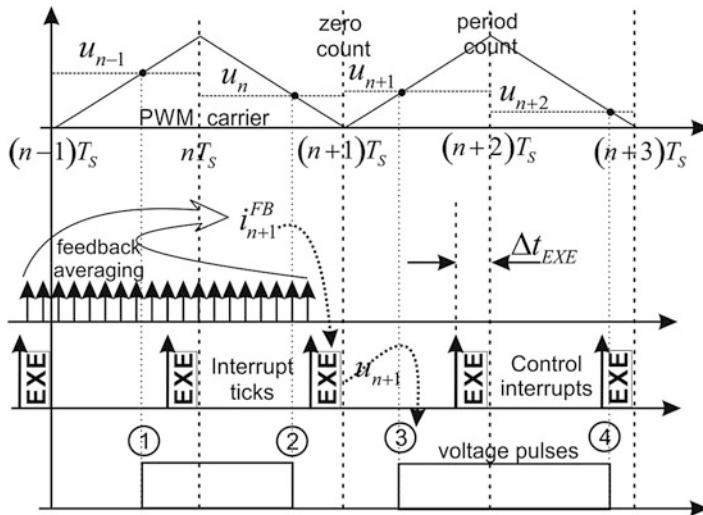

| Fig. 6.1  | Conventional scheduling of the current controller which relies on one-PWM-period feedback averaging .....                                                                                                                                                                                                                                                                                                                                                                                                        | 159 |

| Fig. 6.2  | Modified scheduling with the interrupt triggered $\Delta t_{EXE}$ before the zero-count and the period-count of the PWM carrier .....                                                                                                                                                                                                                                                                                                                                                                            | 159 |

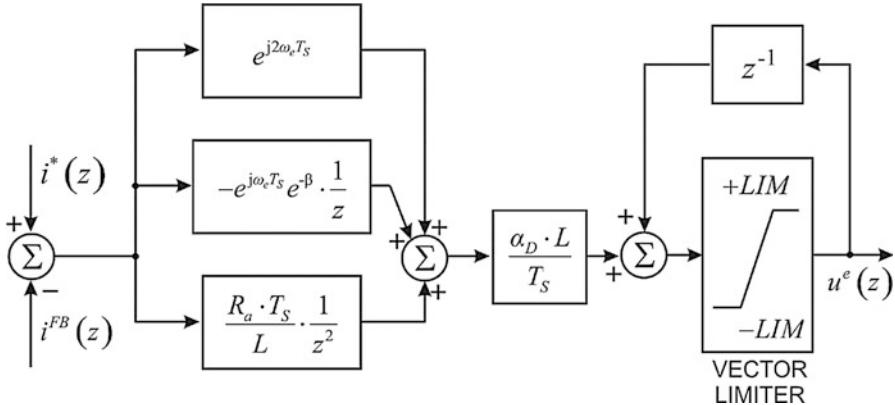

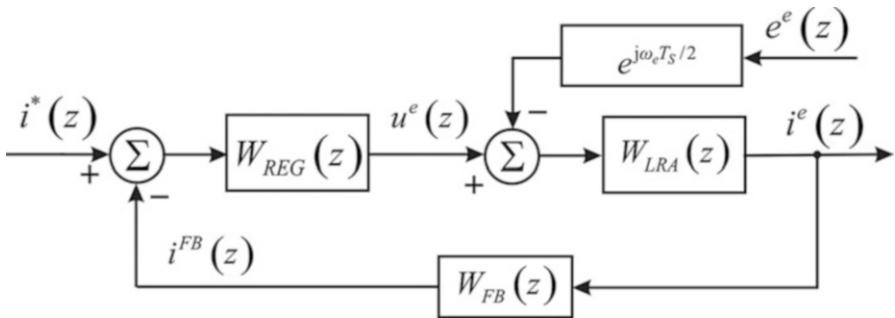

| Fig. 6.3  | Block diagram of the current controller in $d$ - $q$ frame .....                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 164 |

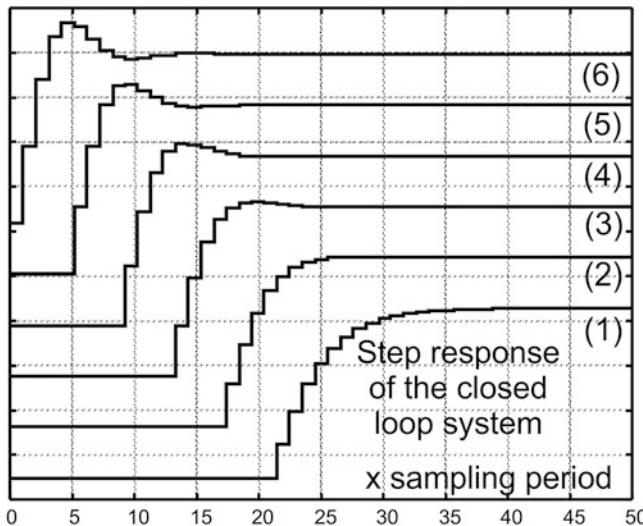

| Fig. 6.4  | Input step response from the pulse transfer function of (6.15) for the gain equal to $\alpha_D = 0.2$ (1), $\alpha_D = 0.25$ (2), $\alpha_D = 0.3$ (3), $\alpha_D = 0.35$ (4), $\alpha_D = 0.4$ (5), and $\alpha_D = 0.45$ (6) .....                                                                                                                                                                                                                                                                             | 166 |

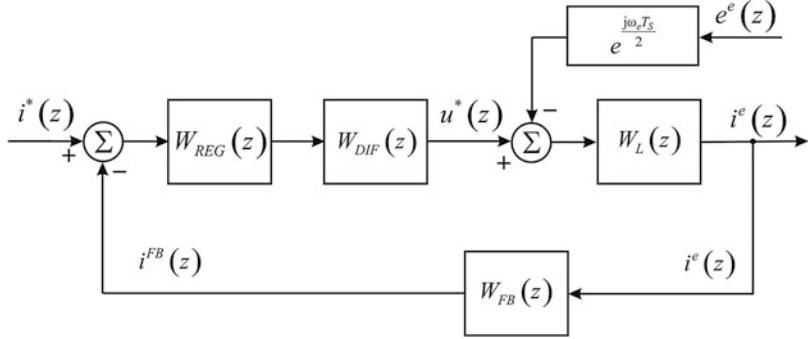

| Fig. 6.5  | Block diagram of the current controller in $d$ - $q$ frame with series differential compensator .....                                                                                                                                                                                                                                                                                                                                                                                                            | 168 |

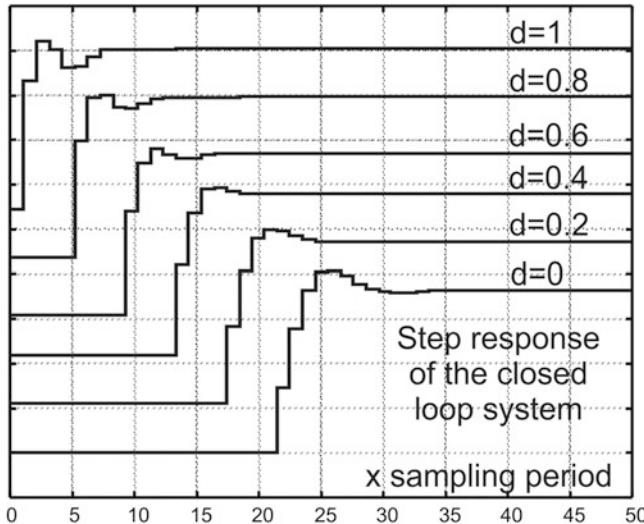

| Fig. 6.6  | Input step response from the pulse transfer function of (6.26) for the gain of $\alpha_D = 0.4$ and for the differential gain ranging from 0 up to 1 .....                                                                                                                                                                                                                                                                                                                                                       | 171 |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

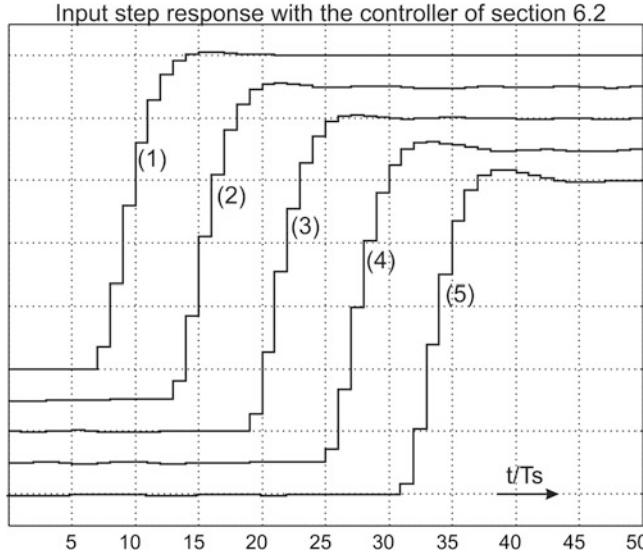

| Fig. 6.7  | Input step response of the $q$ -axis current obtained with the current controller of Sect. 6.2, which uses the advanced scheduling of the control tasks, and it does not use any series compensator. The trace 1 is obtained by computer simulation, and it serves for the reference. For the experimental traces 2–5, the time shift $\Delta t_{\text{EXE}}$ of the execution of the control interrupt is set to 2.4 $\mu\text{s}$ , 4 $\mu\text{s}$ , 8 $\mu\text{s}$ , and 12 $\mu\text{s}$ , respectively .....       | 173 |

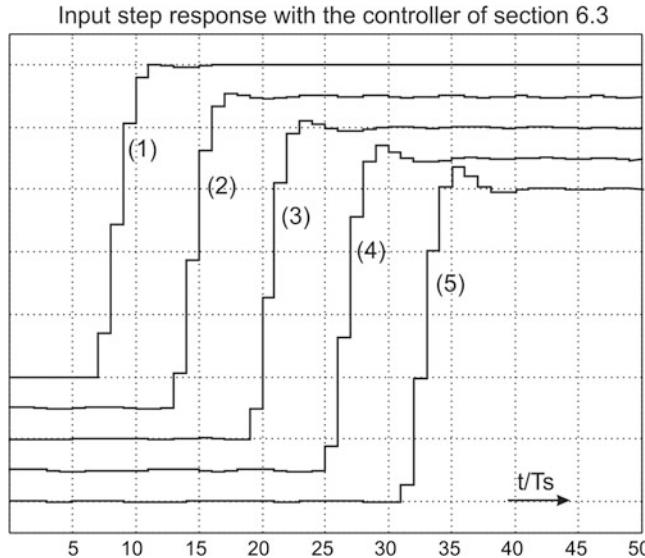

| Fig. 6.8  | Input step response of the $q$ -axis current obtained with the current controller of Sect. 6.3, which uses the advanced scheduling and also the series differential compensator. The trace 1 is obtained by computer simulation, and it serves for the reference. For the experimental traces 2–5, the time shift $\Delta t_{\text{EXE}}$ of the execution of the control interrupt is set to 2.4 $\mu\text{s}$ , 4 $\mu\text{s}$ , 8 $\mu\text{s}$ , and 12 $\mu\text{s}$ , respectively .....                           | 174 |

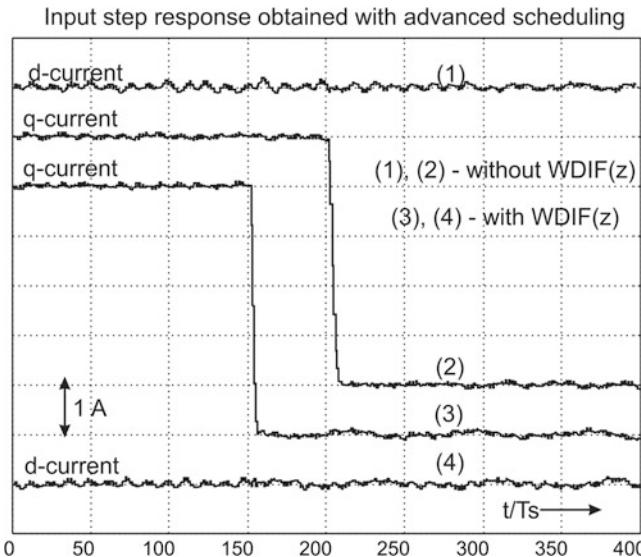

| Fig. 6.9  | Input step response of the $q$ -axis current and the contemporary waveform of the $d$ -axis current obtained in regime where the modulation indices and the output voltage reach 90% of their maximum value. The three-phase inverter supplies a brushless dc motor. The traces (1) and (2) were obtained with the current controller that uses the advance scheduling, but it does not use the series differential compensator. The traces (3) and (4) were obtained by adding the series differential compensator ..... | 175 |

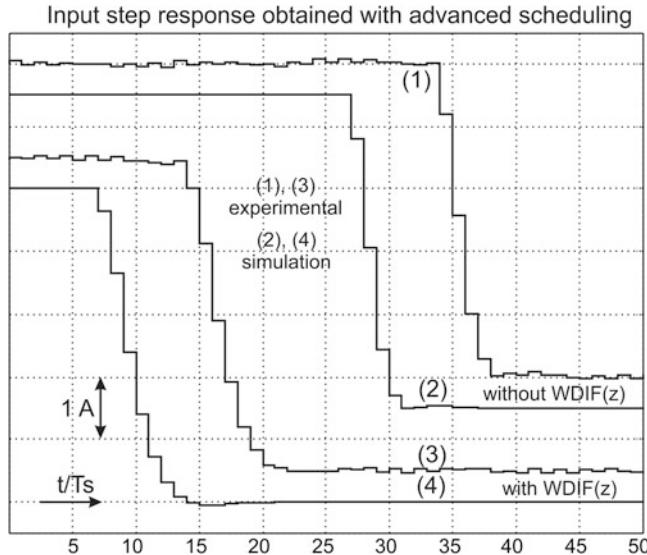

| Fig. 6.10 | Comparison of the experimental traces and the simulated traces. The traces represent the input step response of the $q$ -axis current. The experimental traces are obtained by enlarging the traces (2) and (3) of Fig. 6.9 .....                                                                                                                                                                                                                                                                                         | 176 |

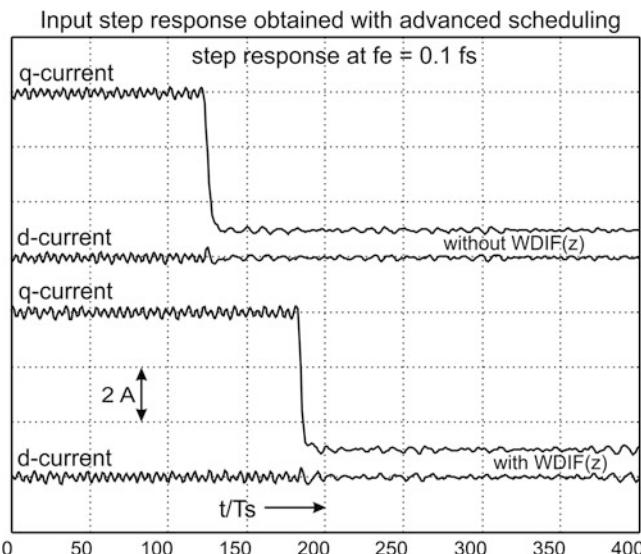

| Fig. 6.11 | Step response of the current controller at very high output frequency of $f_e = 0.1 \cdot f_S$ . The three-phase inverter is loaded with the three star-connected inductances. The two uppermost traces are obtained with the current controller which uses the advanced scheduling without the differential compensator. The bottom two traces correspond to the current controller with the series differential compensator .....                                                                                       | 176 |

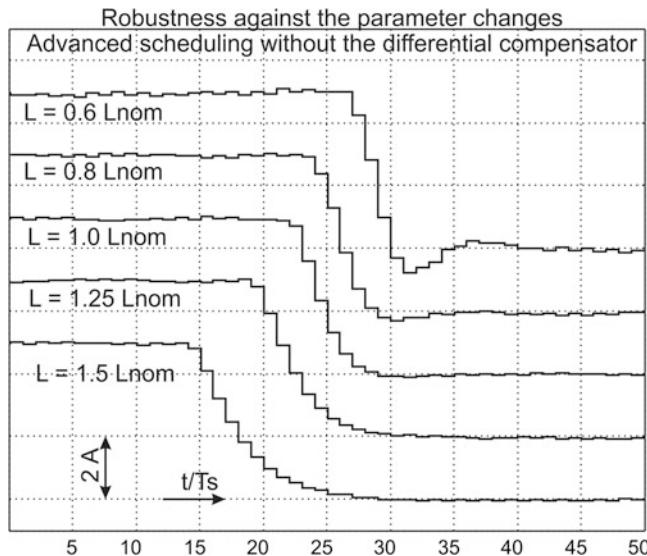

| Fig. 6.12 | The input step response in the presence of parameter changes. The traces are obtained with the current controller which uses the advanced scheduling without the differential compensator. The traces represent the step response of the $q$ -axis current. The ratio between the actual load inductance $L$ and the parameter $L_{\text{nom}}$ is changed. The parameter $L_{\text{nom}}$ is used within the algorithm to calculate the gain ( $\alpha_D L / T_S$ ) .....                                                | 177 |

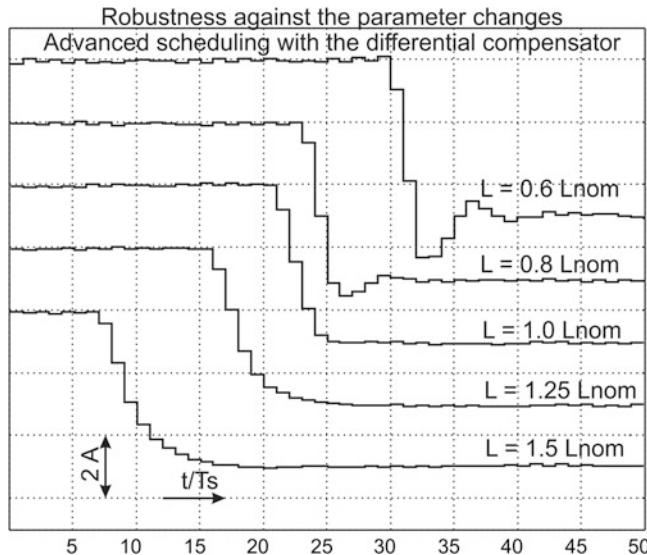

| Fig. 6.13 | The input step response in the presence of parameter changes. The traces are obtained with the current controller which uses the advanced scheduling with the differential compensator. The traces represent the step response of the $q$ -axis current. The ratio between the actual load inductance $L$ and the parameter $L_{\text{nom}}$ is changed.                                                                                                                                                                  |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

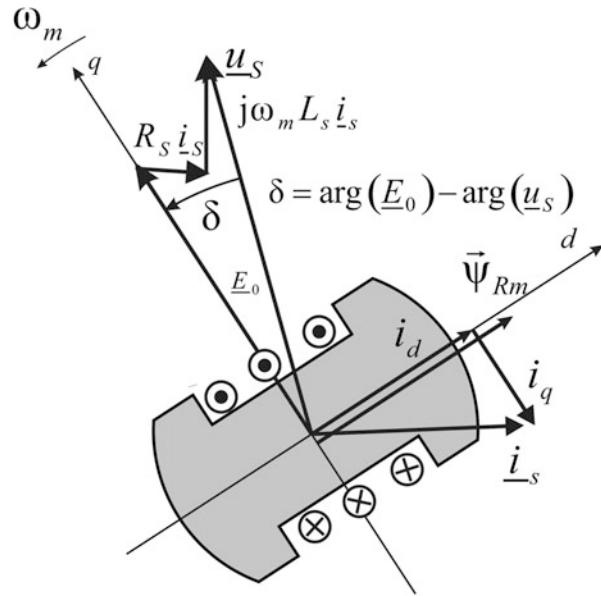

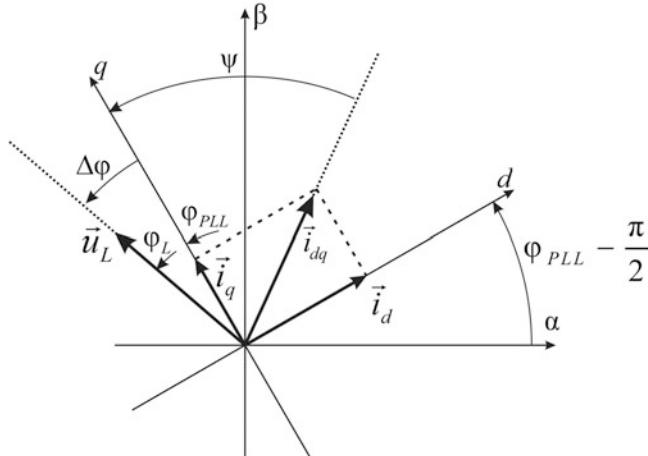

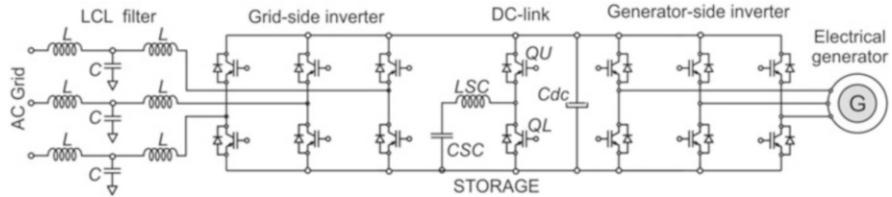

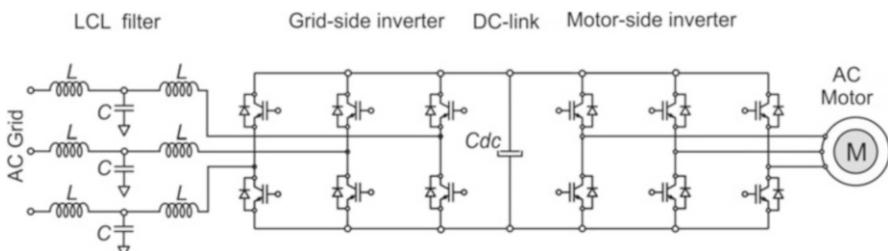

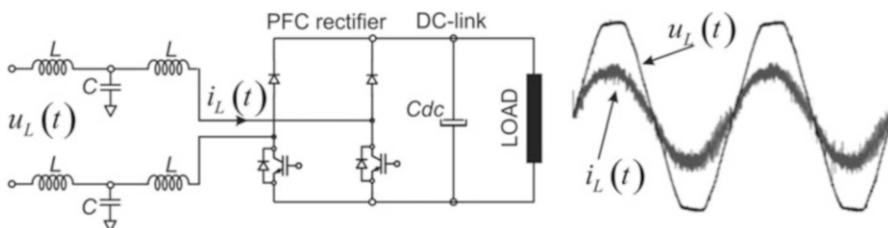

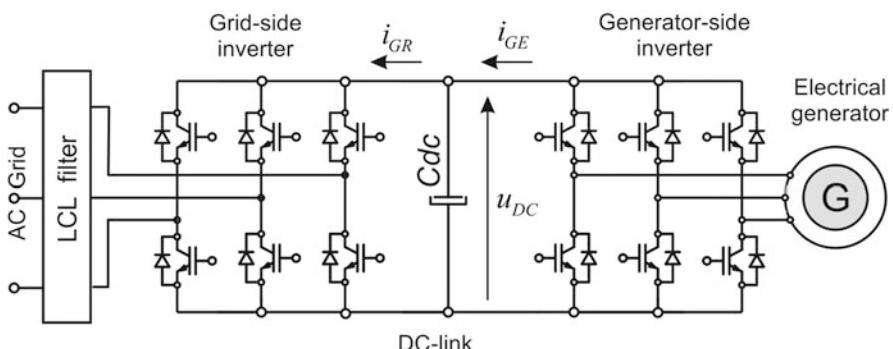

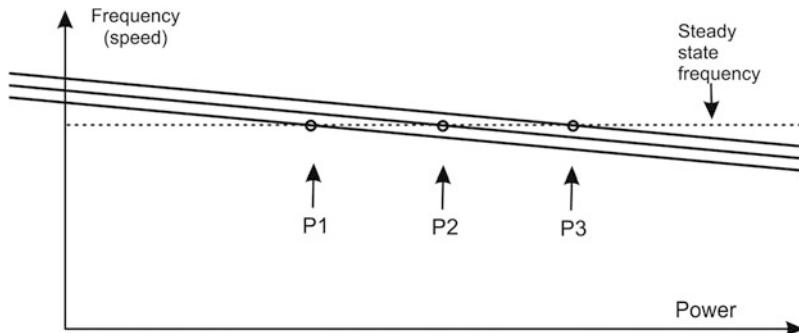

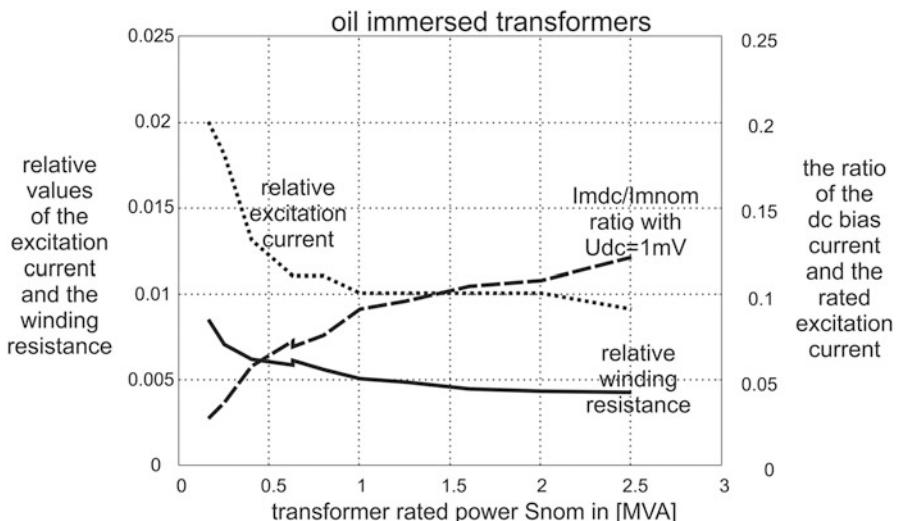

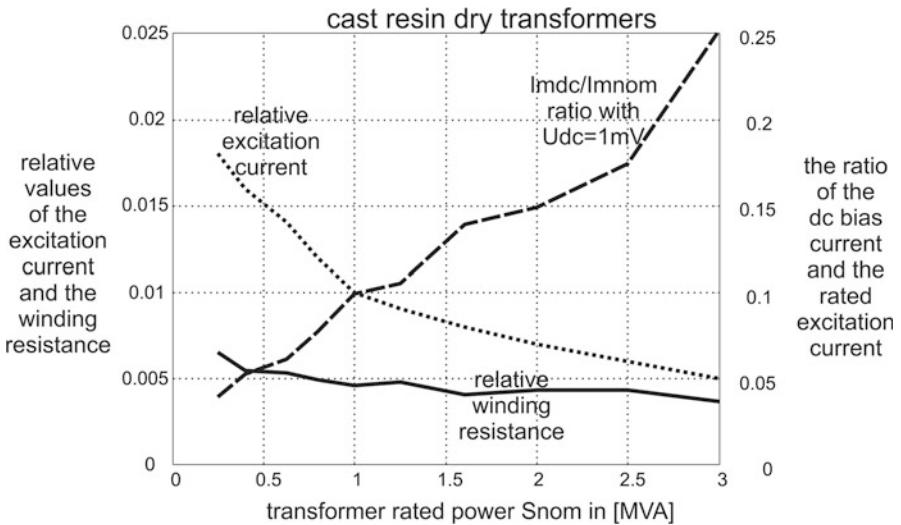

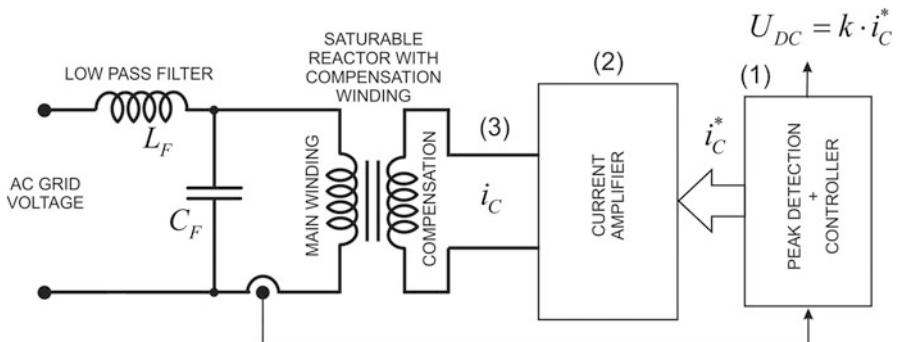

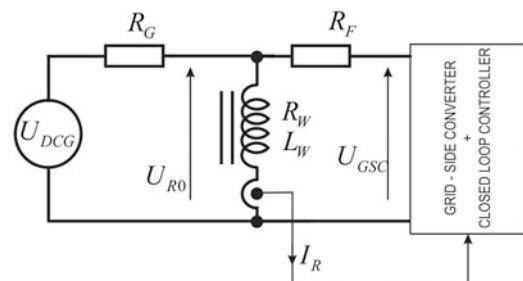

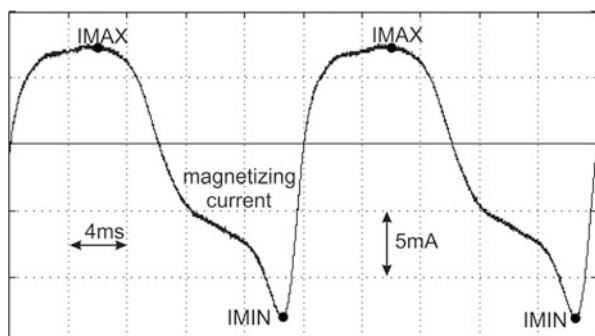

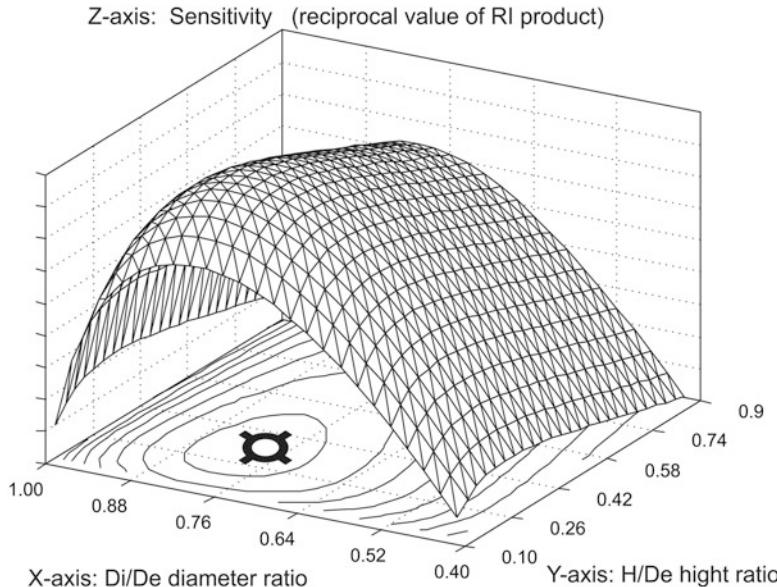

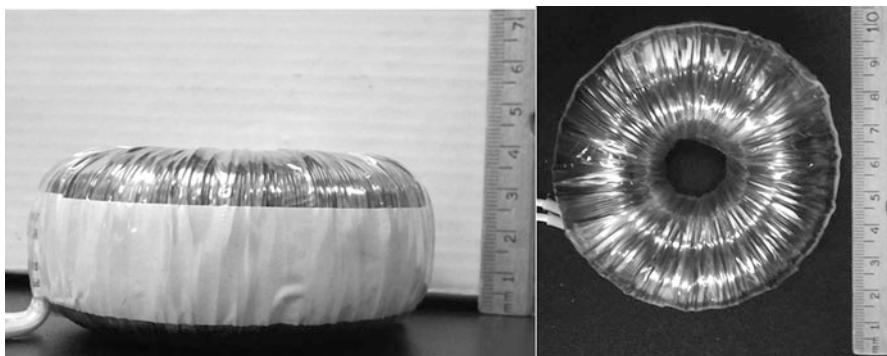

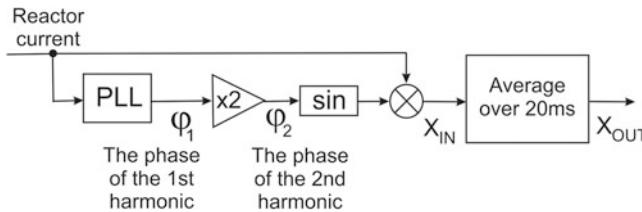

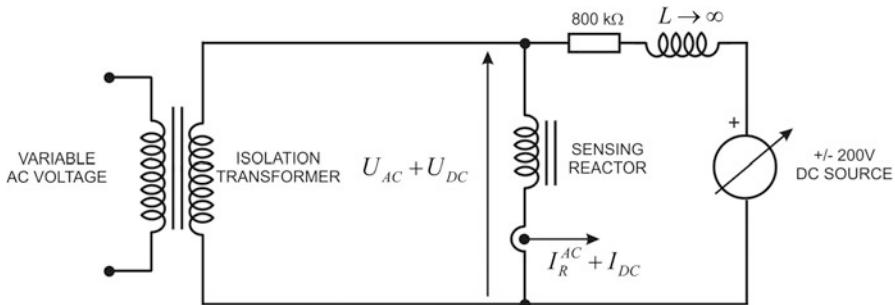

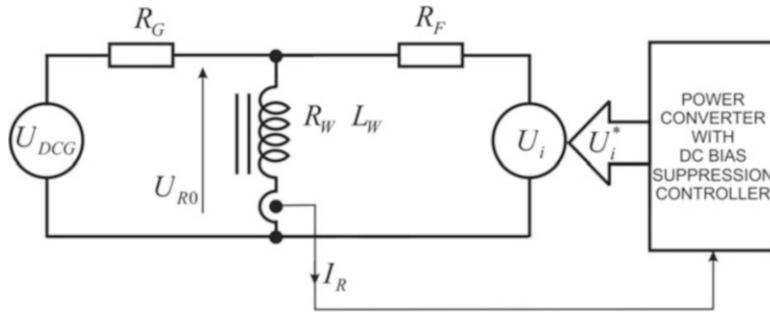

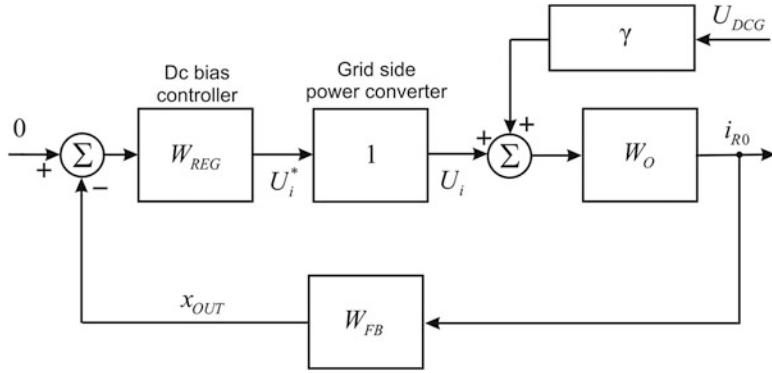

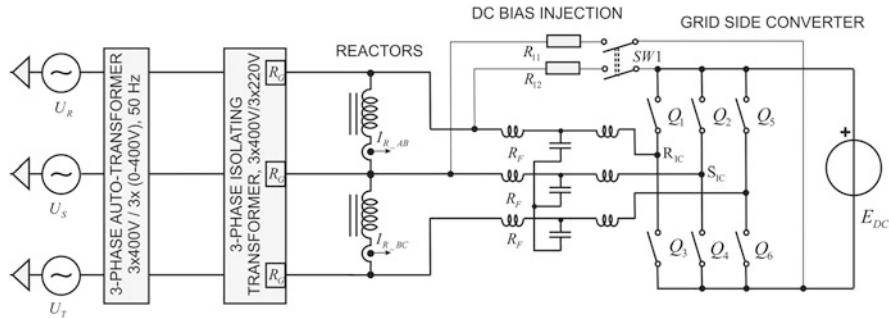

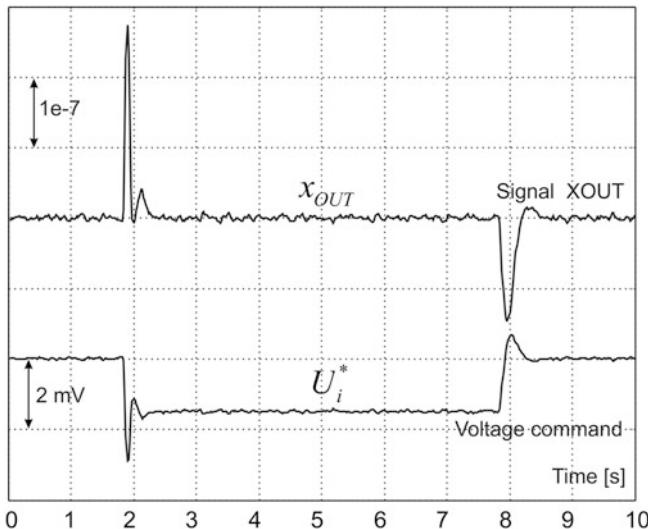

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|