EPFL STI – SEL      Téléphone : +4121 693 13 46

ELG 030              Fax :

Station n° 11          E-mail : [alexandre.levisse@epfl.ch](mailto:alexandre.levisse@epfl.ch)

CH-1015 Lausanne      Site web : [esl.epfl.ch](http://esl.epfl.ch)

Fundamentals of VLSI

September 2024

## FVLSI – Digital Design Flow

### Back End – From Synthesis to GDS

## 1. SETUP THE LAB ENVIRONMENT

For this part of the lab, we will use three new tools, namely Innovus, Embedit and Virtuoso configured for the 65nm globalfoundries design kit.

You will find them in your working environment.

## 2. TUNING THE SIZE OF AN SRAM MEMORY

As you did identify previously, the 64x64bit memory appeared as a bottleneck in the design, from an area standpoint. In this section, we propose to explore how to generate a SRAM memory using a tool called a “memory compiler”. And generate smaller memories which could improve the density of the design we are exploring.

### 2.1. GENERALITIES ABOUT SRAM MEMORIES

SRAM memories are complex and cannot be automatically generated by a synthesis tool. For e.g. instantiating in a RTL language, an array of memorization points will infer an array of flipflops. This is inefficient from an (i) area, (ii) power and (iii) speed standpoint from a certain size. Thereby, it exists some kind of trade-off between the memory size, and its implementation as an array of register files and the need for the utilization of an SRAM memory<sup>1</sup>.

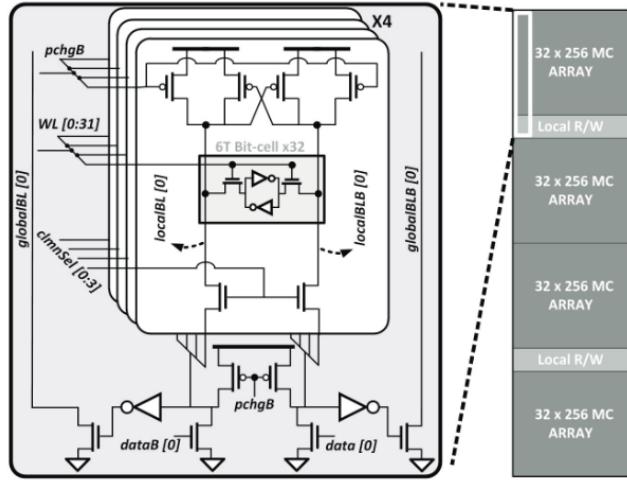

An SRAM bitcell is built as shown in the following picture. It is practically composed of two inverters and two NMOS transistors called access transistors. The SRAM bitcells are then organized in columns and rows. The following screenshot shows an example of memory organization from a publication in the ISSCC conference<sup>2</sup>. In that case, several small 32x256bitcells arrays are built, each with their associated peripheral circuit. These blocks are then replicated and connected together to build larger memory arrays.

<sup>1</sup> Some works actually explored the trade-off <https://ieeexplore.ieee.org/abstract/document/5976987>

<sup>2</sup> <https://ieeexplore.ieee.org/document/5746310>

Each block composing a SRAM array has to be designed with the full custom flow as you did learn during phase 1 of these labs. As today memory compose more than 50% of the area of advanced chips, being able to automate the design of such blocks is mandatory.

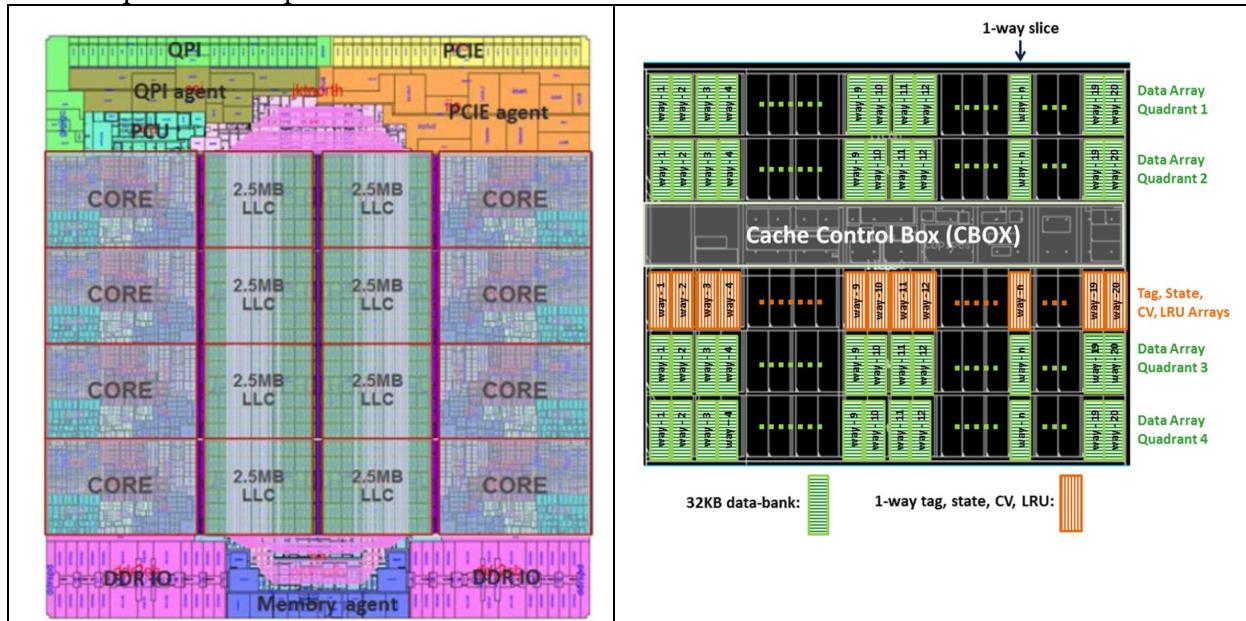

Let's start with an example of an actual memory, to understand the complexity of real memory systems. Note that here we only focus on the physical organization of a memory from a 2013 processor built in 32nm CMOS technology. We do not detail process associated with cache management etc.

The associated screenshots is a detailed Last Level Cache memory hierarchy example of a 2013 Xeon chip from Intel published<sup>3</sup>.

<sup>3</sup> <https://ieeexplore.ieee.org/abstract/document/6515193>

On the top left, one can see the 8 processors (CORE), and the 8x2.5MB (Mega Byte) LLC (Last Level Cache) in the middle, which overall makes 20MB (note that each LLC block is not tied to a core but that it is overall controlled by the memory agent on the bottom, each block being controlled by its Cache Control Box – cf top right picture). The right picture is a zoom in on a 2.5MB block. It is composed of 20 “way slices” (vertical) of 128KB each composed of 4 32KB data banks (green boxes). Each 32KB data-bank is composed of 2 16KB data sub-array shown on the bottom picture.

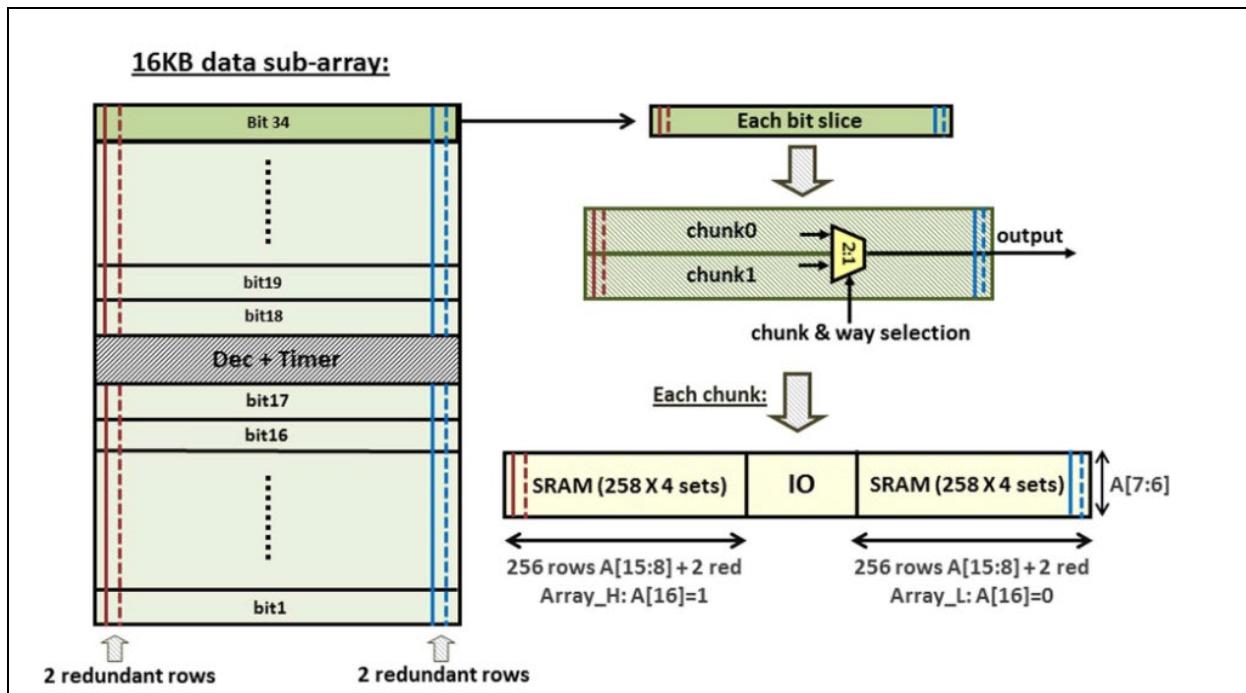

The 16KByte array is then cut into 34 “bit” slices. Each “bit” slice is composed of two “chunks” (chunk 0 and chunk 1). Each chunk is composed of two 258 x 4 bitcell SRAM arrays.

Let's make the calculation :

1 chunk is  $2 * (258 * 4)$  bits = 2.064bits

1 bit slice is 2 chunks = 4.128bits

1 data sub array = 34 bit slices =  $34 * 4.128$ bit = 140.352bits = 17.544Bytes

And so on...

- ① Note how the number of bits does not match the actual memory size, and how things do not match between the physical quantity of bits being integrated.

- ① The 16KB actual memory size is only obtained when removing physical redundancy bitcells (in preision of failure for e.g.), reserved ECC (Error Correction Codes) bits etc.

Bottomline being that the physical organization of a memory is not homogeneous, extremely hierarchical. Ultimately, unitary memory blocks are relatively small, here around 16KB. Picture that each of these 16KB blocks is replicated 1280 times to make the complete 20MB LLC cache.

When diving down the CORE block, besides the LLC, in these Xeon cores, there is also a L2 and a L1 cache, private for each processor. In this architecture, the L2 has a 256KB hierarchical

organization while the L1 is 32KB<sup>4</sup> with the same kind of oversizing as we discussed before. Note that the L1, L2 and LLC are built with different constraints in terms of speed. Closer cache levels are expected to go faster, while LLC is expected to be denser and slower.

Various parameters can be tuned to change the performances of a memory in terms of speed or power. One of them is by tuning the size of the memory. Indeed, smaller arrays mean less metal, in line meaning faster access (remember the layout of your 8bit adder ?).

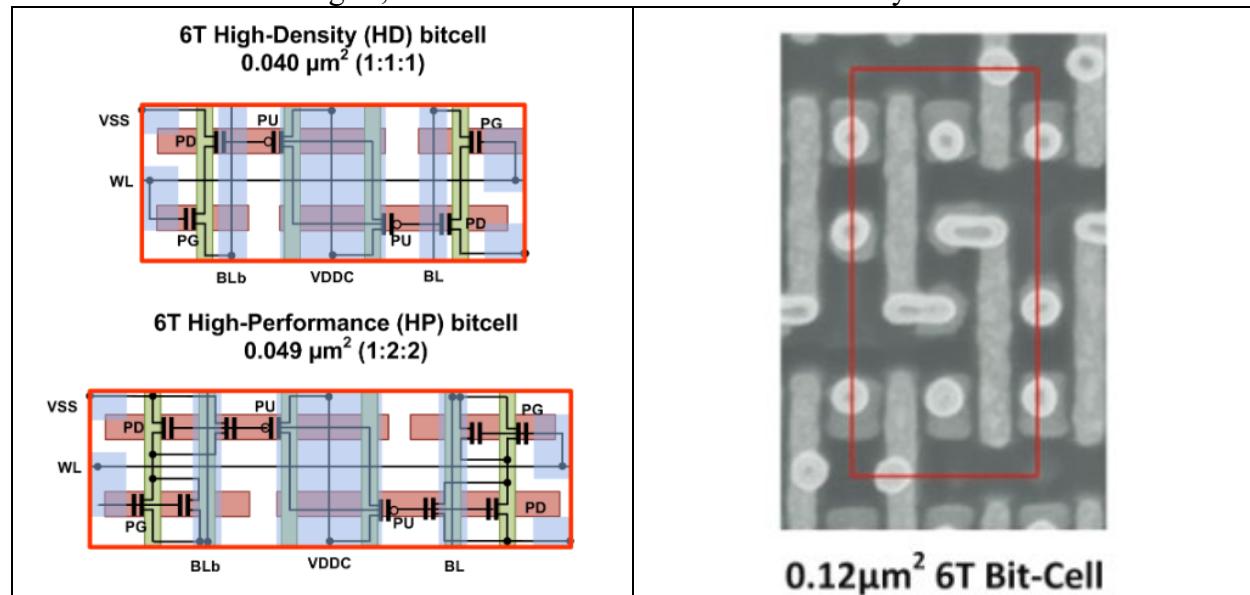

Another approach consists in tuning the parameter of the access transistors. The following left figure is an example of two different bitcells in 10nm FinFet technology from Samsung<sup>5</sup>. Both being what we call 6T (6 transistor) SRAM, the top one High Density (HD), the bottom one High Speed (HS). Here, increasing the width of the access transistors (called PG) and of the pulldowns (called PD) makes the bitcell go faster for read operations.

❶ In finfet technologies, the width of a transistor is controlled by the number of fins.

One particularity of SRAM (and memories in general), that they have an extremely regular layout pattern as opposed to logic circuits (as you did in your 8bit ALU). Thereby, SRAM designers can discuss with the foundry and negotiate on breaking DRC rules. The main reason being that DRC rules are built for logic circuits and can be twisted in some case, if agreed with the foundry. The right part of the graph above shows a SEM picture of a 6T SRAM cell (Poly, Active and Contacts). Note the rectangular contacts, this is generally forbidden in logic DRC.

**Then, what does a memory compiler do ?**

There is no general rules. Each provider does things in their ways. Though, the general approach is as follows. The process of designing a SRAM memory starts by designing and evaluating by hand a memory. Then evaluating the trends and characterizing the different blocks. Build them in a way that they can be automatically and efficiently abutted. Build a performance/power/area

<sup>4</sup> <https://www.intel.com/content/www/us/en/support/articles/000027820/processors/intel-xeon-processors.html>

<sup>5</sup> <https://ieeexplore.ieee.org/abstract/document/7725555>

model. Finally, build a tool that builds a memory that meets the specifications required by the user based on these models. Bottomline being that a memory compiler is mainly playing lego with already existing/configurable blocks.

Once these basics are understood, let's now play with a memory compiler and build different memories.

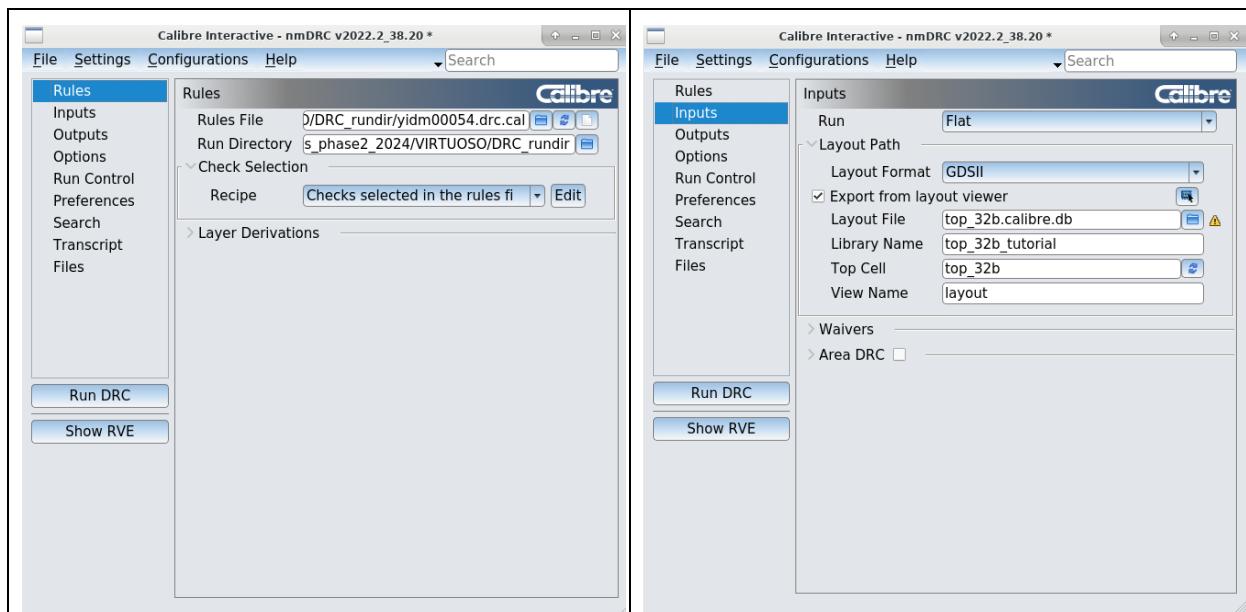

## 2.2.USING THE MEMORY COMPILER EMBEDIT FROM SYNOPSYS

The Synopsys company does develop EDA tools (such as DesignCompiler or PrimeTime) though they are also a renown high quality silicon IPs which companies and universities can license and use their designs<sup>6</sup>.

In this lab, we will use the Synopsys memory compilers and their tool called Embedit. Note that there exist hundreds of memory compilers, each having their own specificities. We use embedit here as it provides a comfortable-to-use Graphical User Interface (GUI), though, most of the memory compilers do not provide GUI (surprised ? you should not be).

1. Go in the EMBEDIT folder

```

edalabs_phase2_2024>cd EMBEDIT

```

2. Run the integrator tool (don't forget the space between snps and integrator)

```

EMBEDIT> snps integrator &

```

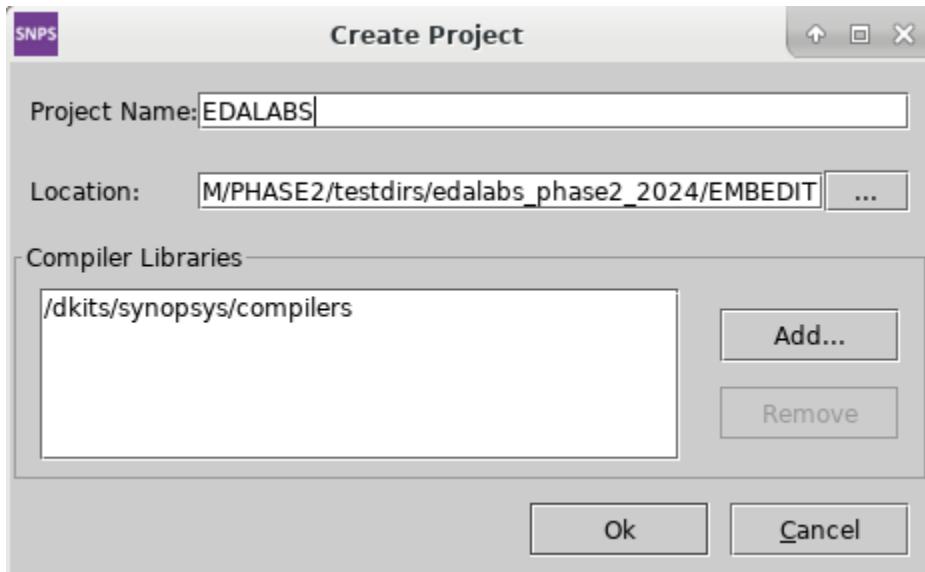

3. Click on project>New

4. Call the project EDALABS

<sup>6</sup> <https://www.synopsys.com/designware-ip.html>

5. Keep the location in the EMBEDIT folder

6. Click OK → *in the screenshot, the path may not be the same as yours*

7. Check the message panel of the GUI. It should print a list of INFO about glb files in the `/dkits/synopsys/compilers/` folder being read.

```

INFO [Integrator, CFG-018]: Reading file

'./dkits/synopsys/compilers/cp65npks1p10aspv201msa05p1/cp65npks1p10a

spv201msa05p1.glb' ...

INFO [Integrator, CFG-018]: Reading file

'./dkits/synopsys/compilers/cp65npy1p11asdr132ksa04p3/cp65npy1p11a

sdrl132ksa04p3.glb' ...

INFO [Integrator, CFG-018]: Reading file

'./dkits/synopsys/compilers/cp65npy1p11sads1512sa06p4/cp65npy1p11s

ads1512sa06p4.glb' ...

INFO [Integrator, CFG-018]: Reading file

'./dkits/synopsys/compilers/cp65npy1p11sass1512sa05p2/cp65npy1p11s

ass1512sa05p2.glb' ...

INFO [Integrator, CFG-018]: Reading file

'./dkits/synopsys/compilers/cp65npy2p11asdr132ksa05p2/cp65npy2p11a

sdrl132ksa05p2.glb' ...

INFO [Integrator, CFG-018]: Reading file

'./dkits/synopsys/compilers/cp65npy2p22sads1512sa04p4/cp65npy2p22s

ads1512sa04p4.glb' ...

INFO [Integrator, CFG-018]: Reading file

'./dkits/synopsys/compilers/cp65npy2p22sass1512sa04p1/cp65npy2p22s

ass1512sa04p1.glb' ...

```

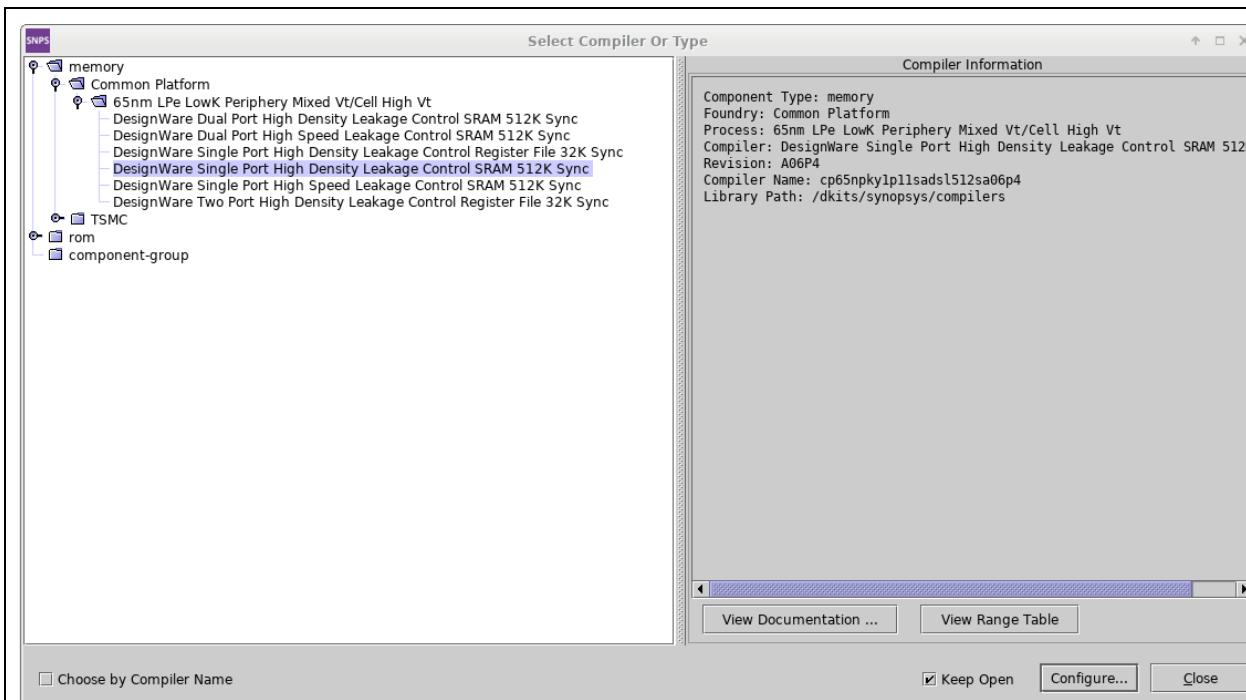

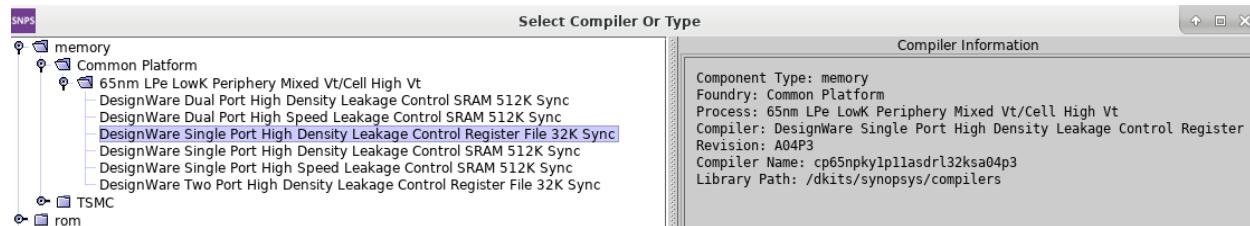

8. Click on and expand the part related to Common Platform<sup>7</sup> and 65nm LPe LowK Periphery Mixed Vt/Cell High Vt.

9. Select the Single Port High Density Leakage Control SRAM 512K Sync (make sure you select the compiler name `cp65npy1p11sads1512sa06p4`)

10. Click Configure

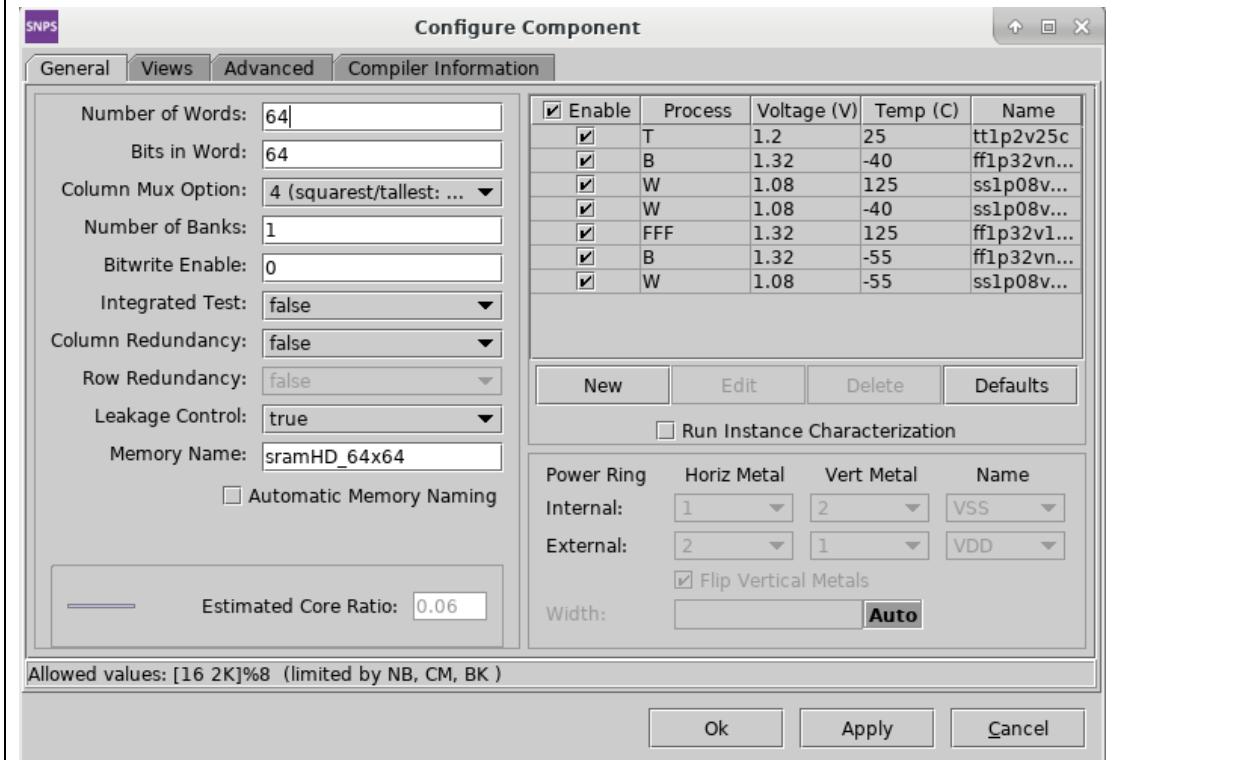

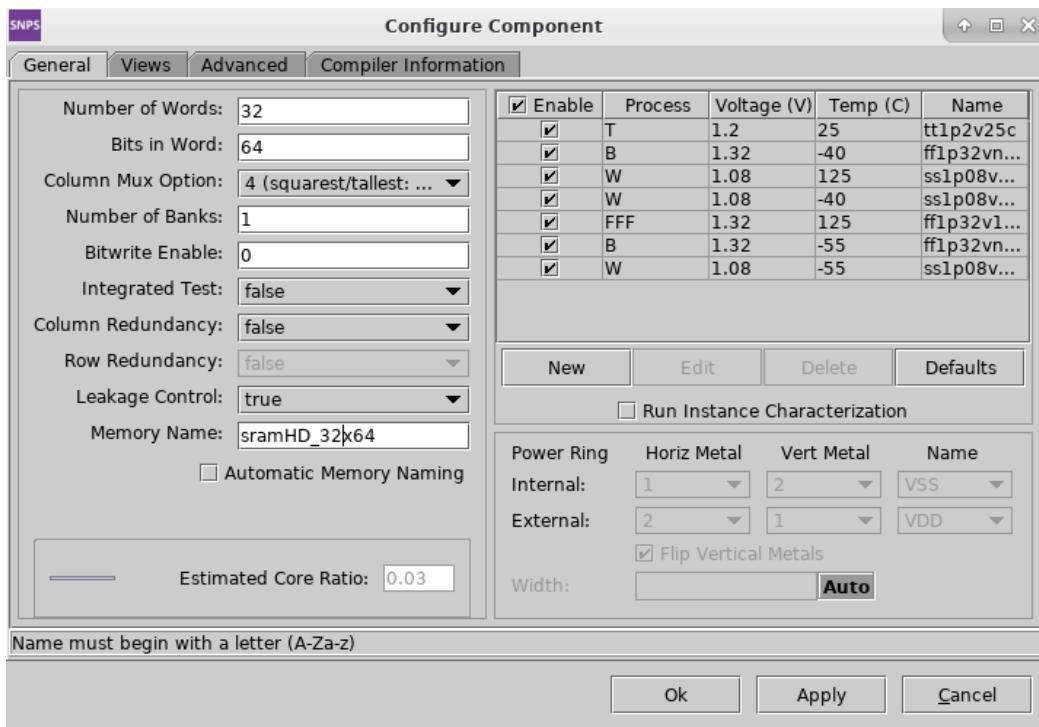

11. Fill the Configure Component window as follows. Make sure you properly untick “automatic memory naming” and call it sramHD\_64x64. Make it 64 words of 64 bits with a squarest aspect ratio.

Note all the corners. You could potentially create new corners if you wanted to use the memory in different conditions. Note that generally, memory compilers do not provide arbitrary parameters, but only parameters in a given range.

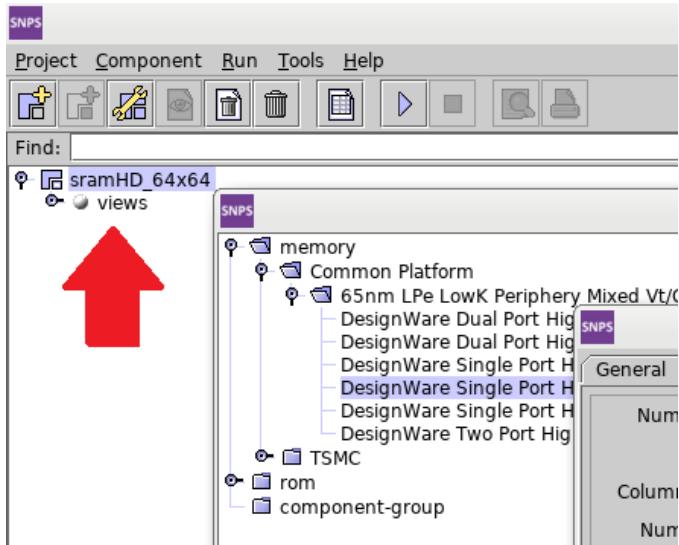

12. Press Apply. And see the sramHD\_64x64 appear in the main window of embedit.

13. Change the numbers of word to 32, change the name to sramHD\_32x64

14. Press Apply

① Note that you can change more advanced parameters in the panel “views” and “advanced”. Have a look there, but keep everything as set by default.

15. Do the same for 16words and call it sramHD\_16x64

16. Press OK to close the window.

17. Close the select type of compiler window by clicking “close”

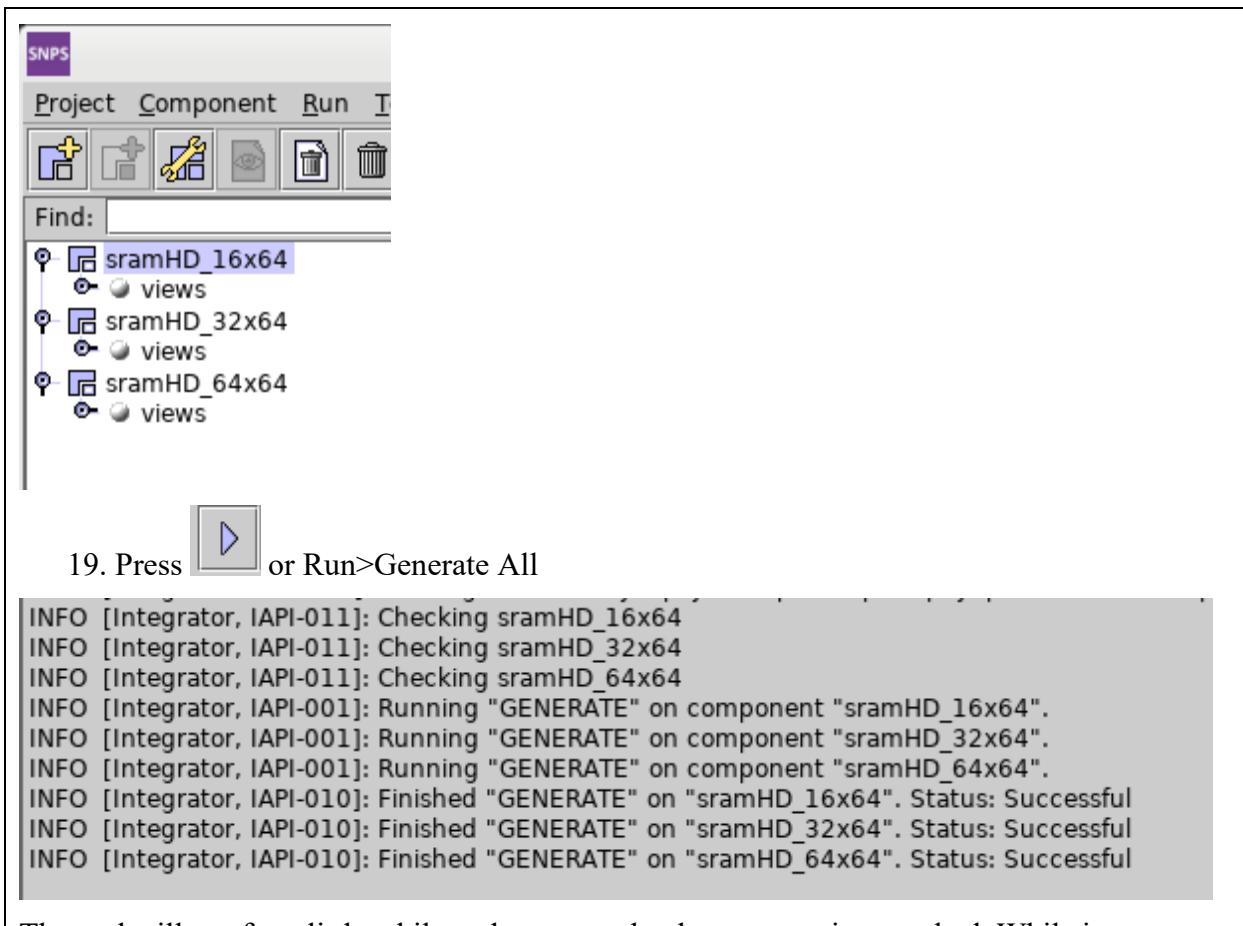

18. You should now see the following :

19. Press  or Run>Generate All

```

INFO [Integrator, IAPI-011]: Checking sramHD_16x64

INFO [Integrator, IAPI-011]: Checking sramHD_32x64

INFO [Integrator, IAPI-011]: Checking sramHD_64x64

INFO [Integrator, IAPI-001]: Running "GENERATE" on component "sramHD_16x64".

INFO [Integrator, IAPI-001]: Running "GENERATE" on component "sramHD_32x64".

INFO [Integrator, IAPI-001]: Running "GENERATE" on component "sramHD_64x64".

INFO [Integrator, IAPI-010]: Finished "GENERATE" on "sramHD_16x64". Status: Successful

INFO [Integrator, IAPI-010]: Finished "GENERATE" on "sramHD_32x64". Status: Successful

INFO [Integrator, IAPI-010]: Finished "GENERATE" on "sramHD_64x64". Status: Successful

```

The tool will run for a little while and generate the three memories as asked. While it runs, start reading the rest of the document and section 1.3. And come back here once finished.

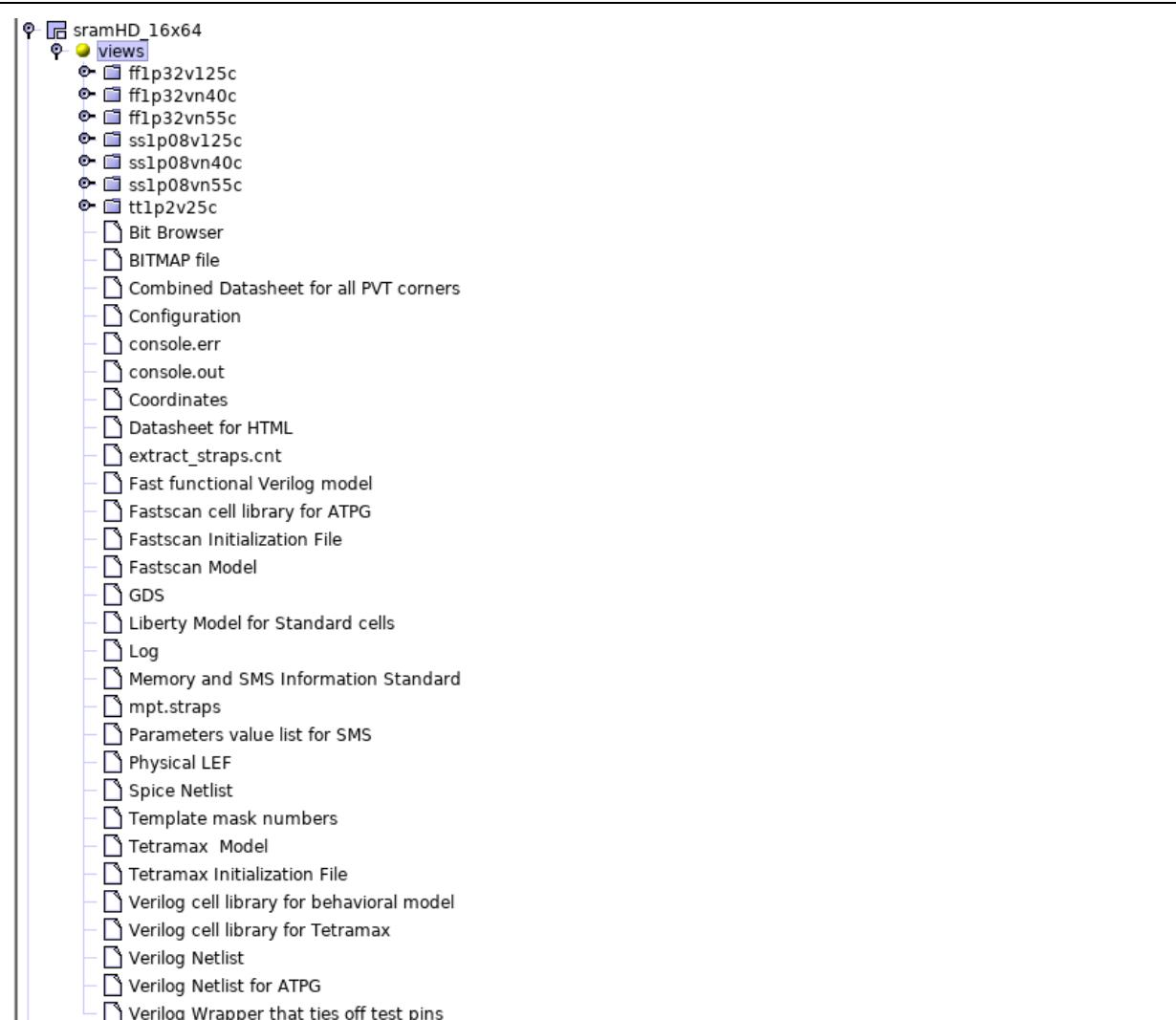

20. Expend the views in one of the generated memories. Note all the files and folders that have been created by the compiler.

QUESTION 2-1 : what's the difference between a single port and a dual port memory ?

QUESTION 2-2: What's the difference between the SRAM and a register file ? From a physical standpoint. Check the available parameters in the compiler for a “High Density Leakage Control” SRAM and Register file. Then rephrase it with your own words the comment below.

- ❶ It is important at this point, if you come from a computer science background, or have had experience with architectural design, to “align your vocabulary”. The vocabulary difference between circuit-level memory designers and architects is deep. The motivation behind these naming resides in the fact that SRAM are generally larger then Register Files. So, register files are generally adapted for small and fast memories and will become suboptimal for larger ones. And conversely for SRAM. The documentation of the cp65npky1p11asdr132ksa04p3 is available on moodle. Check it out (specifically section

2.3.6) compare it to the same section in the cp65npy2p22sads1512s documentation – alternatively you could click on “View Range Table” in the compiler GUI.

## 2.3. EXPLORING THE OUTPUT FILES

A memory compiler generate the files which are needed in the design process. As a designer, in order to include a memory, you need :

- A Verilog (.v) or Vital (.vhd) file to simulate the behavioural of the memory in your design.

- ① Note that vital is getting more and more deprecated.

- A liberty (.lib) file which contains the timing information from the memory, for the timing and power analysis.

- A library exchange format (.lef) which contains the physical specifications of the memory and its pins positions.

- You could also get other files such as test models (remember EE530?).

These are call the Front end views. Most of the agreements you may get with an IP provider do only involve front end views as these do not contain the details of the design and allow a company to share IPs without taking too many risks on their design knowhow.

The following views are generally more sensitive and not gracefully shared by IP providers without strong NDAs and associated liabilities.

- GDS views. The detailed layout of the IP that could be imported in a layout editor (such as virtuoso).

- Spice netlists. Containing the detailed spice netlist of the design with all the transistor sizes.

Let's first explore the spice netlist :

1. Double click on the Spice Netlist and scroll through it. It should remind you something from phase 1.

**QUESTION 2-3: scroll through the netlist and find devices starting with MP and MN. What do these correspond to ?**

① Mos transistors in a netlist are generally syntaxed as follows : InstanceName Drain Gate Source Bulk PDKdeviceName Parameters(W,L etc.)

Let's then explore a the GDS :

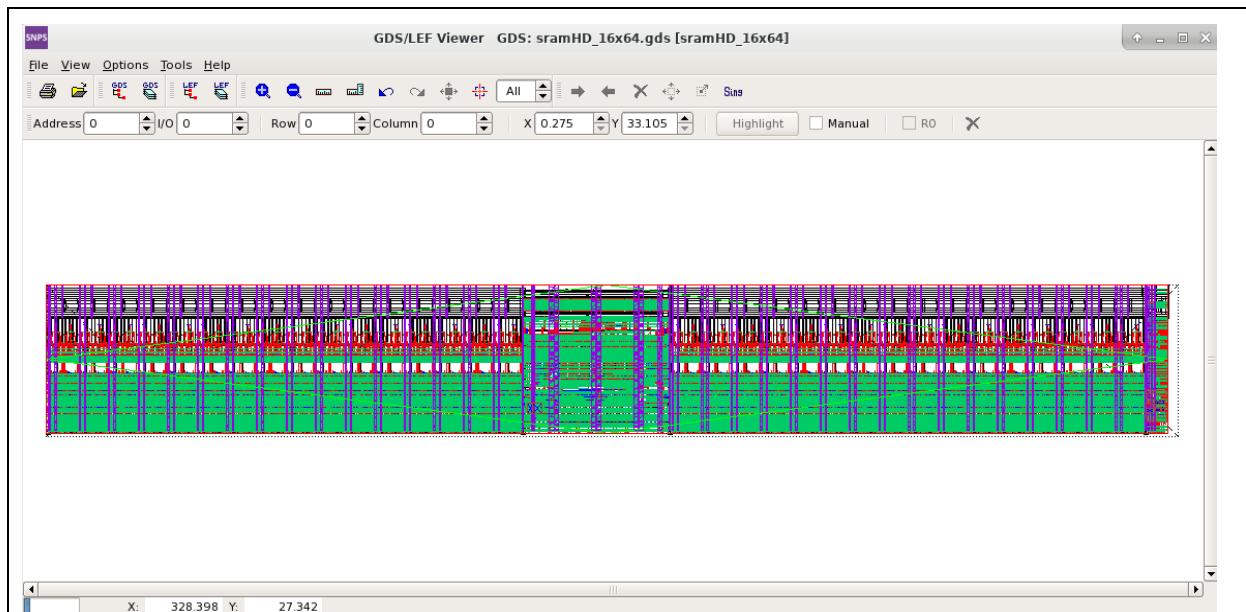

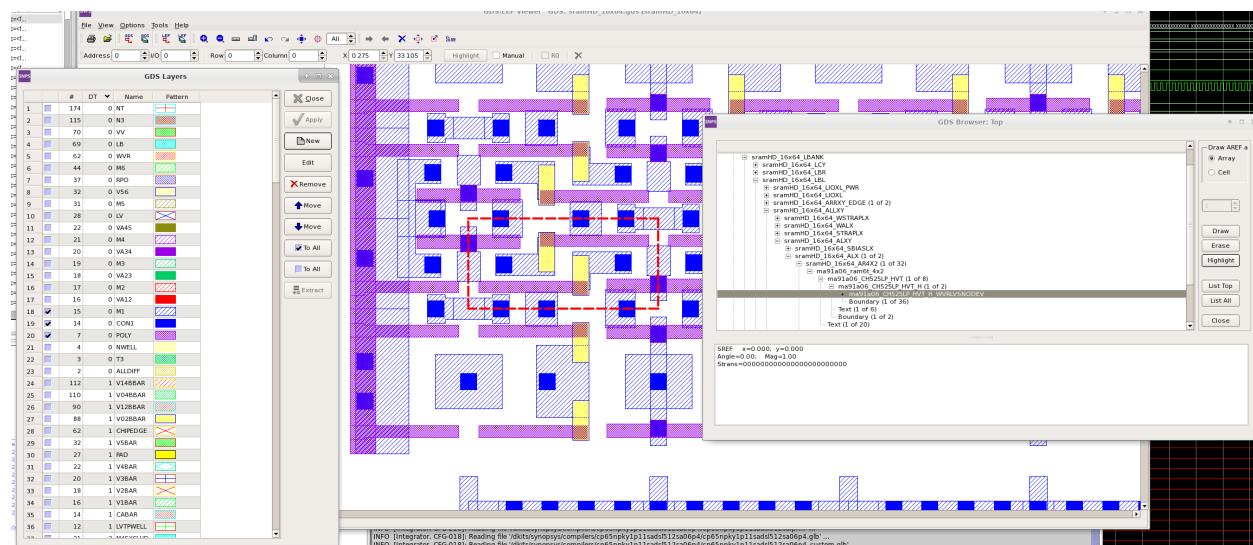

1. Double click on the GDS in the list

2. A new window opens, resize to make it easy to read. This is a GDS viewer.

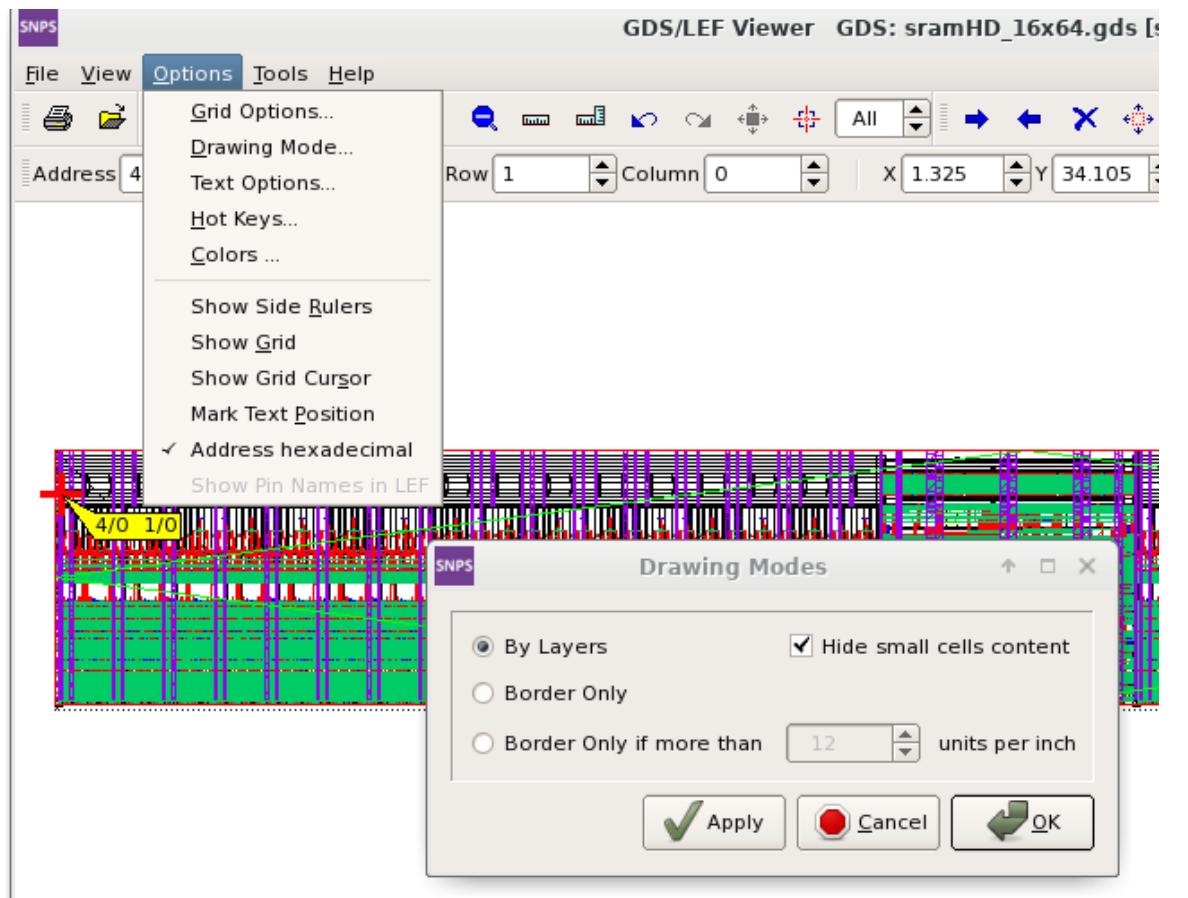

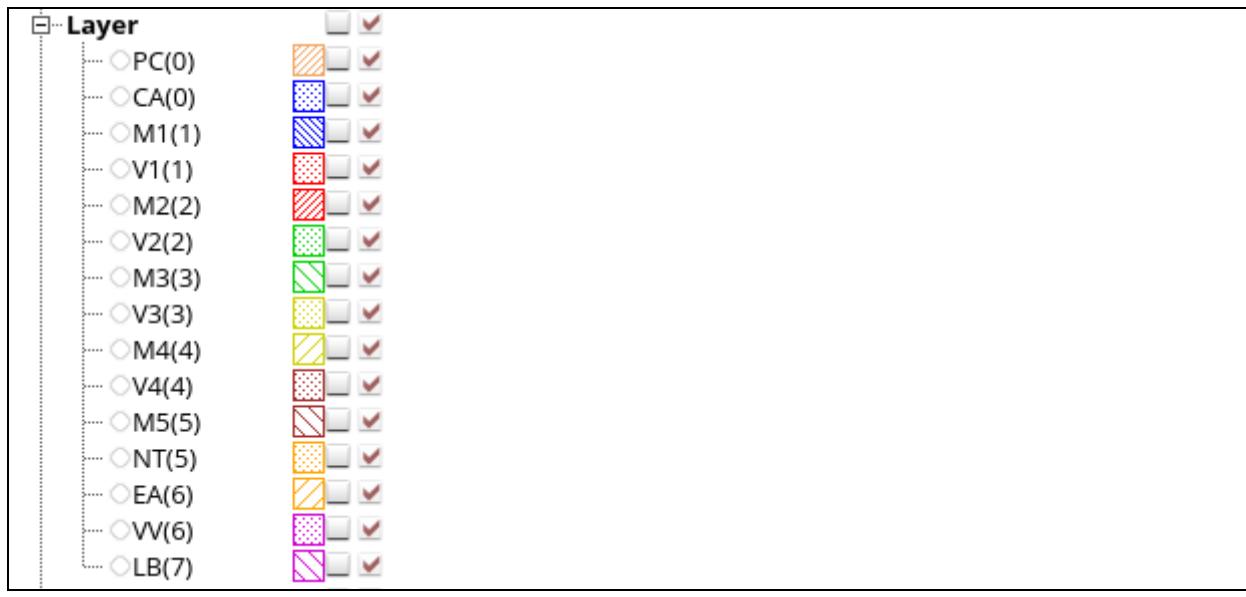

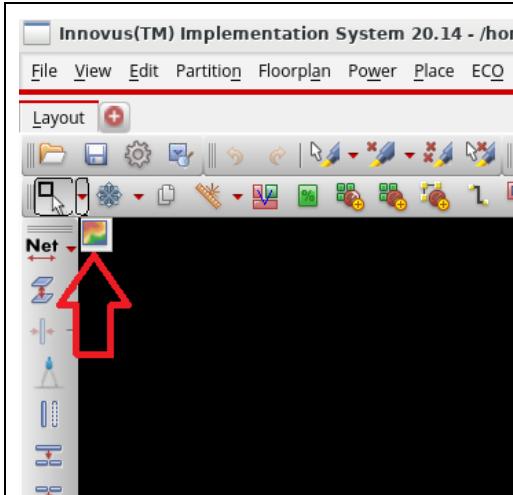

Use the  to fit the view to the screen.

3. Click on Options>Drawing Mode and make sure that the drawing mode is “By Layer”

4. Press OK

5. You can zoom in by left-clicking and maintaining to draw the zone to zoom in.

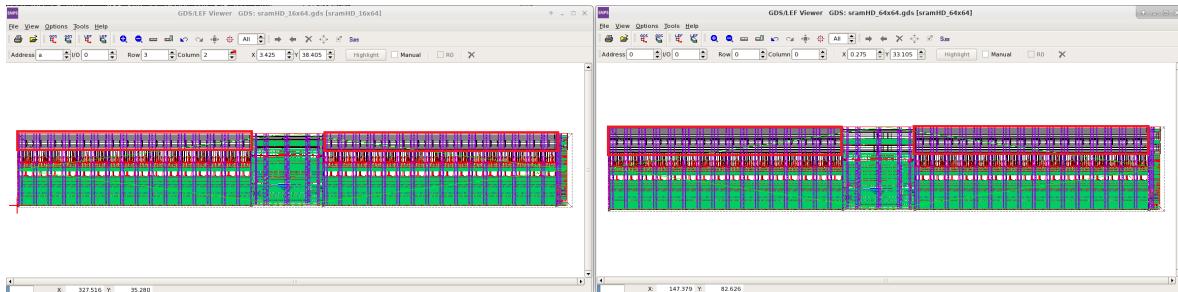

6. Explore the design, and zoom down to the transistor-level layout. To zoom out, use the fit button.

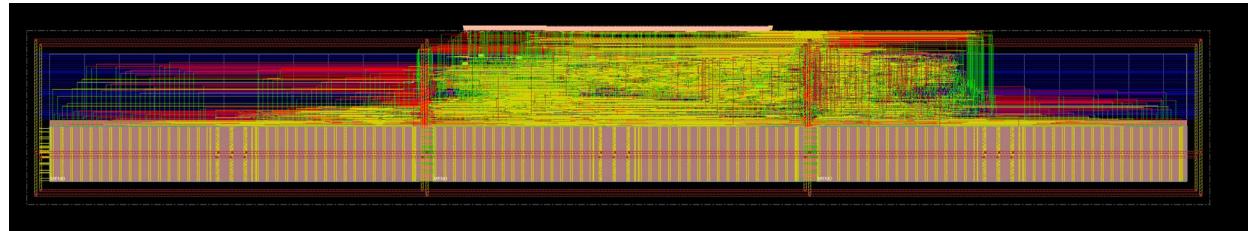

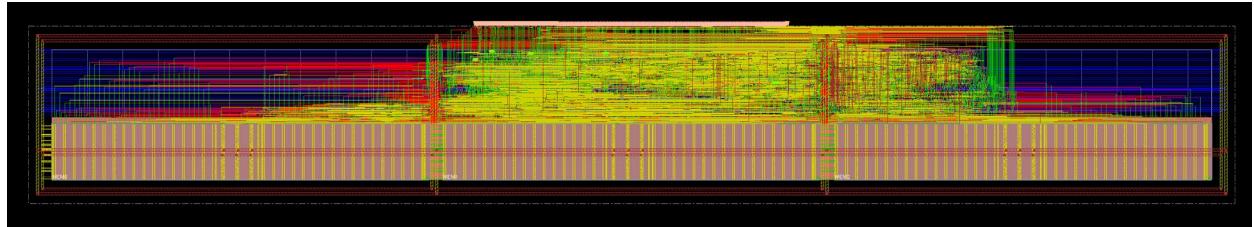

7. Note that we did build a quite small SRAM memory. Compare the layout of the 16x64 , 32x64 and 64x64 SRAM memories.

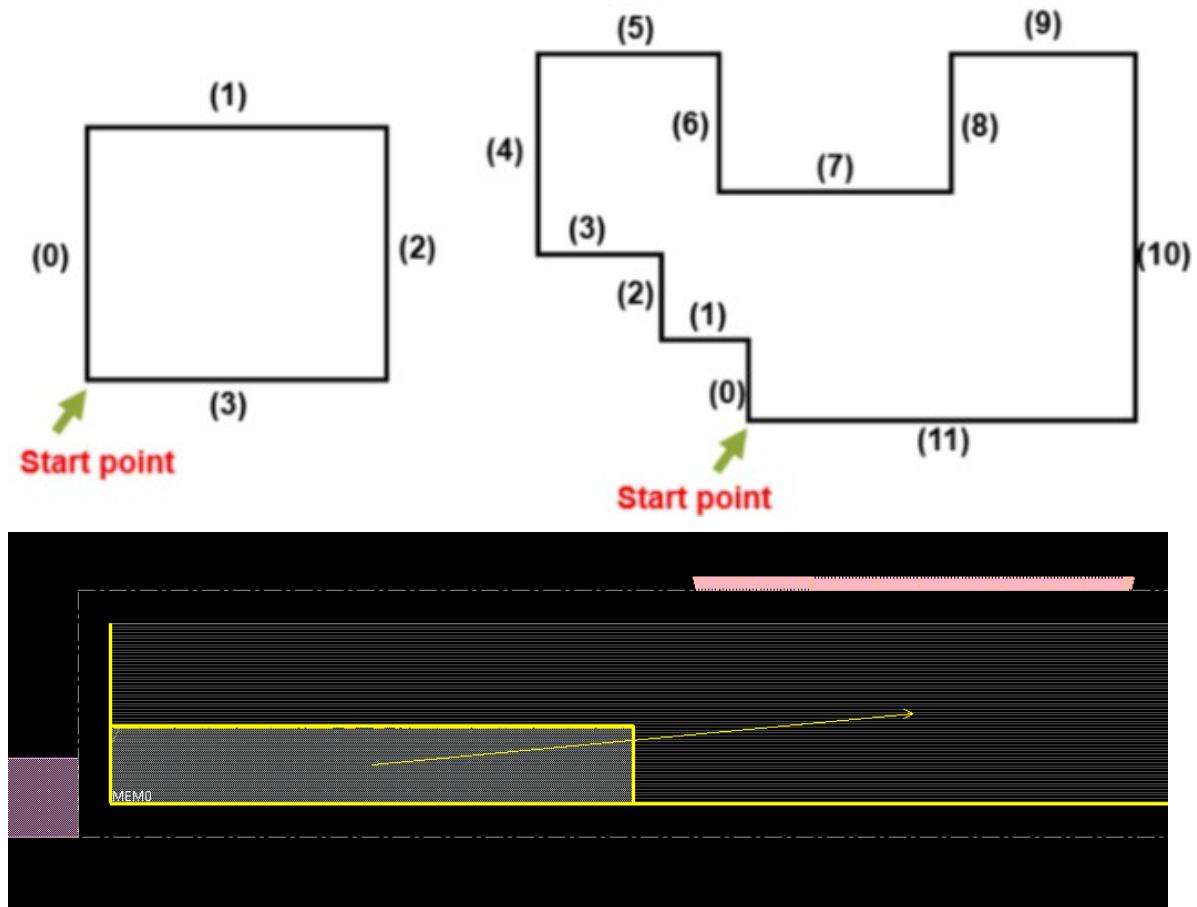

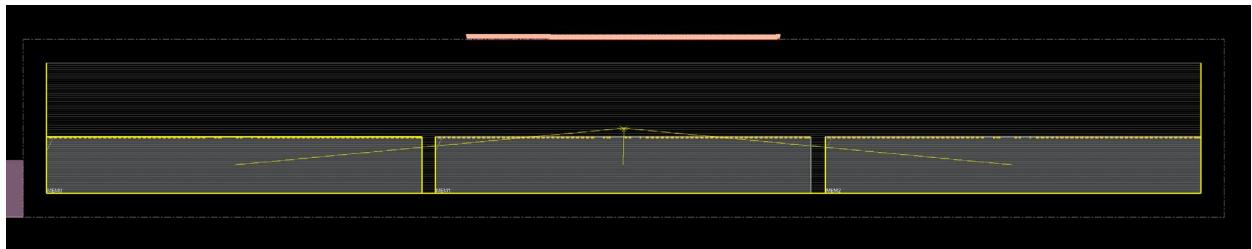

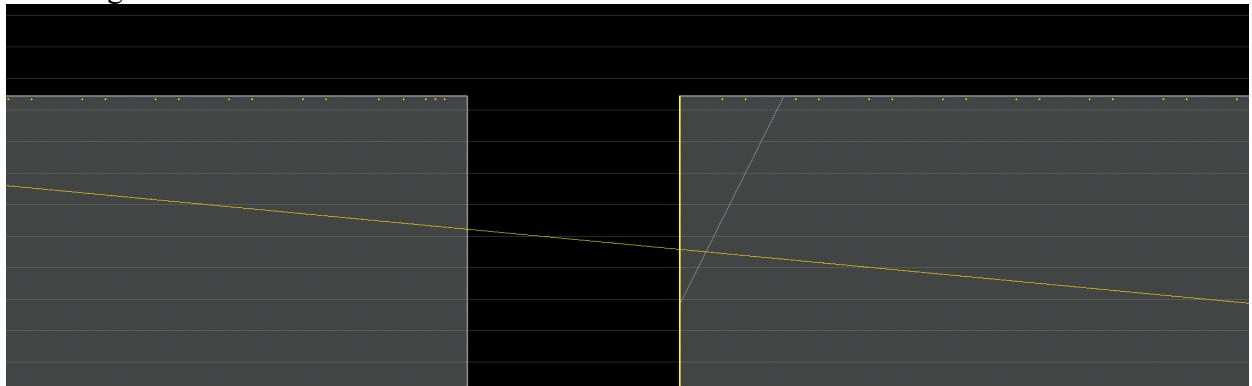

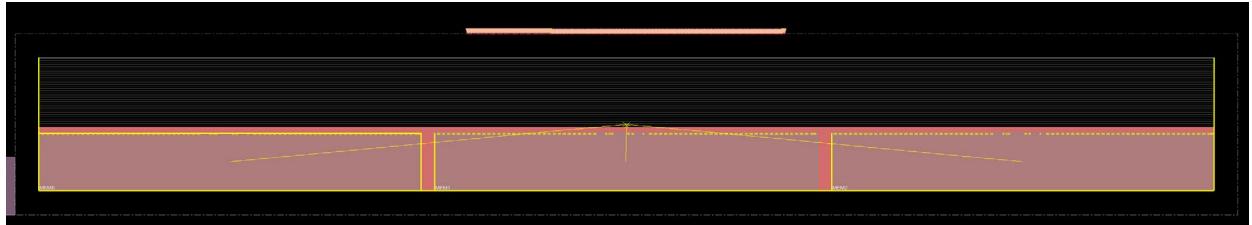

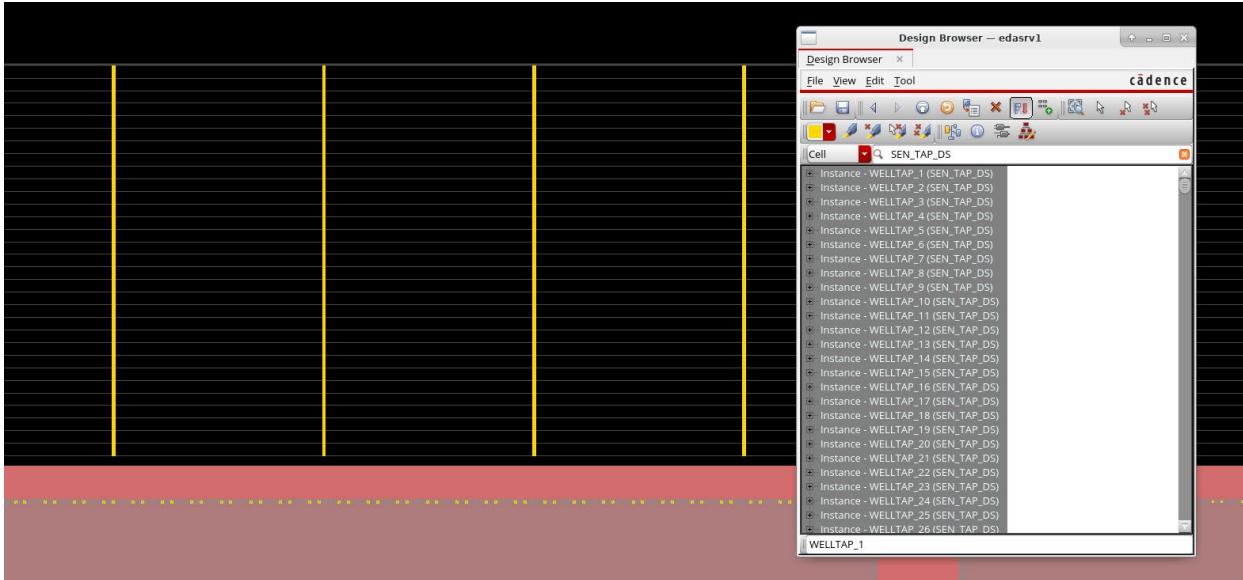

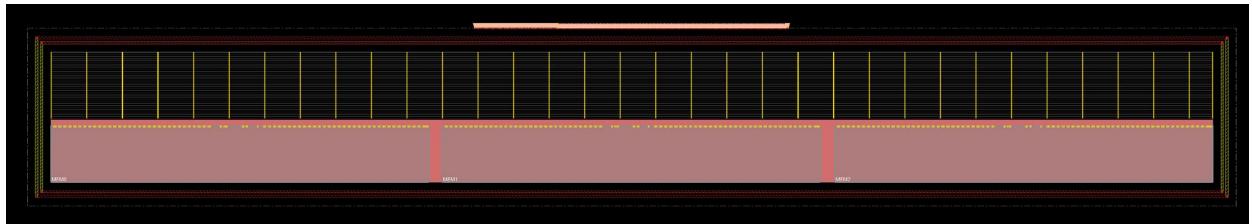

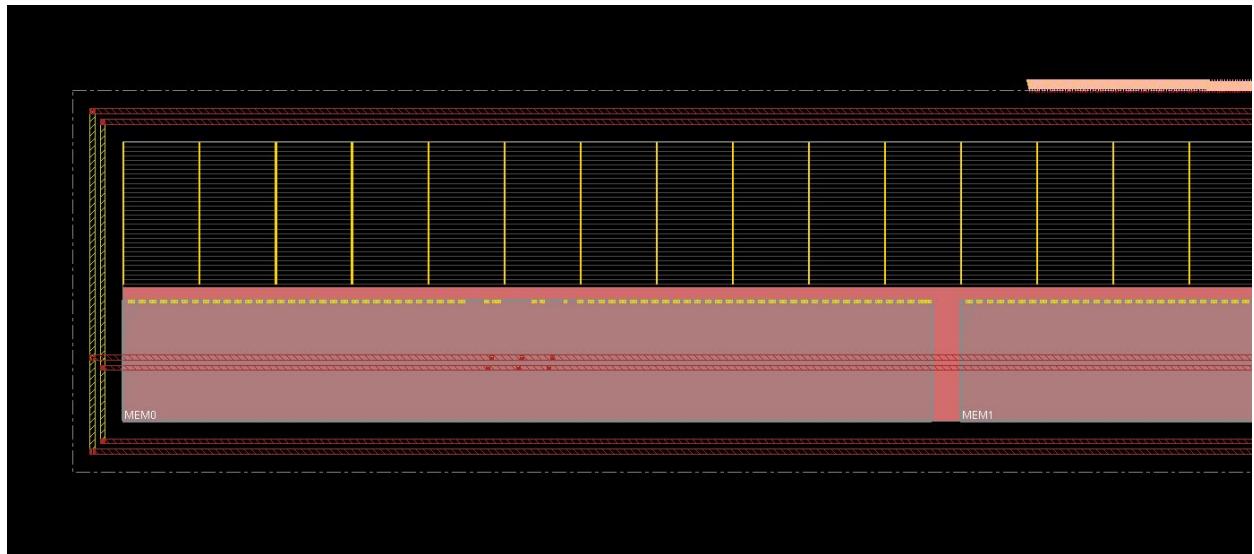

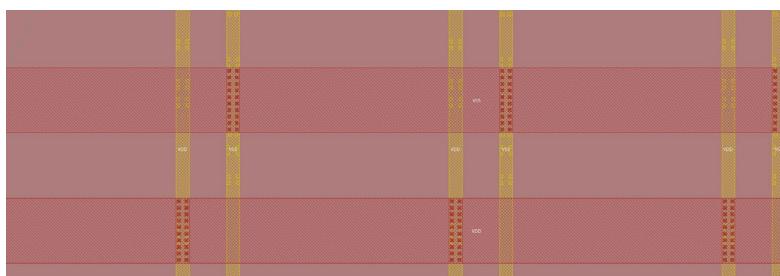

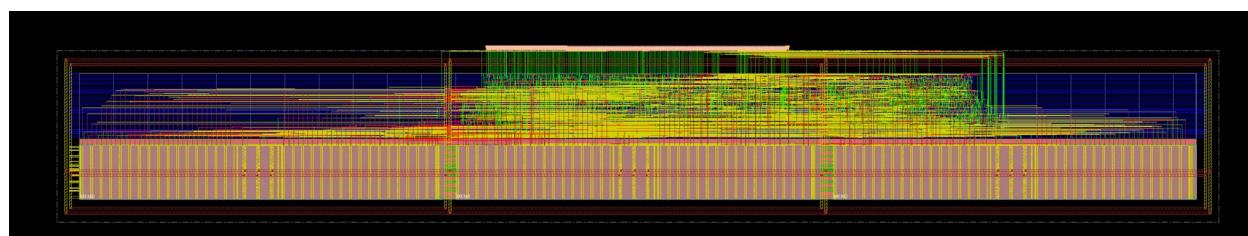

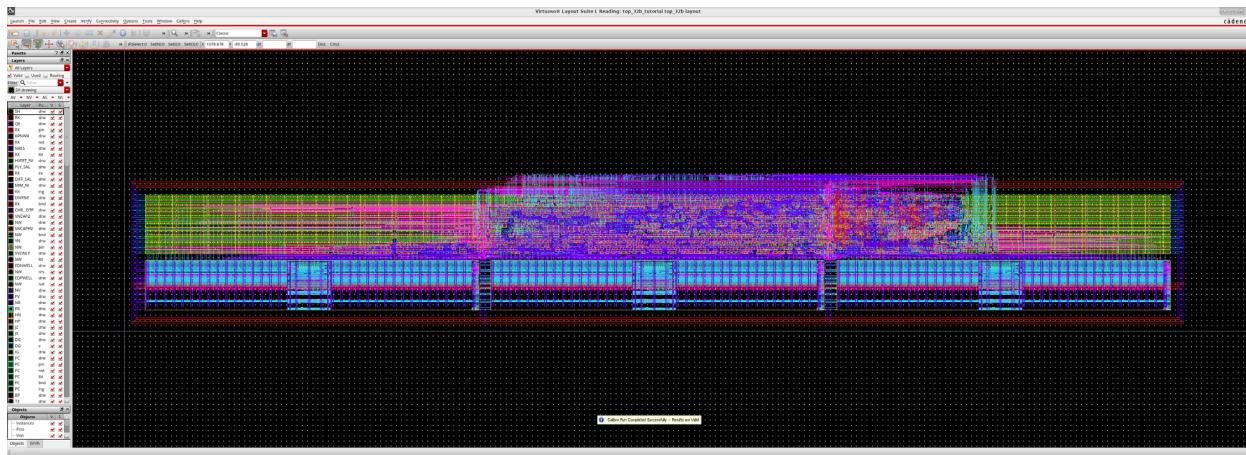

In the screenshots, the highlighted area in red is the actual subarray.

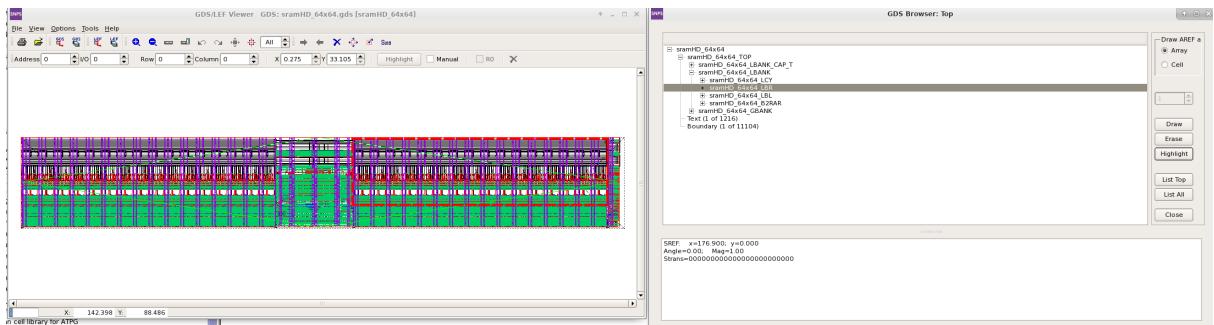

8. Keep the 64x64 GDS opened, and click in the button to open the hierarchy of the GDS.

9. Put side-to-side the gds viewer and the gds browser. And dive in the hierarchy.

10. Click on + on sramHD\_64x64 then on sramHD\_64x64\_TOP

11. Alternatively select the three blocks inside sramHD\_64x64\_TOP and click on Highlight.

**i** If you click on Erase by mistake, you select back the top cell and click on Draw to print it back.

12. Find the actual memory array.

13. Find a bitcell and zoom in it.

QUESTION 2-4: measure approximatively the size of the bitcell using the ruler. Units for the ruler are in um.

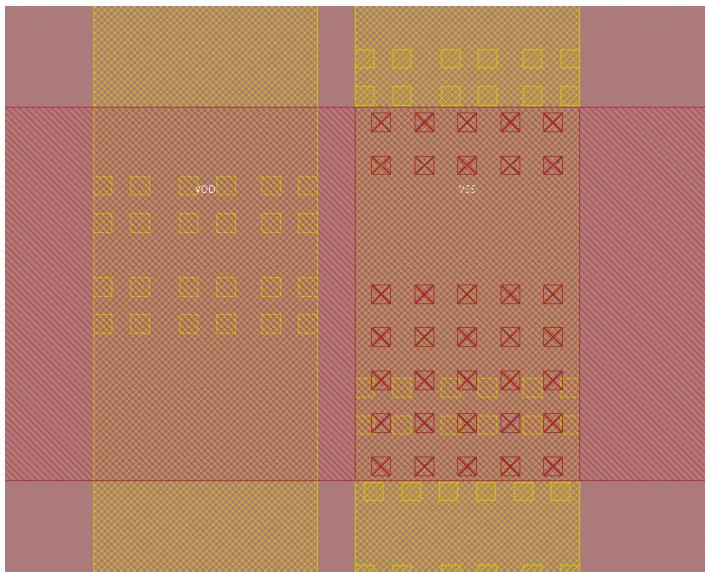

QUESTION 2-5 : The view of the bitcell is layout, as we did in phase 1. From the layout of one bitcell, by only representing the layers as described in the next comment, infer the schematic of the bitcell and draw it in your report. Are there things you see in this layout which seem to break the DRC rules you had to respect in the layout of phase 1 ?

**i** You can use the GDS layer button to enable/disable layers in order to ease the view. You could for e.g. order the layer by DT and only keep CON1, POLY, M1 NWELL and ALLDIFF visible. Note the layer called CAREC which is the special layer used for rectangular contacts in this technology. Add the layer CAREC as well.

① You can add and remove layers by ticking them in the “GDS Layers” panel accessible

through the  button. To remove all the layers press  then . Then tick the layers you want to add, and press *Apply* again.

② The N WELL layer sometimes stays over the rest, so try adding it and removing it to identify where the PMOS are.

③ Orders of magnitude for the size of an SRAM cell in this technology node can be found in [https://en.wikichip.org/wiki/65\\_nm\\_lithography\\_process](https://en.wikichip.org/wiki/65_nm_lithography_process)

Here is a screenshot of the bitcell, with one way to access one bitcell in the hierarchy, and one example of GDS layers panel with M1 Con1 Poly and CAREC activated. Here you would like to add ALLDIFF to find the transistors.

Once you are done, you can for now close integrator.

QUESTION 2-6 : Now that you have played with a memory compiler. Comment on the memory size you have been using. Considering the area ratio inside the memories you generated. Does it make sense to use this family of SRAM memories for such a small memory array?

### 3. MAKE YOUR DESIGN READY FOR A SRAMHD\_16x64 MEMORY

Let's now solve the memory area bottleneck problem by replacing the sramHD\_64x64 from the top\_32b block, by a sramHD\_16x64.

#### 3.1. MODIFY THE TOP\_32B

Let's modify the top\_32b to have a version of it ready for future explorations.

- With your terminal move to the HDL/RTL/

- Make a copy of the file top\_32b.vhd

```

> cp top_32b.vhd top_32b_16x64bitMEM.vhd

```

- Open the newly created top\_32b\_16x64bitMEM.vhd with gedit or any text editor of your choice. Modify lines 159 to 191 in the following way :

```

MEM0 : component sramHD_16x64

```

```

port map (

Q    => data_out_memo,

ADR   => addr_memo(3 downto 0),

D    => data_in_memo,

WE   => we_memo,

ME   => en_memo,

CLK   => clk,

TEST1 => '0',

RME   => '0',

RM    => (others => '0'));

MEM1 : component sramHD_16x64

port map(

Q    => data_out_mem1,

ADR   => addr_mem1(3 downto 0),

D    => data_in_mem1,

WE   => we_mem1,

ME   => en_mem1,

CLK   => clk,

TEST1 => '0',

RME   => '0',

RM    => (others => '0'));

MEM2 : component sramHD_16x64

port map(

Q    => data_out_mem2,

ADR   => addr_mem2(3 downto 0),

D    => data_in_mem2,

WE   => we_mem2,

ME   => en_mem2,

CLK   => clk,

TEST1 => '0',

RME   => '0',

RM    => (others => '0'));

```

#### 4. Save the file and close it.

You should also update the alu32\_pkg.vhd file as it does contain definitions of memories for the simulation.

1. Open the file alu32\_pkg.vhd

2. Add the following lines before line 85 as already done in the file for the sramHD\_32x64.

```

component sramHD_16x64

port(

Q      : out std_logic_vector (63 downto 0);

ADR   : in std_logic_vector (3 downto 0);

D      : in std_logic_vector (63 downto 0);

WE    : in std_logic;

ME    : in std_logic;

CLK   : in std_logic;

TEST1 : in std_logic;

RME   : in std_logic;

RM    : in std_logic_vector (3 downto 0));

end component sramHD_32x64;

```

#### 3. Save and close the file

## 3.2. COMPILE THE LIB INTO A DB FILE

Before proceeding with logic synthesis, you must generate the db for your memory. This step is needed as designCompiler does not understand liberty files, and requires the lib file to be compiled

in a db file. Also, Embedit does not generate db files for you, so you need to generate them using a tool called LibraryCompiler and its command line : lc\_shell

1. Go in the LibraryCompiler folder

2. Run >lc\_shell

3. Run the following commands :

```

lc_shell>                                         read_lib

..../EMBEDIT/EDALABS/compout/views/sramHD_16x64/ss1p08v125c/sramHD_16

x64.lib

```

❶ *The tool will read the lib file and check its syntax. As the lib file has been generated by a tool, you may want to read the warnings it does issue, though, at this point there is not much you can do. Identifying errors, info and warnings generally gives you insights on the quality and age of the model you deal with.*

❷ *It should finish by Technology library 'sramHD\_16x64.lib' read successfully*

```

lc_shell> write_lib sramHD_16x64.lib -format db -output

..../EMBEDIT/EDALABS/compout/views/sramHD_16x64/ss1p08v125c/sramHD_16

x64.db

Wrote the 'sramHD_16x64.lib' library to

'..../EMBEDIT/EDALABS/compout/views/sramHD_16x64/ss1p08v125c/sramHD_16x64.

db' successfully

```

Once you are done,

```

lc_shell> exit

Maximum memory usage for this session: 127.71 MB

CPU usage for this session: 2 seconds ( 0.00 hours)

Elapsed time for this session: 571 seconds ( 0.16 hours)

Thank you for using Library Compiler.

```

Thank you...

Now, you have your db file ready for when you want to run a synthesis with this new memory size. At this point, when this is needed, it will be your duty to update the tcl script with the path to this new IP.

You could, for e.g., run the following command, to copy this new sramHD\_16x64 folder in your IP/Memories folder (in this example, we run it from the LibraryCompiler folder):

```

>cp -r ..../EMBEDIT/EDALABS/compout/views/sramHD_16x64 ..../IPS/MEMORIES/

```

## 4. PLACE AND ROUTE THE MAPPED DESIGN WITH INNOVUS

In this step, you will learn how to place the synthesized design from DesignCompiler. Here, you should take a design that you generated in the previous step. The Verilog and SDC files should be taken from the SDC and RTL/GATE/ folders.

**IMPORTANT DISCLAIMER :** from 2020, Cadence released a new syntax for their tools, called Stylus (or Common UI). This User Interface (UI) replaces what's called Legacy UI. This disclaimer is important for two reasons :

- 1- If you had experience in the past with Innovus, you did most likely learn legacy UI. Switching to Common UI will require a bit of gymnastics, but is an investment for the future, as from now on, only Common UI will be formally supported by Cadence.

- 2- If you go in a company, any flow developed before 2020 will most likely still use Legacy UI. It is important to be aware that these two UI will continue to co-exist.

In practice :

- 1- Some commands are discontinued between legacy and common

- 2- Some new commands have been introduced

- 3- Syntax has been homogenized between all cadence tools

- a. Example of Legacy command :

```

globalNetConnect VDD -type pgpin -pin VDD -inst *

```

b. example of Common UI command :

```

connect_global_net VDD -type pgpin -pin VDD -inst *

```

- 4- Even in the 2022 version of Innovus , the GUI does not fully support yet Common UI. Which means... we will not use the GUI commands in this lab ! (it's a good thing, trust me)

For the curious you, on moodle you will find a documentation called “Translation of Innovus Legacy UI Commands into Common UI (CUI) Commands” and which proposed examples of how to translate a flow from Legacy to Common UI.

## 4.1.BEFORE STARTING

Innovus, as DesignCompiler, is an EXTREMELY COMPLEX tool. It does take commands through the terminal, and has, as expected, a long documentation which you would be expected, as a designer, to dive through.

To cope with that, besides the translation guide, we also provide the following documentation on moodle :

- The “*Innovus Stylus Common UI Text Command Reference*” which contains the details of all the commands used in innovus

- The “*Innovus Stylus Common UI User Guide*” which helps you selecting the good commands, and gives insights on how to use innovus and the UI.

For reference, the user guide is 2000+ pages and the command reference is 5000+ pages. Not something you would read before sleeping, though it can be extremely helpful during your designs.

## 4.2.STARTING INNOVUS

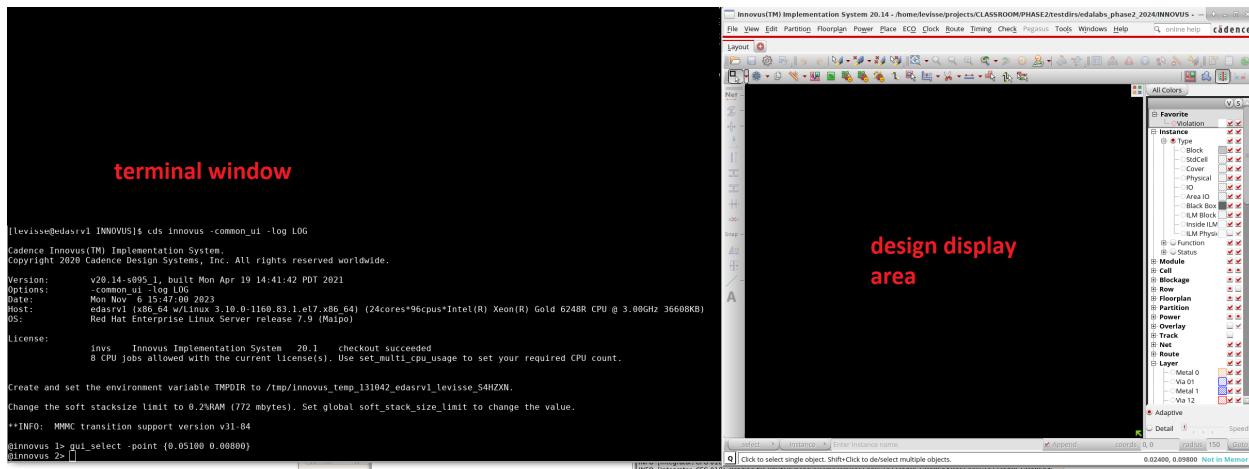

To start the Innovus tool, go to the INNOVUS directory and run the innovus command:

```

> cd INNOVUS

> innovus -common_ui -log LOG

```

The `-log` option redirects all log files to the `LOG` directory. Three log files are created: the file `innovus.cmd` records all entered commands and the files `innovus.log` and `innovus.logv` contain the respectively compact and verbose session logs.

Two things happen. The terminal becomes a `@innovus>` command line as it did with `dc_shell`. A window called Innovus Implementation System appears. You'll notice that this window looks a lot like virtuoso.

**① Make the Innovus console terminal large and visible enough, so you can better monitor what is happening during the place and route steps.**

The design display area includes three different *design views* that you can toggle during a session (from left to right): the **Floorplan** view, the **Amoeba** view, and the **Physical** view:

- The Floorplan view displays the hierarchical module and block guides, connection flight lines, and floorplan objects, including block placement, and power/ground nets.

- The Amoeba view displays the outline of the modules and submodules after placement, showing physical locality of the module.

- The Physical view displays the detailed placements of the module's blocks, standard cells, nets, and interconnects.

When the AutoQuery box is enabled, the properties of the object below the cursor are automatically displayed.

There are a number of *binding keys* available (hit the key when the Innovus GUI is active). Some useful binding keys:

| Binding key | Action                                                                                                                                                             |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b           | display the list of binding keys                                                                                                                                   |

| d           | (de)select or delete objects                                                                                                                                       |

| f           | zoom the display to fit the core area                                                                                                                              |

| k           | create a ruler                                                                                                                                                     |

| K           | remove last ruler displayed                                                                                                                                        |

| q           | display the object attribute editor form for the selected object<br>click the left-button mouse to select an object<br>shift-click to select or deselect an object |

| u           | undo the last command                                                                                                                                              |

| U           | redo the last command                                                                                                                                              |

| z           | zoom-in 2x                                                                                                                                                         |

| Z           | zoom-out 2x                                                                                                                                                        |

| Arrows      | pan the display                                                                                                                                                    |

| CTRL+R      | refresh the display                                                                                                                                                |

### 4.3. REQUIRED DATA

A number of specific data must be available or defined before using the Innovus tool.

- **Physical libraries**

This includes information on the technology process to be used (routing layers (kind (metal, poly), name, pitch, and spacing), via/cut cells, core and pad site definitions, legal placement orientations) and abstract<sup>8</sup> information for every standard macro cell (type of site (core, pad, etc.), bounding box size, pins (name, kind, size, and position), blockages (routing obstructions)).

Physical libraries are provided by a foundry or an IP provider as LEF ([Library Exchange Format](#)) files<sup>9</sup>. LEF files have the `.lef` extension. There could be two LEF files, one for the technology process and one for the macro cells, or a single one including both aspects.

- **Timing libraries**

This includes the timing information for all macro cells (path delays, setup/hold times, etc.) and for various PVT (process/voltage/temperature) corners. Timing libraries will be used in the so-called *BC-WC (best case - worst case) timing analysis mode*: max/worst-case (resp., min/best-case) timing libraries are used for verifying setup (resp., hold) time

---

<sup>8</sup> The place and route does not need full geometrical layouts. i.e., you can work with LEF files and not gds as inputs.

<sup>9</sup> The Innovus help provides a LEF language reference.

constraints.

These libraries are the same as the ones used by DesignCompiler synthesizer, but here in the *Liberty* text (.lib) format. As opposed to designCompiler, innovus does not need the lib files to be compiled in db.

- **Parasitics extraction data**

This includes technological data required to extract actual parasitics (RC) values for wires in the design. There could either be capTables (.capTbl) or directly extracted from the technology files (qrcTechFile). Generally nodes older than 65 would rely on captables while more advanced nodes will consider the more precise qrc files.

- **Gate-level netlist**

This is the netlist to be placed and routed defined as a Verilog (.v) file. The file has been generated during logic synthesis and is placed in the HDL/GATE folder.

- **Timing constraints**

This relates to the constraints used in logic synthesis. A .sdc constraint file has been generated at that step that can be used, although only timing commands (clock specification, timing delays) are supported.

The SDC file generated in synthesis defines typical conditions. Place and route allows you more optimization through buffer insertion and clock tree synthesis, thereby, you could overconstrain the required timings by, say, 10%, to exploit possible further timing optimizations during place and route. We propose you one way to do it at the end of section.

## 4.4.DEFINING YOUR DESIGN ENVIRONMENT

The first step to do, as for designCompiler, is to define the working environment.

In the cadence environment, this is called the view definition, and it does define what's called the MMMC, i.e., Multi Mode Multi Corner.

1. Go in the INNOVUS/BIN/ folder and find the “default\_mmmc.view” file.

2. You will find also a copy of this file identified with the features of your design : svt, mem64, 4.5ns top32\_mmmc\_svt\_mem64\_4p5ns.view

3. Open this file with a text editor

```

>gedit top32_mmmc_svt_mem64_4p5ns.view

```

We define this file for you already as it can be a bit complex to setup. Though, you must understand it as you will need to update it in order to use it.

Disclaimer. As usual, there is no absolute rule on how to deal with scripts in IC design. Here, we propose to use a MMMC template which have been used in EPFL for circuit design projects.

The approach described in this section is quite hierarchical and allows for some flexibility when adding or removing corners. Indeed, it becomes easy to add a new standard cell library, a new corner, or a new constraint file.

#### 4.4.1. DEFINITION OF THE TECHNOLOGY CORNERS

first check lines 12 to 15

```

set      cap_tbl(rcbest)          /dkits/gf/65nm/65LPe/pdk/65LPe/PEX/QRC/EDA-CAD-65N-

EX038/Rev9/cmos10lpe_6_00_01_00_LB/cmos10lpe_FuncCmin_6_00_01_00_LB_effective/qrc

TechFile

set      cap_tbl(rcworst)         /dkits/gf/65nm/65LPe/pdk/65LPe/PEX/QRC/EDA-CAD-65N-

EX038/Rev9/cmos10lpe_6_00_01_00_LB/cmos10lpe_FuncCmax_6_00_01_00_LB_effective/qrc

TechFile

set      cap_tbl(typical)        /dkits/gf/65nm/65LPe/pdk/65LPe/PEX/QRC/EDA-CAD-65N-

EX038/Rev9/cmos10lpe_6_00_01_00_LB/cmos10lpe_nominal_6_00_01_00_LB_effective/qrcT

echFile

set cap_tables {rcworst rcbest typical}

foreach rc $cap_tables {

create_rc_corner -name corner_${rc} \

-qrc_tech $cap_tbl($rc) \

-T {25}

}

```

Here we first define the technology files for the metal levels. Note that relative paths are not supported by the view files.

Note that we use the qrcTechFile which is a compiled version of the parasitic. This file can also be used for parasitic extraction in virtuoso.

**QUESTION 4-1 : what do these 3 corners correspond to ?**

#### 4.4.2. DEFINITION OF THE IPS CORNERS

check lines 30 to 32

```

set lib_std(wc)

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/s

vt/5.00a/liberty/ccs/cp65npksdst_ss1p08v125c.lib

set lib_std(bc)

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/s

vt/5.00a/liberty/ccs/cp65npksdst_ff1p32vn40c.lib

set lib_std(tc)

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/s

vt/5.00a/liberty/ccs/cp65npksdst_tt1p2v25c.lib

```

Here we define the three corners for the standard cell library with the svt flavour as used during synthesis. If you intend to use lvt and hvt, you would need to add them there.

Check lines 37 to 39

```

set lib_mem(wc)  ../IPS/sramHD_64x64/ss1p08v125c/sramHD_64x64.lib

set lib_mem(bc)  ../IPS/sramHD_64x64/ff1p32vn40c/sramHD_64x64.lib

set lib_mem(tc)  ../IPS/sramHD_64x64/tt1p2v25c/sramHD_64x64.lib

```

Same as for the standard cells, we define here the lib file corresponding to the sramHD\_64x64 memory.

Then, lines 42 to 48 the lib files are being clustered together per corner in a library set.

```

set libsets {wc bc tc}

foreach libset $libsets {

create_library_set -name libset_${libset} -timing [list \

$lib_std($libset) \

$lib_mem($libset)

]

}

```

#### 4.4.3. DEFINITION OF THE CONSTRAINTS

Here we import the SDC file containing the design constraints. This is where the clock is being defined for e.g. The design constraints are being matched to all the libsets defined before. i.e., here we define a single constraint mode for all the corners.

Line 54 to 56

```

foreach libset $libsets {

create_constraint_mode -name constraint_${libset} -sdc_files

{../DesignCompiler/SDC/DATE/TIME/postSynthesis_svt_clk_4.5.sdc}

}

```

**Here you are expected to update the XXXX and DATE/TIME to match with the one of your design.** Also make sure that the SDC file name matches.

#### 4.4.4. DEFINE THE DELAY CORNERS

Then we match the capacitance corners defined before, with the timing conditions from the standard cell libraries.

Line 58 to 71

```

foreach libset $libsets {

create_timing_condition -name timing_condition_${libset} -

library_sets [list libset_${libset}]

}

set cap_map {rcworst rcbest typical}

# association of the capacitance corners (called cap_map) with the

# timing conditions and constraints in the delay corner

foreach libset $libsets rc $cap_map {

create_delay_corner -name delay_corner_${libset} \

-early_timing_condition [list timing_condition_${libset}] \

-late_timing_condition [list timing_condition_${libset}] \

-early_rc_corner corner_${rc} \

-late_rc_corner corner_${rc}

}

```

#### 4.4.5. DEFINITION OF THE HOLD AND SETUP VIEWS

First we define the name of the variables being used. Note that here, we associate the hold corner to bc only and the setup corner to wc only.

Here, one may want to define much more than only 1 corner per check. Various voltages, temperatures could make sense to be added. In some conditions temperature inversion effects force the designers to add more than one corner.

Line 77 to 81

```

set hold_lib_corners {bc}

set setup_lib_corners {wc}

set setup_views {}

set hold_views {}

```

QUESTION 4-2: why is the BC corner (ff, 1.32V, -40C) being used in the hold view ?

QUESTION 4-3 why is the WC corner (ss, 1.08V, -125C) being used in the setup view ?

From line 83 to 102

```

# for each hold_lib_corner we define an analysis view called

analysis_hold_${corner}

foreach corner $hold_lib_corners {

create_analysis_view -name analysis_hold_${corner} \

-constraint_mode constraint_${corner} \

-delay_corner delay_corner_${corner}

lappend hold_views analysis_hold_${corner}

}

# for each setup_lib_corner we define an analysis view called

analysis_setup_${corner}

foreach corner $setup_lib_corners {

create_analysis_view -name analysis_setup_${corner} \

-constraint_mode constraint_${corner} \

-delay_corner delay_corner_${corner}

lappend setup_views analysis_setup_${corner}

}

# we define the set_analysis_view and associate setup_views to -setup

# and hold_views to -hold

# this approach is extremely scalable and allows for the definition

# of a large range of corners used during hold and setup.

# for the example given here, it could seem like a bit of overdoing

# though.

set_analysis_view -setup $setup_views \

-hold $hold_views

```

We now define the views to be considered during hold and setup checks.

## 4.5. IMPORT THE MMMC AND INITIALIZE THE DESIGN ENVIRONMENT

### 4.5.1. IMPORT THE MMMC

First we want to import the MMMC file which we just read. Let's import it and check the corresponding logs.

```

Innovus > read_mmmc BIN/top32_mmmc_svt_mem64_4p5ns.view

Note that innovus does read the commands you import starting them with a @

#@ Begin verbose source (pre):

@file 1: # Version:1.0 MMMC View Definition File

@file 2: # Do Not Remove Above Line

@file 3: #this script has been written and prepared by Alexandre Levisse in oct2023 -

alexandre.levisse@epfl.ch

@file 4: #this script is designed as an example for the labs on EDA for innovus.

@file 5: #feel free to use it as a basis for your designs in EPFL

```

```

@file 6:

@file 7: # mmmc files do not accept relative paths, thereby, in the rest of the file, the

paths are using EPFL's edadk file organization. feel free to update them with your environment.

@file 8: # definition of the technology corners

@file 9: # here the qrcTechFile is being used. One could use a capTable in 65nm if available

- not available for this technology

@file 10: # definition of the different metal corners through variables

@file 11: # 3 corners are being selected rcbest, rcworst and typical.

...

}

@file 97:

@file 98: # we define the set_analysis_view and associate setup_views to -setup and hold_views

to -hold

@file 99: # this approach is extremely scalable and allows for the definition of a large range

of corners used during hold and setup.

@file 100: # for the example given here, it could seem like a bit of overdoing though.

@file 101: set_analysis_view -setup $setup_views \

-hold $hold_views

#@ End verbose source: BIN/top32_mmmc_svt_mem64_4p5ns.view

```

**Until this point innovus was simply reading and printing the file**

```

Reading                                libset_wc          timing          library

'/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp

65nplksdst_ss1p08v125c.lib' ...

**WARN: (TECHLIB-302):      No function defined for cell 'SEN_TIEDIN_1'. The cell will only

be           used           for           analysis.          (File

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp6

5nplksdst_ss1p08v125c.lib)

...

**WARN: (TECHLIB-302):      No function defined for cell 'SEN_DCAP32'. The cell will only

be           used           for           analysis.          (File

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp6

5nplksdst_ss1p08v125c.lib)

**WARN: (TECHLIB-302):      No function defined for cell 'SEN_DCAP16'. The cell will only

be           used           for           analysis.          (File

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp6

5nplksdst_ss1p08v125c.lib)

```

**Here innovus complains about some cells not having a defined logic functionality. Think about what TIE cells and DCAP cells are. Does that make sense ?**

```

**WARN: (TECHLIB-1435):      For dc_current table defined in cell 'SEN_FDNRBSBQ_2' and pin

'Q', the current values are not monotonically decreasing in the range '-0.00339' to '-0.003388'

for           'input_voltage'           '0.702000'.          (File

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp6

5nplksdst_ss1p08v125c.lib, Line 4281393)

**WARN: (TECHLIB-1435):      For dc_current table defined in cell 'SEN_FDNRBSBQ_2' and pin

'Q', the current values are not monotonically decreasing in the range '-0.005477' to '-0.005426'

for           'input_voltage'           '0.756000'.          (File

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp6

5nplksdst_ss1p08v125c.lib, Line 4281393)

**WARN: (TECHLIB-1435):      For dc_current table defined in cell 'SEN_FDNRBSBQ_2' and pin

'Q', the current values are not monotonically decreasing in the range '-0.007974' to '-0.007907'

for           'input_voltage'           '0.810000'.          (File

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp6

5nplksdst_ss1p08v125c.lib, Line 4281393)

...

**WARN: (TECHLIB-1435):      For dc_current table defined in cell 'SEN_EO3_6' and pin 'X',

the current values are not monotonically decreasing in the range '-0.231' to '0.1281' for

'output_voltage'           '0.486000'.          (File

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp6

5nplksdst_ss1p08v125c.lib, Line 4022900)

**WARN: (TECHLIB-1435):      For dc_current table defined in cell 'SEN_EO3_6' and pin 'X',

the current values are not monotonically decreasing in the range '-0.2372' to '0.1214' for

'output_voltage'           '0.540000'.          (File

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp6

5nplksdst_ss1p08v125c.lib, Line 4022900)

Message <TECHLIB-1435> has exceeded the message display limit of '20'. Use 'set_message -

no_limit -id list_of_msgIDs' to reset the message limit.

```

**Some more complains about some device definition in the lib file. At this point you can ignore these. Though remember that in real life, you must**

make sure that you understand what all the warnings mean. Because otherwise you could be in a situation where your results are incorrect because of some wrong assumption taken by the tool

```

Read 1128 cells in library 'cp65npksdst_ss1p08v125c'

Reading libset_wc timing library

'/home/levisse/projects/CLASSROOM/PHASE2/testdirs/edalabs_phase2_2024/IPS/sramHD_64x64/ss1p

08v125c/sramHD_64x64.lib' ...

Read 1 cells in library 'sramHD_64x64.lib'

```

Here Innovus acknowledges the read of the stdcells and memories defined in the mmmc file for the libset\_wc case.

Then it does the same for libset\_bc

```

Reading libset_bc timing library

'/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp

65npksdst_ff1p32vn40c.lib' ...

**WARN: (TECHLIB-302): No function defined for cell 'SEN_TIEDIN_1'. The cell will only

be used for analysis. (File

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp6

5npksdst_ff1p32vn40c.lib)

**WARN: (TECHLIB-302): No function defined for cell 'SEN_DCAP8'. The cell will only be

used for analysis. (File

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp6

5npksdst_ff1p32vn40c.lib)

**WARN: (TECHLIB-302): No function defined for cell 'SEN_DCAP64'. The cell will only be

used for analysis. (File

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp6

5npksdst_ff1p32vn40c.lib)

**WARN: (TECHLIB-302): No function defined for cell 'SEN_DCAP4'. The cell will only be

used for analysis. (File

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp6

5npksdst_ff1p32vn40c.lib)

**WARN: (TECHLIB-302): No function defined for cell 'SEN_DCAP32'. The cell will only be

used for analysis. (File

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp6

5npksdst_ff1p32vn40c.lib)

**WARN: (TECHLIB-302): No function defined for cell 'SEN_DCAP16'. The cell will only be

used for analysis. (File

/dkits/synopsys/DesignWare_logic_libs/commonplatform65nlp/hd/base/svt/5.00a/liberty/ccs/cp6

5npksdst_ff1p32vn40c.lib)

Read 1128 cells in library 'cp65npksdst_ff1p32vn40c'

Reading libset_bc timing library

'/home/levisse/projects/CLASSROOM/PHASE2/testdirs/edalabs_phase2_2024/IPS/sramHD_64x64/ff1p

32vn40c/sramHD_64x64.lib' ...

Read 1 cells in library 'sramHD_64x64.lib'

timing_initialized

```

QUESTION 4-4: Why do TIE and DCAP cells not have logic behaviour ? what are these cells doing ?

#### 4.5.2. IMPORT THE PHYSICAL FOOTPRINT OF THE IPs BEING USED

Before starting the design we need to tell innovus the physical shape of all the cells.

In other words :

- The physical footprint of the standard cells and memory : area and shape

- Where are the pins located : inputs, outputs, vdd, grounds (cf what you did in the layout)

- How large are the pins

Though, for this, we do not use the GDS file, but a simplified version of it, inside a file called LEF.

- ❶ One of the reasons for using a LEF file instead of the GDS is that it allows to only show the interface pins. This is of value for companies which do not want to share the details of their design to their users.

- ⓘ The second reason is that lef files are much lighter and more efficient to handle.

Note that besides the lef file for cp65npkstdt you also import a file with a reference to m06f0f1. This is called the tech LEF. It does contain a simplified version of the DRC for a given metal stack (here we use m06f0f1), so that innovus knows how to connect wires.

- ⓘ For some reason, the lef file of the sramHD is called plef for physical LEF, but this does not have any impact in your design.

```

Innovus > read_physical -lef

{../IPS/STDCELLS/hd/base/svt/latest/lef/5.6/cp65npksdst_m06f0f1.lef

../IPS/STDCELLS/hd/base/svt/latest/lef/5.6/cp65npksdst.lef

../IPS/MEMORIES/sramHD_64x64/sramHD_64x64.plef}

```

```

Loading LEF file ../IPS/hd/base/svt/latest/lef/5.6/cp65npksdst_m06f0f1.lef ...

**WARN: (IMPLF-122): The direction of the layer 'M2' is the same as

the previous routing layer. Make sure this is on purpose or correct

the direction of the layer. In most cases, the routing layers

alternate in direction between HORIZONTAL and VERTICAL.

```

**Note how innovus reads about the routing directions.**

```

Loading LEF file ../IPS/hd/base/svt/latest/lef/5.6/cp65npksdst.lef ...

Set DBUPerIGU to M2 pitch 400.

```

```

Loading LEF file ../IPS/sramHD_64x64/sramHD_64x64.plef ...

WARNING (LEFPARS-2007): NAMESCASESENSITIVE statement is obsolete in version 5.6 and

later.

The LEF parser will ignore this statement.

To avoid this warning in the future, remove this statement from the LEF file with

version 5.6 or later. See file ../IPS/sramHD_64x64/sramHD_64x64.plef at line 39.

```

**This warning comes from the memory compiler and can be ignored**

```

**WARN: (IMPLF-200): Pin 'X' in macro 'SEN_TIEDIN_1' has no ANTENNAGATEAREA

value defined. The library data is incomplete and some process antenna rules will

not be checked correctly.

Type 'man IMPLF-200' for more detail.

```

**This warning means that in the standard cell library, the cell SEN\_TIEDIN\_1 does not have some antenna protection on one of its outputs. This could lead to errors in DRC later on. At this point there is nothing we can do about it as this was designed by the IP provider, but it's a good example of something to be aware of.**

```

viaInitial starts at Tue Nov 7 11:54:22 2023

viaInitial ends at Tue Nov 7 11:54:22 2023

## Check design process and node:

## Both design process and tech node are not set.

```

### 4.5.3. READ THE POST SYNTHESIS NETLIST

```

Innovus> read_netlist -top top_32b

../../../HDL/GATE/XXXXXX/postSynthesis_svt_clk_4.5.v

```

**Update the XXXX with the path to your netlist**

```

#% Begin Load netlist data ... (date=11/07 13:21:19, mem=646.5M)

```

```

*** Begin netlist parsing (mem=838.2M) ***

Created 1129 new cells from 4 timing libraries.

Reading netlist ...

Backslashed names will retain backslash and a trailing blank

character.

Reading verilog netlist

'../HDL/GATE/11072023/10h50m41s/postSynthesis_svt_clk_4.5.v'

*** Memory Usage v#1 (Current mem = 838.184M, initial mem = 292.316M)

*** End netlist parsing (cpu=0:00:00.1, real=0:00:00.0, mem=838.2M)

*** End Load netlist data ... (date=11/07 13:21:19, total

cpu=0:00:00.1, real=0:00:00.0, peak res=679.2M, current mem=679.2M)

Set top cell to top_32b.

Hooked 2258 DB cells to tlib cells.

Starting recursive module instantiation check.

No recursion found.

Building hierarchical netlist for Cell top_32b ...

*** Netlist is unique.

** info: there are 2317 modules.

** info: there are 3675 stdCell insts.

** info: there are 3 macros.

*** Memory Usage v#1 (Current mem = 907.109M, initial mem = 292.316M)

*** 0

```

#### 4.5.4. INITIALIZE THE DESIGN ENVIRONMENT

Let's initialize some variables being useful later on in the design

```

@innovus 6> set_db init_ground_nets VSS

1 VSS

@innovus 7> set_db init_power_nets VDD

1 VDD

```

**Here we defined the names of the power nets being used in the design**

```

@innovus 8> set_db timing_analysis_type ocv

1 ocv

@innovus 9> set_db timing_analysis_cppr both

1 both

```

**Here we define the type of timing analysis being performed. OCV for on chip variations, and remove pessimism in the clock tree path (CPPR – Clock Path Pessimism Removal) in both hold and setup. This simplifies the clock tree design for this design which is simple.**

```

@innovus 10> set_db design_process_node 65

## Process: 65 (User Set)

## Node: (not set)

## Check design process and node:

## Design tech node is not set.

```

```

Applying the recommended capacitance filtering threshold values for

65nm process node: total_c_th=0, relative_c_th=1 and

coupling_c_th=0.1.

```

```

These values will be used by all post-route extraction engines,

including TQuantus, IQuantus and Quantus QRC extraction.

```

```

Capacitance filtering mode(extract_rc_cap_filter_mode option of

the set_db) is 'relative_and_coupling' for all engines.

```

```

The accuracy mode for post_route extract_rc_effort_level low

extraction will be set to 'high'.

```

```

Default value for EffortLevel(extract_rc_effort_level option of

the set_db) in post_route extraction mode will be 'medium' if Quantus

QRC technology file is specified else 'low'.

```

```

1 65

```

**Defining a process sets several parameters in innovus, and aligns the flow with the constraints associated with a 65nm technology process. It does select different types of RC extraction for coupling, threshold on R and C etc.**

```

@innovus 11> set_db design_top_routing_layer M5

1 M5

@innovus 12> set_db design_bottom_routing_layer M2

1 M2

```

**Here we define the Top and Bottom routing layers. In this flow, the tool will be allowed to route from M2 to M5.**

Then, we initialize the design

```

Innovus > init_design

```

```

Set Default Net Delay as 1000 ps.

Set Default Net Load as 0.5 pF.

Set Default Input Pin Transition as 0.1 ps.

```

```

**WARN: (IMPFP-3961): The techSite 'VLC_SITE_sramHD_64x64' has no related

standard cells in LEF/OA library. Cannot make calculations for this site type unless

standard cell models of this type exist in the LEF/OA library. If the SITE is not

used by the library you can ignore this warning or remove the SITE definition from

the LEF/OA to avoid this message.

Type 'man IMPFP-3961' for more detail.

```

**This warning comes from the lef of the memory. You can ignore it at this point**

```

Extraction setup Started

Initializing multi-corner RC extraction with 2 active RC Corners ...

Capable file(s) not specified in multi-corner setup. PreRoute extraction will use

technology file. For post_route extraction, default value for effort level would be

'medium' and effort level 'low' would not be allowed.

Generating auto layer map file.

Importing multi-corner technology file(s) for preRoute extraction...

/dkits/gf/65nm/65LPe/pdk/65LPe/PEX/QRC/EDA-CAD-65N-

EX038/Rev9/cmos10lpe_6_00_01_00_LB/cmos10lpe_FuncCmax_6_00_01_00_LB_effective/qrc

TechFile

Generating auto layer map file.

/dkits/gf/65nm/65LPe/pdk/65LPe/PEX/QRC/EDA-CAD-65N-

EX038/Rev9/cmos10lpe_6_00_01_00_LB/cmos10lpe_FuncCmin_6_00_01_00_LB_effective/qrc

TechFile

Generating auto layer map file.

Completed (cpu: 0:00:03.5 real: 0:00:04.0)

Set Shrink Factor to 1.00000

```

**From the technology corners defined and the RC parasitic files (qrcTechFile) selected, the tool summarizes all the parameters.**

Summary of Active RC-Corners :

```

Analysis View: analysis_setup_wc

RC-Corner Name      : corner_rcworst

RC-Corner Index     : 0

RC-Corner Temperature : 25 Celsius

RC-Corner Cap Table  : ''

RC-Corner PreRoute Res Factor      : 1

RC-Corner PreRoute Cap Factor     : 1

RC-Corner PostRoute Res Factor    : 1 {1 1 1}

RC-Corner PostRoute Cap Factor   : 1 {1 1 1}

RC-Corner PostRoute XCap Factor  : 1 {1 1 1}

RC-Corner PreRoute Clock Res Factor : 1 [Derived]      from postRoute_res

(effortLevel low)

RC-Corner PreRoute Clock Cap Factor : 1 [Derived]      from postRoute_cap

(effortLevel low)

RC-Corner PostRoute Clock Cap Factor : 1 {1 1 1} [Derived]      from

postRoute_cap (effortLevel low)

RC-Corner PostRoute Clock Res Factor : 1 {1 1 1} [Derived]      from

postRoute_res (effortLevel low)

RC-Corner Technology file: '/dkits/gf/65nm/65LPe/pdk/65LPe/PEX/QRC/EDA-CAD-

65N-

EX038/Rev9/cmos10lpe_6_00_01_00_LB/cmos10lpe_FuncCmax_6_00_01_00_LB_effective/qrc

TechFile'

Analysis View: analysis_hold_bc

RC-Corner Name      : corner_rcbest

RC-Corner Index     : 1

RC-Corner Temperature : 25 Celsius

RC-Corner Cap Table  : ''

RC-Corner PreRoute Res Factor      : 1

RC-Corner PreRoute Cap Factor     : 1

RC-Corner PostRoute Res Factor    : 1 {1 1 1}

RC-Corner PostRoute Cap Factor   : 1 {1 1 1}

RC-Corner PostRoute XCap Factor  : 1 {1 1 1}

RC-Corner PreRoute Clock Res Factor : 1 [Derived]      from postRoute_res

(effortLevel low)

RC-Corner PreRoute Clock Cap Factor : 1 [Derived]      from postRoute_cap

(effortLevel low)

RC-Corner PostRoute Clock Cap Factor : 1 {1 1 1} [Derived]      from

postRoute_cap (effortLevel low)

RC-Corner PostRoute Clock Res Factor : 1 {1 1 1} [Derived]      from

postRoute_res (effortLevel low)

RC-Corner Technology file: '/dkits/gf/65nm/65LPe/pdk/65LPe/PEX/QRC/EDA-CAD-

65N-

EX038/Rev9/cmos10lpe_6_00_01_00_LB/cmos10lpe_FuncCmin_6_00_01_00_LB_effective/qrc

TechFile'

Updating RC grid for preRoute extraction ...

Initializing multi-corner resistance tables ...

Default value for post_route extraction mode's extract_rc_effort_level

(extract_rc_effort_level option of set_db) changed to 'medium'.

*Info: initialize multi-corner CTS.

Reading timing constraints file

'/home/levisse/projects/CLASSROOM/PHASE2/testdirs/edalabs_phase2_2024/DesignCompi

ler/SDC/11072023/10h50m41s/postSynthesis_svt_clk_4.5.sdc'...

Current (total cpu=0:14:12, real=1:29:00, peak res=1204.3M, current mem=1078.5M)

**WARN: (TCLCMD-1461): Skipped unsupported command: set_units (File

'/home/levisse/projects/CLASSROOM/PHASE2/testdirs/edalabs_phase2_2024/DesignCompil

er/SDC/11072023/10h50m41s/postSynthesis_svt_clk_4.5.sdc, Line 8).

INFO      (CTE):      Reading      of      timing      constraints      file

'/home/levisse/projects/CLASSROOM/PHASE2/testdirs/edalabs_phase2_2024/DesignCompil

er/SDC/11072023/10h50m41s/postSynthesis_svt_clk_4.5.sdc completed, with 1 WARNING

WARNING      (CTE-25):      Line:      10      of      File

'/home/levisse/projects/CLASSROOM/PHASE2/testdirs/edalabs_phase2_2024/DesignCompil

er/SDC/11072023/10h50m41s/postSynthesis_svt_clk_4.5.sdc' : Skipped unsupported

command: set max area

```

```

WARNING (CTE-25): Line: 9 of File

/home/levisse/projects/CLASSROOM/PHASE2/testdirs/edalabs_phase2_2024/DesignCompiler/SDC/11072023/10h50m41s/postSynthesis_svt_clk_4.5.sdc : Skipped unsupported command: set_operating_conditions

Ending "Constraint file reading stats" (total cpu=0:00:00.1, real=0:00:00.0, peak res=1095.6M, current mem=1095.6M)

Current (total cpu=0:14:12, real=1:29:00, peak res=1204.3M, current mem=1095.6M)

Reading timing constraints file

'/home/levisse/projects/CLASSROOM/PHASE2/testdirs/edalabs_phase2_2024/DesignCompiler/SDC/11072023/10h50m41s/postSynthesis_svt_clk_4.5.sdc' ...

Current (total cpu=0:14:12, real=1:29:00, peak res=1204.3M, current mem=1095.6M)

**WARN: (TCLCMD-1461): Skipped unsupported command: set_units (File

/home/levisse/projects/CLASSROOM/PHASE2/testdirs/edalabs_phase2_2024/DesignCompiler/SDC/11072023/10h50m41s/postSynthesis_svt_clk_4.5.sdc, Line 8).

INFO (CTE): Reading of timing constraints file

/home/levisse/projects/CLASSROOM/PHASE2/testdirs/edalabs_phase2_2024/DesignCompiler/SDC/11072023/10h50m41s/postSynthesis_svt_clk_4.5.sdc completed, with 1 WARNING

WARNING (CTE-25): Line: 10 of File

/home/levisse/projects/CLASSROOM/PHASE2/testdirs/edalabs_phase2_2024/DesignCompiler/SDC/11072023/10h50m41s/postSynthesis_svt_clk_4.5.sdc : Skipped unsupported command: set_max_area

WARNING (CTE-25): Line: 9 of File

/home/levisse/projects/CLASSROOM/PHASE2/testdirs/edalabs_phase2_2024/DesignCompiler/SDC/11072023/10h50m41s/postSynthesis_svt_clk_4.5.sdc : Skipped unsupported command: set_operating_conditions

Ending "Constraint file reading stats" (total cpu=0:00:00.0, real=0:00:00.0, peak res=1095.9M, current mem=1095.9M)

Current (total cpu=0:14:12, real=1:29:00, peak res=1204.3M, current mem=1095.9M)

```

### Here the tool lists all the cells available for the design to come

```

Total number of combinational cells: 954

Total number of sequential cells: 174

Total number of tristate cells: 0

Total number of level shifter cells: 0

Total number of power gating cells: 0

Total number of isolation cells: 0

Total number of power switch cells: 0

Total number of pulse generator cells: 0

Total number of always on buffers: 0

Total number of retention cells: 0

List of usable buffers: SEN_BUF_1 SEN_BUF_10 SEN_BUF_12 SEN_BUF_16 SEN_BUF_2

SEN_BUF_1P5 SEN_BUF_20 SEN_BUF_24 SEN_BUF_3 SEN_BUF_4 SEN_BUF_6 SEN_BUF_8

SEN_BUF_AS_1 SEN_BUF_AS_0P5 SEN_BUF_AS_10 SEN_BUF_AS_12 SEN_BUF_AS_16 SEN_BUF_AS_2

SEN_BUF_AS_1P5 SEN_BUF_AS_3 SEN_BUF_AS_4 SEN_BUF_AS_5 SEN_BUF_D_1 SEN_BUF_AS_6

SEN_BUF_AS_8 SEN_BUF_D_12 SEN_BUF_D_16 SEN_BUF_S_1 SEN_BUF_D_2 SEN_BUF_D_3

SEN_BUF_D_4 SEN_BUF_D_6 SEN_BUF_D_8 SEN_BUF_S_12 SEN_BUF_S_16 SEN_BUF_S_2

SEN_BUF_S_3 SEN_BUF_S_4 SEN_BUF_S_6 SEN_BUF_S_8

Total number of usable buffers: 40

List of unusable buffers:

Total number of unusable buffers: 0

List of usable inverters: SEN_INV_0P5 SEN_INV_0P65 SEN_INV_1 SEN_INV_0P8 SEN_INV_10

SEN_INV_12 SEN_INV_16 SEN_INV_1P25 SEN_INV_2 SEN_INV_1P5 SEN_INV_20 SEN_INV_24

SEN_INV_3 SEN_INV_2P5 SEN_INV_32 SEN_INV_4 SEN_INV_5 SEN_INV_6 SEN_INV_8

SEN_INV_AS_1 SEN_INV_AS_0P5 SEN_INV_AS_10 SEN_INV_AS_12 SEN_INV_AS_16 SEN_INV_AS_2

SEN_INV_AS_1P5 SEN_INV_AS_3 SEN_INV_AS_4 SEN_INV_AS_5 SEN_INV_AS_6 SEN_INV_AS_8

SEN_INV_S_1 SEN_INV_S_0P5 SEN_INV_S_12 SEN_INV_S_16 SEN_INV_S_2 SEN_INV_S_1P5

SEN_INV_S_3 SEN_INV_S_32 SEN_INV_S_4 SEN_INV_S_6 SEN_INV_S_8

Total number of usable inverters: 42

List of unusable inverters:

Total number of unusable inverters: 0

List of identified usable delay cells: SEN_DEL_L4_1 SEN_DEL_L4_2 SEN_DEL_L4_4

SEN_DEL_L4_8 SEN_DEL_L6_1 SEN_DEL_L6_2 SEN_DEL_L6_4 SEN_DEL_L6_8

```

```

Total number of identified usable delay cells: 8

List of identified unusable delay cells:

Total number of identified unusable delay cells: 0

```

#### 4.5.5. INITIALIZE THE METRICS EXTRACTION

In the latest versions of innovus, it does embed some feature called metrics.

It does enable you to save the state of your design and some metrics in a html file which can be opened at the end of the flow.

Let's enable the metrics feature so that we can check the reports later.

```

innovus > enable_metrics -on

```

- ➊ What this function does is storing all the metrics of the design (area, slack, reports etc.) at a certain point in time. You will see that we will use some snapshot-related commands later on.

- ➋ This relies on 2 commands :

```

>push_snapshot_stack

>pop_snapshot_stack

```

Everything happening between these two commands will be tracked and saved in the final html file.

#### 4.5.6. AUTOMATE THE FLOW

As for all the other tools you used until now, this step can be automatically done through a script written in the tcl language.

1. From the terminal, using the gedit tool, open the following files and understand their content :

```

INNOVUS/BIN/init.tcl

INNOVUS/BIN/top32_mmmc_svt_mem64_4p5ns.view

```

- ➊ These two files contain all the commands you did write before. From a new instance of innovus, you can reach back the point where we are here, by running the following commands.

- ➋ Note that init.tcl imports the .view file through the read\_mmmc command, so sourcing the init.tcl file will also setup the mmc.

For innovus, we propose a different way to write a tcl script. If you take a look at the BIN folder, you will notice several files, and a file called “fullflow.tcl” which contains source commands to all the other files. This way allows you to handle longer scripts in a more comfortable way. And ease the process of progressively go through the flow. Though, when making different versions of the same flow, it does then require the designer to make an organizational effort.

#### 4.5.7. SAVE AND RESTORE THE DESIGN STATE

As opposed to dc\_shell, where you noticed that restoring the ddc file was not that straightforward, innovus does provide a complete save/restore design function which allows you to fully save and restore the actual state of the tool at any point.

As the place and route is a fairly longer process than logic synthesis, being able to save and restore the tool state can actually be useful.

1. To save the state of a design, run the following command :

```

Innovus> write_db DB/tutorial/top_32b_INIT

#% Begin save design ... (date=11/08 11:26:36, mem=1133.9M)

% Begin Save ccopt configuration ... (date=11/08 11:26:36, mem=1137.0M)

% End Save ccopt configuration ... (date=11/08 11:26:36, total

cpu=0:00:00.0, real=0:00:00.0, peak res=1137.8M, current

mem=1137.8M)

% Begin Save netlist data ... (date=11/08 11:26:36, mem=1137.9M)

Writing Binary DB to DB/tutorial/top_32b_INIT/top_32b.v.bin in

single-threaded mode...

% End Save netlist data ... (date=11/08 11:26:36, total

cpu=0:00:00.0, real=0:00:00.0, peak res=1138.0M, current

mem=1138.0M)

Saving symbol-table file ...

Saving congestion map file

DB/tutorial/top_32b_INIT/top_32b.route.congmap.gz ...

% Begin Save AAE data ... (date=11/08 11:26:37, mem=1138.6M)

Saving AAE Data ...

% End Save AAE data ... (date=11/08 11:26:37, total cpu=0:00:00.0,

real=0:00:00.0, peak res=1138.6M, current mem=1138.6M)

Saving preference file DB/tutorial/top_32b_INIT/gui.pref.tcl ...

Saving mode setting ...

Saving root attributes to be loaded post write_db ...

Saving global file ...

Saving root attributes to be loaded previous write_db ...

% Begin Save floorplan data ... (date=11/08 11:26:38, mem=1142.9M)

Saving floorplan file ...

% End Save floorplan data ... (date=11/08 11:26:38, total

cpu=0:00:00.0, real=0:00:00.0, peak res=1143.4M, current

mem=1143.4M)

Saving Drc markers ...

... No Drc file written since there is no markers found.

% Begin Save placement data ... (date=11/08 11:26:38, mem=1143.5M)

** Saving stdCellPlacement_binary (version# 2) ...

Save Adaptive View Pruning View Names to Binary file

% End Save placement data ... (date=11/08 11:26:38, total

cpu=0:00:00.0, real=0:00:01.0, peak res=1143.7M, current

mem=1143.7M)

% Begin Save routing data ... (date=11/08 11:26:39, mem=1143.7M)

Saving route file ...

*** Completed saveRoute (cpu=0:00:00.0 real=0:00:00.0 mem=1283.5M)

***

% End Save routing data ... (date=11/08 11:26:39, total

cpu=0:00:00.0, real=0:00:00.0, peak res=1147.9M, current

mem=1147.9M)

Saving property file DB/tutorial/top_32b_INIT/top_32b.prop

*** Completed saveProperty (cpu=0:00:00.0 real=0:00:00.0

mem=1286.5M) ***

Saving preRoute extracted patterns in file

'DB/top_32b_INIT/top_32b.techData.gz' ...

Saving preRoute extraction data in directory

'DB/tutorial/top_32b_INIT/extraction/' ...

% Begin Save power constraints data ... (date=11/08 11:26:39,

mem=1149.1M)

```

```

% End Save power constraints data ... (date=11/08 11:26:39, total

cpu=0:00:00.0, real=0:00:00.0, peak res=1149.2M, current

mem=1149.2M)

Generated self-contained design top_32b_INIT

#% End save design ... (date=11/08 11:26:40, total cpu=0:00:01.5,

real=0:00:04.0, peak res=1153.6M, current mem=1153.6M)

*** Message Summary: 0 warning(s), 0 error(s)

```

**Essentially here the tool is saving all the details of the design.**

In the same way, from a new version of innovus (if you exit it and start it again), you can restore a db.

1. To restore the init state you just saved, from a new innovus instance

`innovus > read_db DB/tutorial/top_32b_INIT.db`

Note that here, innovus will go through the configuration of the mmmc file again, as this step is kind of mandatory. But restoring more advanced part of the design will be faster.

## 4.6. FLOORPLANNING THE DESIGN

The logic cells in the gate-level netlist obtained from synthesis will be placed in rows in the so-called *core area*. All physical cells in the standard cell library have the same height and different widths. They all have a power rail at their top and a ground rail at their bottom. Physical cells are abutted in a row so their power and ground rails connect between cells. The rows in the core area are further flipped so power and ground rails of neighboring rows coincide.

The floorplan defines the actual form, or aspect ratio, of the core area, the global and detailed routing grids, the rows to host the core cells and the I/O pad cells (if required), the area for power rings, the (pre)placement of blocks/macros, and the location of the corner cells (if required). After the design import, an initial default floorplan is displayed in the display area.

### 4.6.1. DEFINE THE FLOORPLAN

Run the following command :

```

@innovus 7> create_floorplan -site CP65_DST -core_size 980 110

20 20 20 20

**WARN: (IMPFP-3961): The techSite 'VLC_SITE_sramHD_64x64' has no

related standard cells in LEF/OA library. Cannot make calculations

for this site type unless standard cell models of this type exist in

the LEF/OA library. If the SITE is not used by the library you can

ignore this warning or remove the SITE definition from the LEF/OA to

avoid this message.

Type 'man IMPFP-3961' for more detail.

```

**You can ignore this warning which comes from the memory macro which also has a SITE being defined. Though here we use the site reference of the standard cell library (see after).**

```

**WARN: (IMPFP-325): Floorplan of the design is resized. All current

create_floorplan objects are automatically derived based on specified

new create_floorplan. This may change blocks, fixed standard cells,

existing routes and blockages.

```

Here we purposely create a suboptimal floorplan which you will need to update and optimize later on.

The `create_floorplan` command has many parameters. Here we use the `-site CP65_DST` which comes from the standard cell library. Line 11 of the lef file (`cp65npksdst.lef`) you will find the following syntax. This defines the size of the rows of standard cells. The 1.8um corresponds to the height of the standard cell track. Using a different standard cell height (for e.g. a HS cell) will require the `-site` to be updated accordingly.

```

# Placement site definition for this library.

SITE CP65_DST

SYMMETRY Y ;

CLASS core ;

SIZE 0.2 BY 1.8 ;

END CP65_DST

```

The lef can be found in

```

IPS/STDCELLS/hd/base/svt/5.00a/lef/5.6/cp65npksdst.lef

```

The `-core_size` command is described in the innovus TCR document in the description of the `create_floorplan` command page 814.

It is documented as follows :

```

-core_size {w h left bottom right top}

Specifies the core size and the spacing, in micrometers, between the

core edge, which is the margin between the outside edge of the core

(head) box.

```

- w: Specifies the core box's width value.

- h: Specifies the core box's height value.

- left: Specifies the margin from the outside edge of the core box to the left.

- bottom: Specifies the margin from the outside edge of the core box to the bottom.

- right: Specifies the margin from the outside edge of the core box to the right.

- top: Specifies the margin from the outside edge of the core box to the top.

The following command creates floorplan by specifying a core size of 1000 x 1000, and the spacing between core edge to each die edge of 300.

Then, some examples are given.

In other words, here, we created a 980um wide by 110um tall box, with 20um space on all sides.

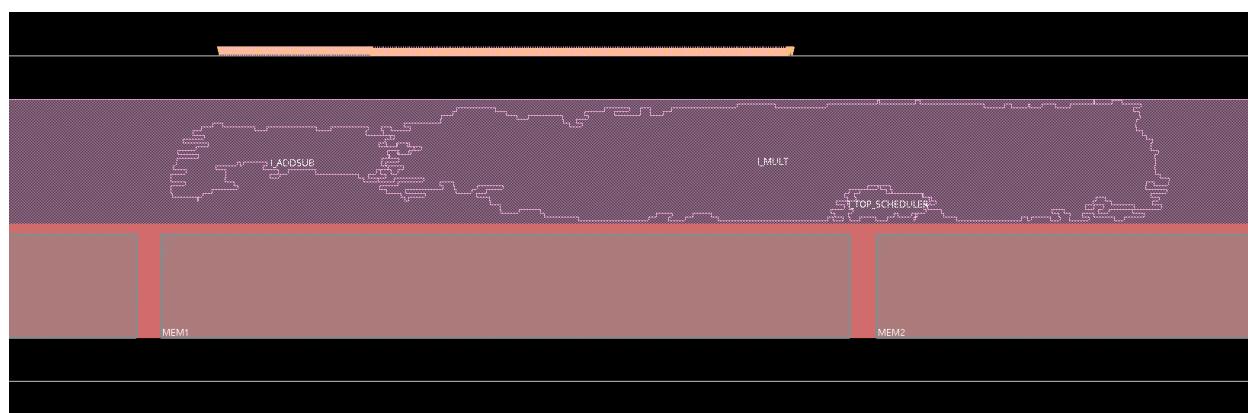

The corresponding floorplan can be observed in the design display area.

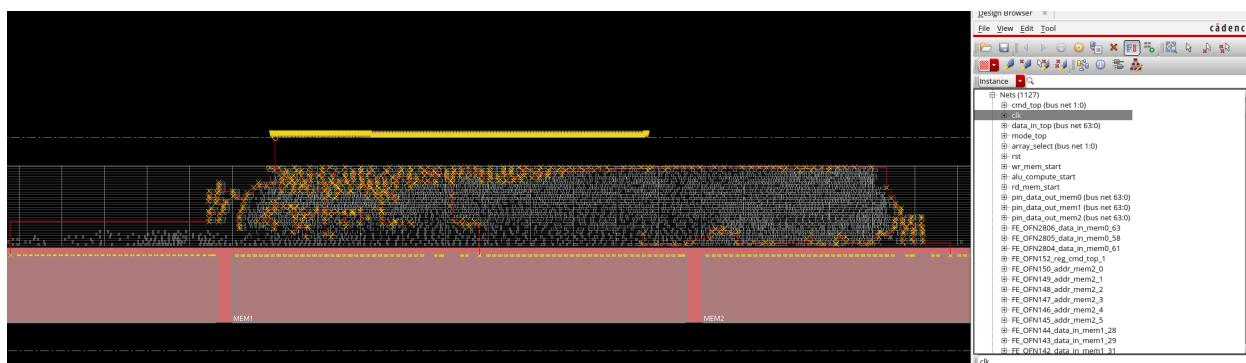

Click on the floorplan view  to print the design units. The floorplan is now visible

Note the three memory macros on the right. And on the left, the two largest blocks (I\_MULT and I\_ADDSUB).

#### 4.6.2. REPORT THE FLOORPLAN UTILIZATION

At this point you can already report the projected density of your design. To make sure that your floorplan makes sense from a design standpoint.

```

innovus 9> check_floorplan -report_density

Checking routing tracks.....

Checking other grids.....

Checking FINFET Grid is on Manufacture Grid.....

Checking core/die box is on Grid.....

Checking snap rule .....

Checking Row is on grid.....

Checking AreaIO row.....

Checking row out of die ...

Checking routing blockage.....

Checking components.....

Checking IO Pads out of die...

Checking constraints (guide/region/fence) .....

Checking groups.....

.

Checking Preroutes.....

No. of regular pre-routes not on tracks : 0

.

Reporting Utilizations.....

```

Here the core utilization is projected to be 54% which is low enough to make sure the design can be routed. There is no absolute rule here, as everything depends on your design and floorplan, though consider that you should generally not go above 80% at this point.

```

Core utilization = 54.142904

Effective Utilizations

**ERROR: (IMPSP-365): Design has inst(s) with SITE

'VLC_SITE_sramHD_64x64', but the floorplan has no rows defined for

this site. Any locations found for such insts will be illegal; create

rows for this site to avoid this.

Type 'man IMPSP-365' for more detail.

```

This error can be ignored at this point. You can use the “man IMPSP-365” command to read about it (we do it after in this code snippet).

```

Average module density = 0.542.

Density for the design = 0.542.

= (stdcell_area 35621 sites (12824 um^2) + block_area 126507

sites (45542 um^2)) / alloc_area 298900 sites (107604 um^2).

Pin Density = 0.04940.

```

```

= total # of pins 14766 / total area 298900.

*** Summary of all messages that are not suppressed in this session:

Severity ID          Count Summary

ERROR    IMPSP-365      1 Design has inst(s) with SITE '%s',

but t...

*** Message Summary: 0 warning(s), 1 error(s)

0

@innovus 15> man IMPSP-365

IMPSP-365 (20.14)                                IMPSP-365 (20.14)

NAME

IMPSP-365

SUMMARY

Design has inst(s) with SITE '%s', but the floorplan has no rows

defined for this site. Any locations found for such insts will be ille-

gal; create rows for this site to avoid this.

DESCRIPTION

This warning will be reported by commands such as check_floorplan and

place_design

when the floorplan does not contain any rows for the specified site.

Each

standard cell in the LEF should have a SITE defined for it. Instances

of this

cell can only be placed in rows defined for this site.

Example:

-----

Run the following command(replace RAM_site with your specific site

name) to report the instances which use this site:

dbGet [dbGet -p3 top.insts.cell.site.name RAM_site].name

When you create the initial floorplan, it should automatically create

rows for

the standard cells defined in the netlist. You can add additional rows

using

Floorplan - Row - Create Core Row or using the create_row text command.

If this

warning is occurring on standard cells you must define rows for them or

else

they will not be placed.

If this problem occurs for hard macros such as memories you can ignore

it.

Rows are not required by the hard macros. Remove the SITE definition in

the LEF for the

hard macros to avoid this message for them.

If this occurs for IO pads you can also ignore it. Rows for IO pads are

optional. You can create IO rows using Floorplan - Row - Create I/O Row

or

using the create_io_row text command.

IMPSP-365 (20.14)

```

Note that here the problem occurs for hard macros. So you can ignore the issues related to VLC\_SITE\_sramHD...

This is one good example of the designer role in the process of filtering useful errors and warnings.

Save the design state as DB/tutorial/top\_32b\_fplan.

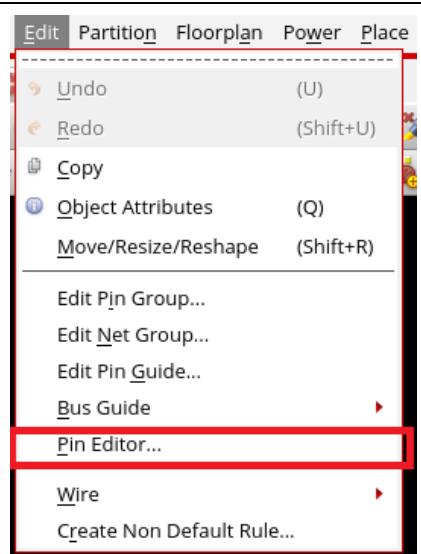

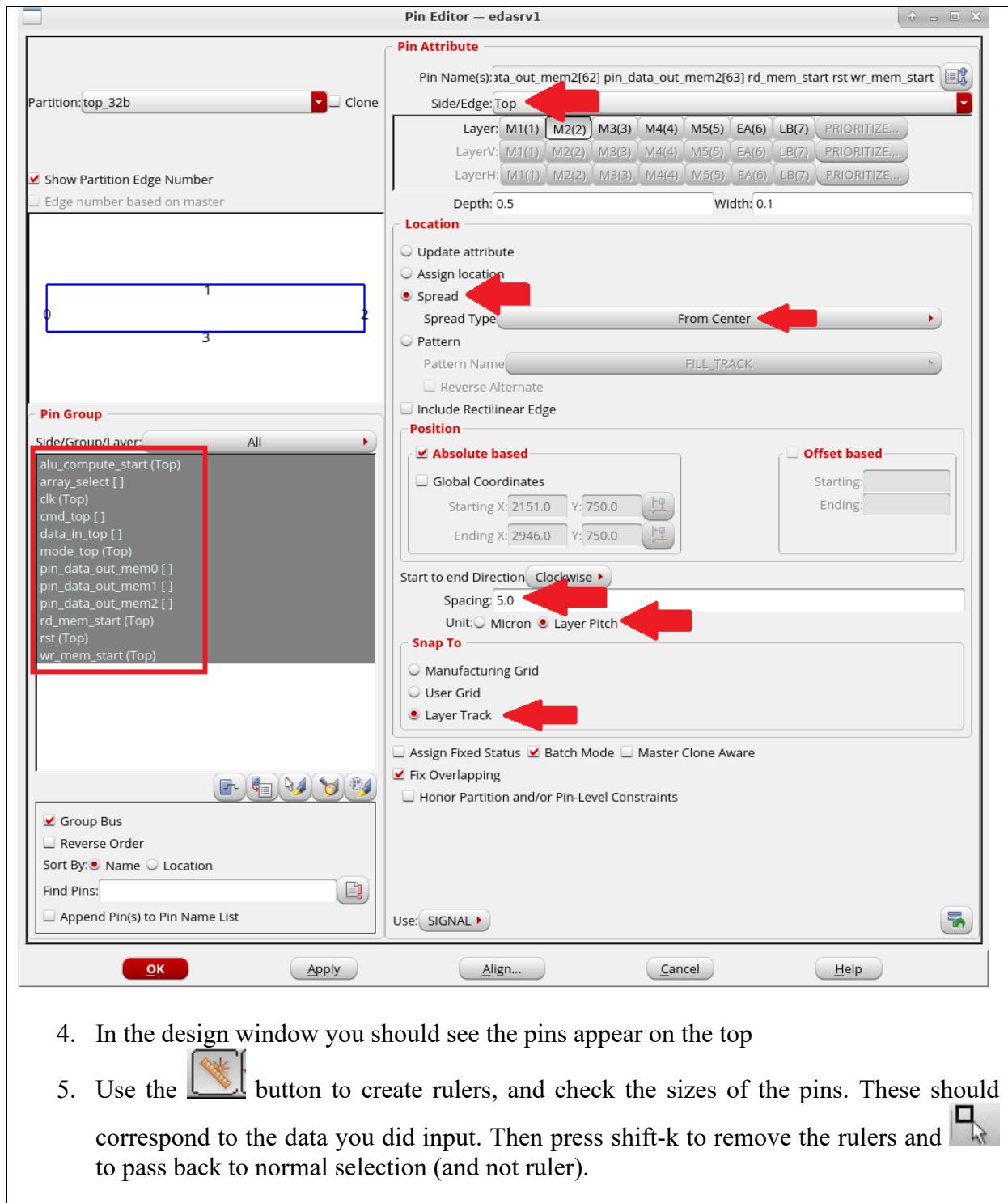

## 4.7.PLACING IO PINS

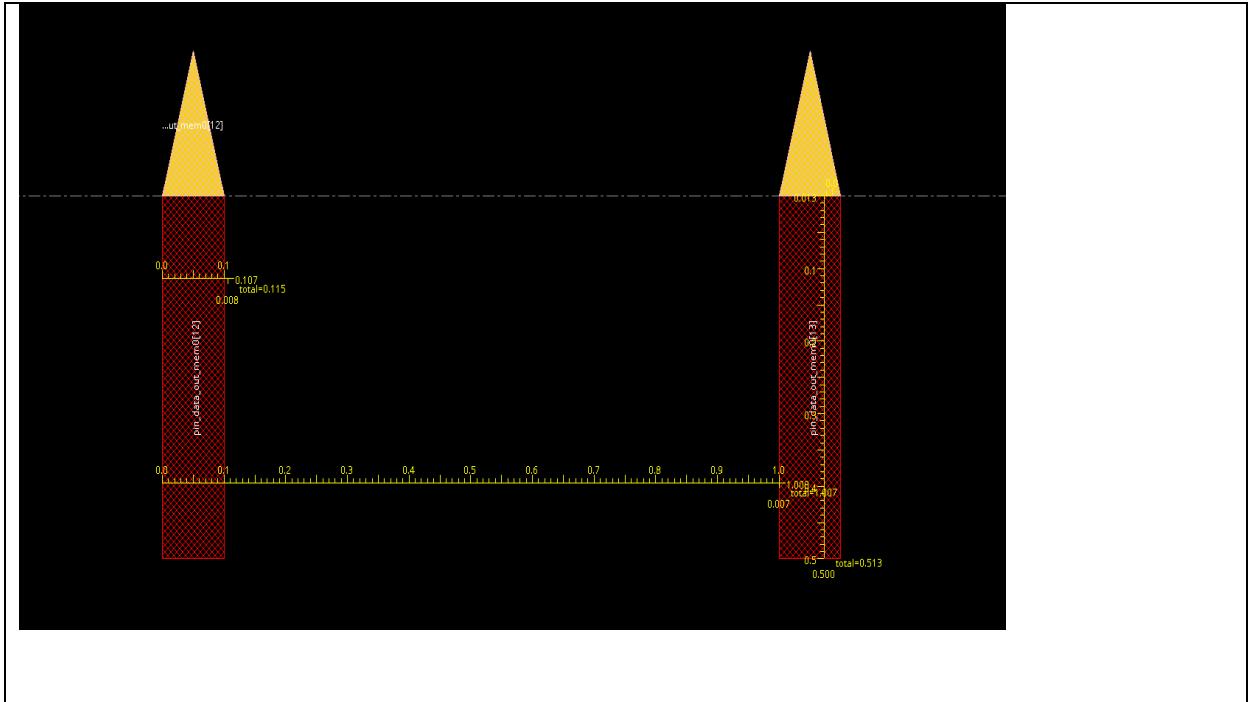

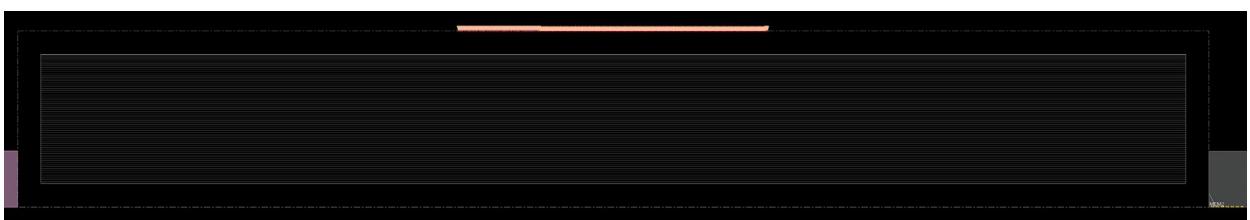

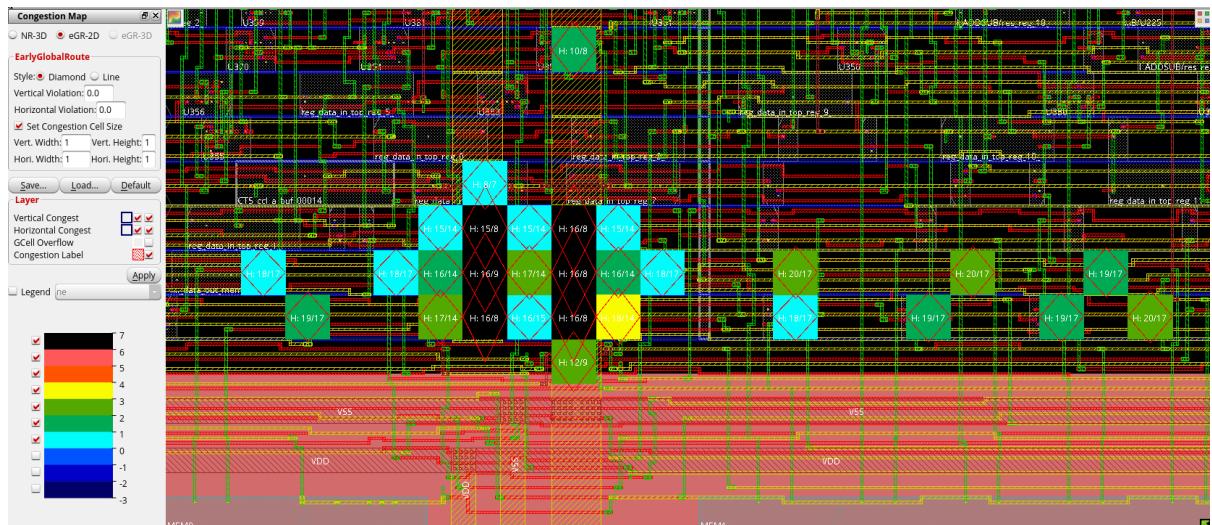

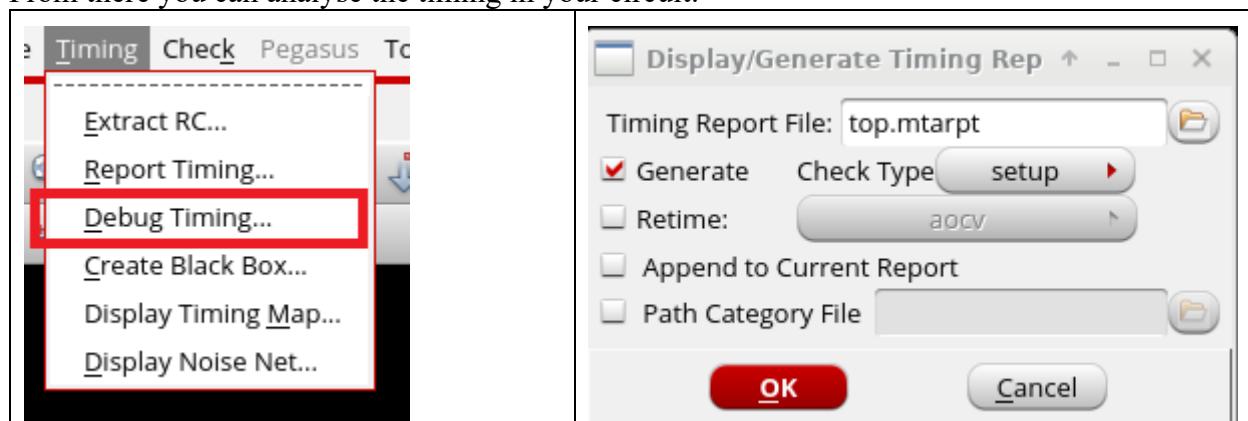

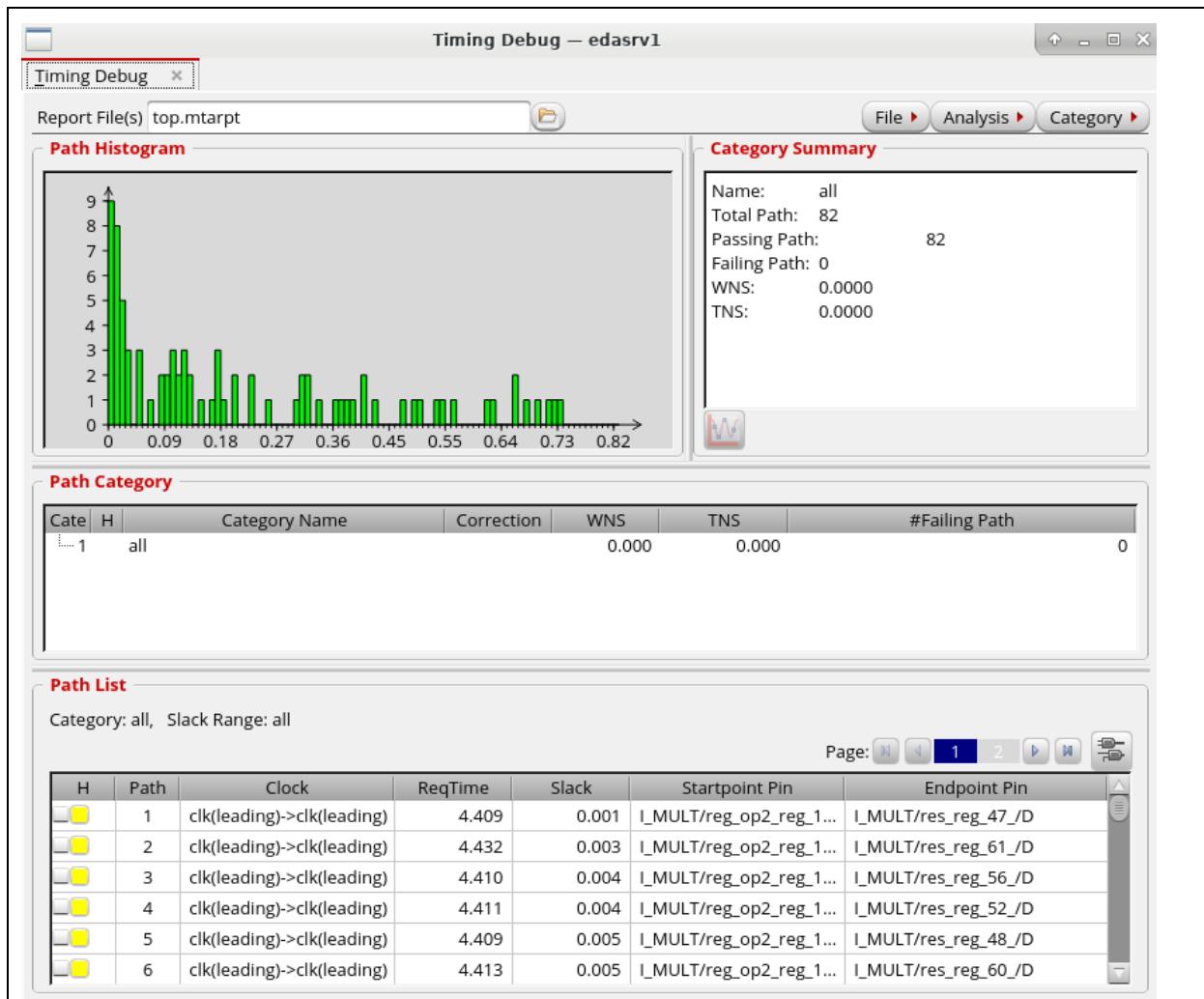

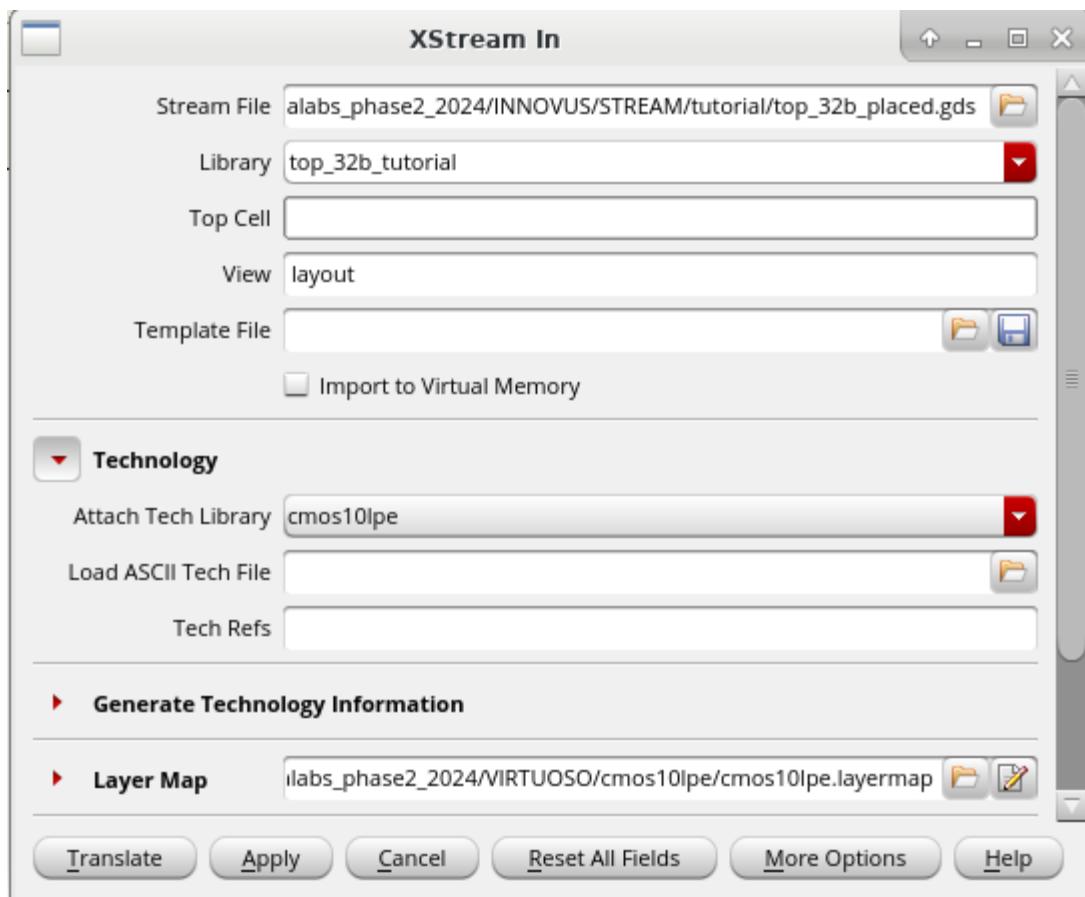

One important part of the floorplan, is the placement of input and output pins. Here in this proposed floorplan, we will place all the IOs on the top.