# **Lecture 8**

# **Microelectronic Devices**

**MOS structure – impact of interface states and trapped charge**

## **MOSFET operation regimes**

- **Linear regime**

- **Saturation regime**

- **Short channel effects**

- **MOSFET scaling and Dennard rule**

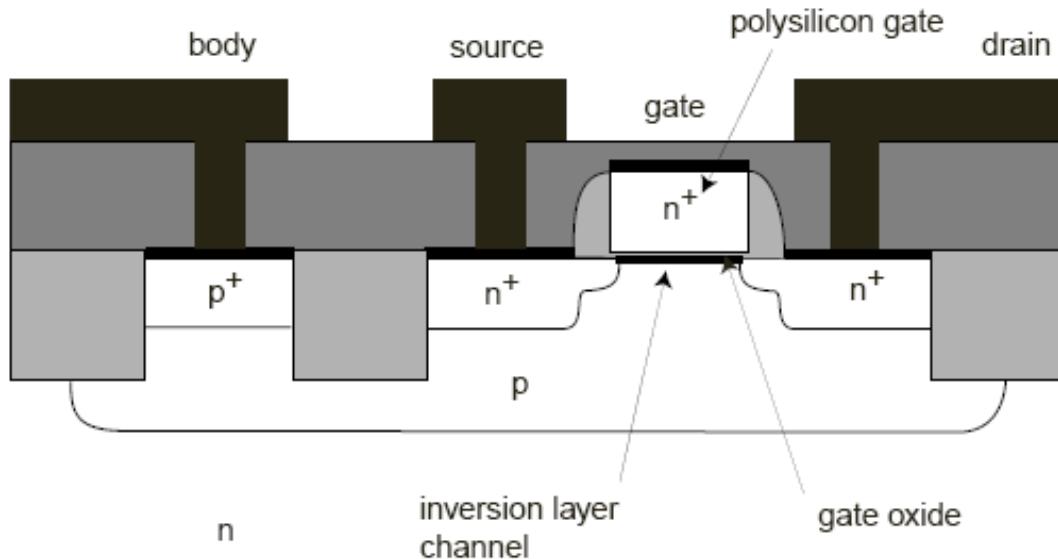

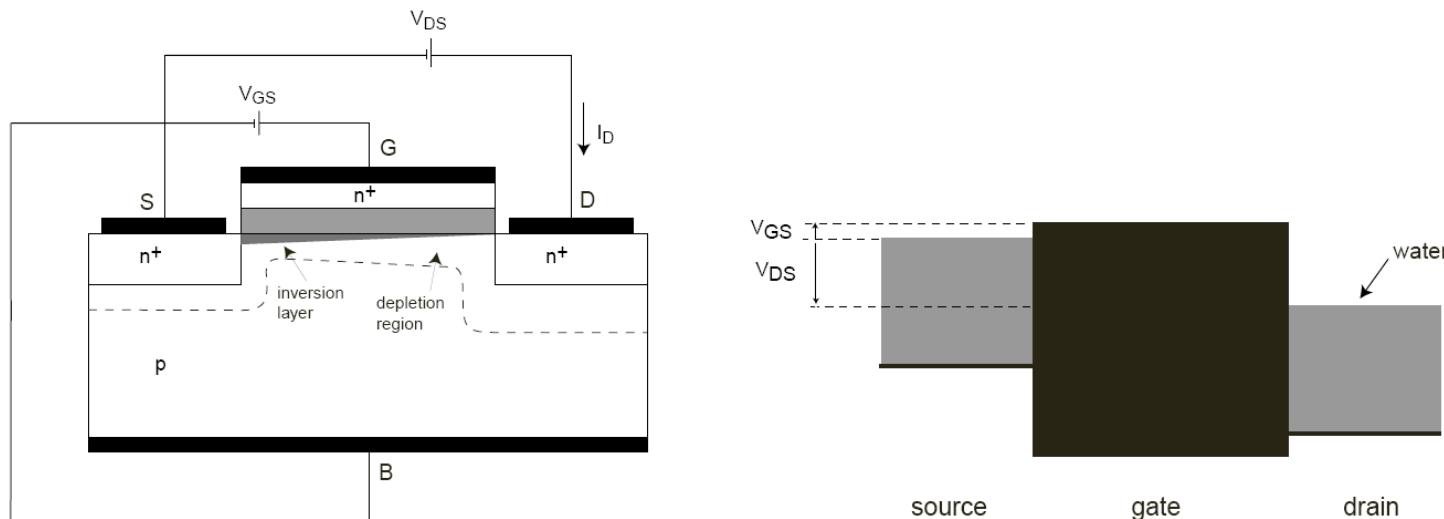

# MOSFET: layout

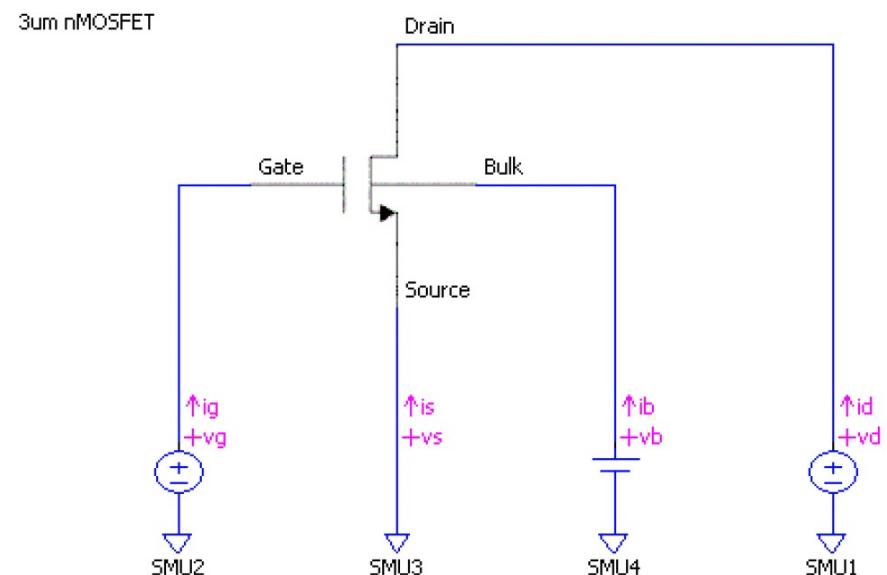

In most MOSFETs in digital logic circuits **Source and Drain are symmetrical**.

Both are **heavily doped** regions:

- **n-type (n+)** for **NMOS**

- **p-type (p+)** for **PMOS**

## Key elements:

- inversion layer under gate (depending on gate voltage)

- heavily-doped regions in source/drain – formed by implantation/annealing

- inversion layer electrically connects source and drain

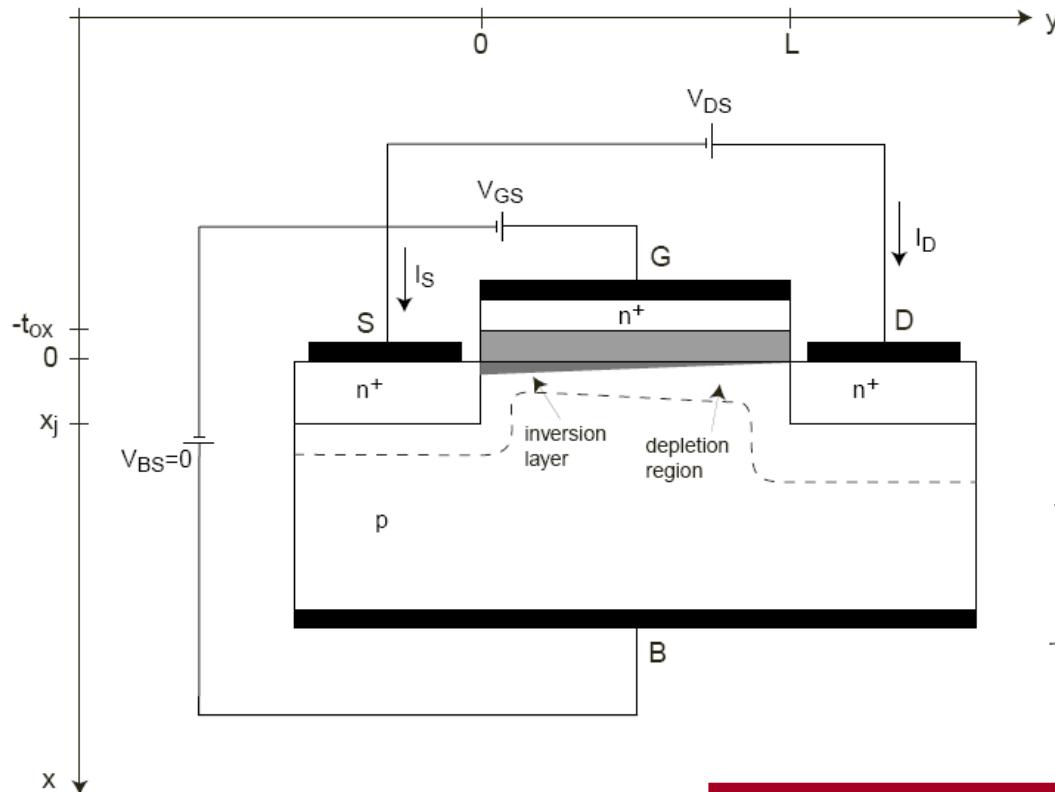

- 4-terminal device: body voltage important

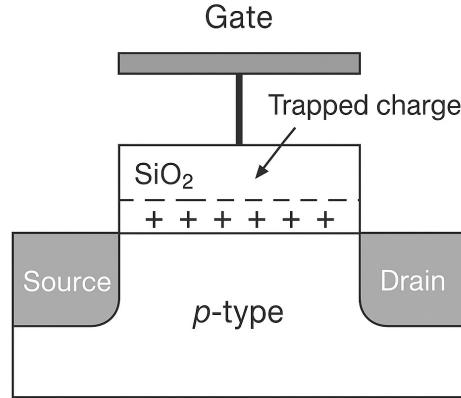

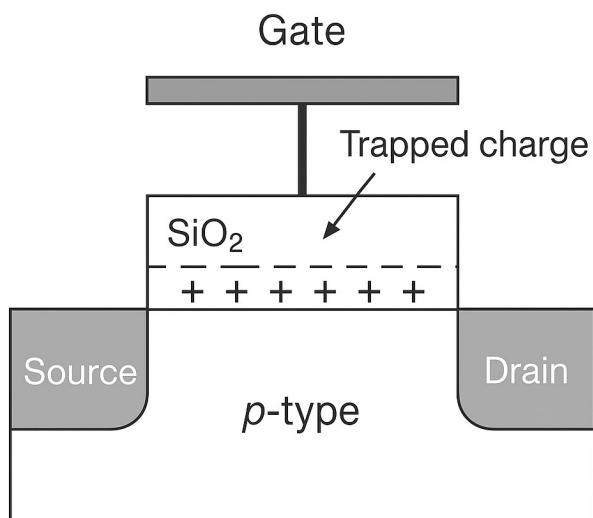

# Imperfect Si/SiO<sub>2</sub> (semiconductor/oxide) interface – trapped charge!

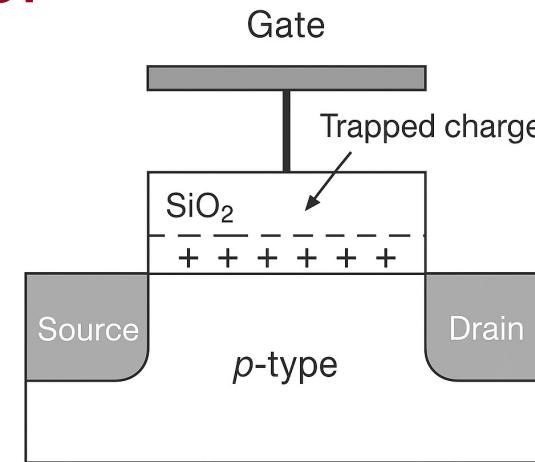

Trapped charges are **unwanted charges** that get "stuck" at the **interface** between the **gate oxide** (usually SiO<sub>2</sub>) and the **semiconductor (Si)**.

These charges can arise due to:

- **Manufacturing defects**

- **Radiation exposure**

- **Charge injection during operation**

- **Impurities or interface states**

Trapped charge can be of different nature:

**Interface trapped charges** at the Si/SiO<sub>2</sub> interface - dangling bonds or defects.

**Fixed oxide charges** - immobile charges in the oxide, typically positive, near interface

**Mobile ionic charges** - contaminants that can move under an electric field (positive)

**Oxide trapped charges** - Charges trapped within the bulk of the oxide

# Imperfect Si/SiO<sub>2</sub> (semiconductor/oxide) interface – trapped charge!

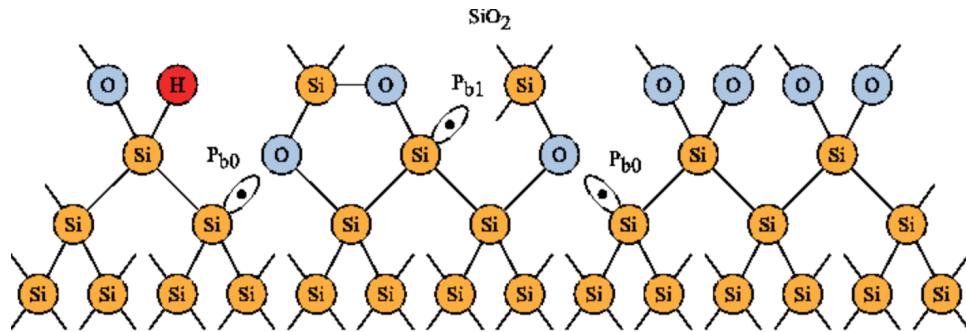

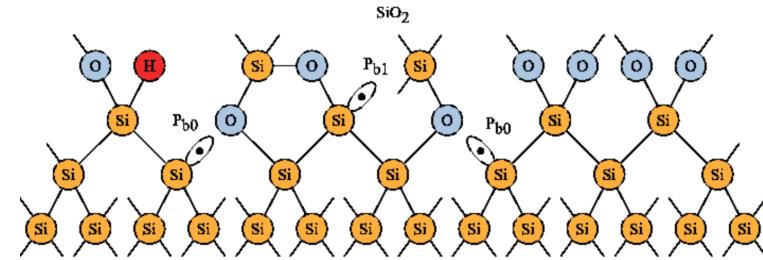

- The **oxide/semiconductor interface** (especially  $\text{Si/SiO}_2$ ) naturally has **dangling bonds** — unsatisfied chemical bonds that can **trap charges** and act as **interface states**

- The interface states trap electrons or holes

Problems: **instability, threshold voltage shifts, and degraded mobility**

- **Forming gas (H<sub>2</sub>-10%, N<sub>2</sub>-90%)** reduces density of interface traps in MOSFET fabrication

## Hydrogen passivation:

- Hydrogen atoms from the forming gas **diffuse into the oxide and interface**

- They **bind to the dangling silicon bonds** ( $\text{Si}\cdot \rightarrow \text{Si}-\text{H}$ )

- This **neutralizes** the defect, removing its ability to trap charge.

# Imperfect Si/SiO<sub>2</sub> interface – trapped charge!

## Threshold Voltage Shift

- Trapped charges can **increase or decrease the threshold voltage**

## Mobility Degradation

- Interface traps can **scatter carriers**, reducing their mobility and thus **degrading drive current**.

## Subthreshold Slope Degradation

A high density of interface traps worsens the subthreshold slope, making the MOSFET **less ideal**.

## Hysteresis

- In devices like memories, mobile or trapped charges can cause **hysteresis** in the I-V characteristics.

# Imperfect Si/SiO<sub>2</sub> interface – trapped charge!

The effect of trapped charge on the threshold voltage depends on the type and polarity of the trapped charge, as well as the type of MOSFET (NMOS or PMOS)

$$\Delta V_T \propto \frac{Q_{\text{trap}}}{C_{ox}}$$

## For n-MOSFET:

- **Positive trapped charge :**

- Increases  $V_T$  → makes it **harder** to turn on the **n-MOSFET**

- **Negative trapped charge:**

- Decreases  $V_T$  → makes it **easier** to turn on

## For p-MOSFET:

- **Positive trapped charge :**

- **Decreases**  $V_T$  → makes it **easier** to turn on the **p-MOSFET**

- **Negative trapped charge:**

- **Decreases**  $V_T$  → makes it **harder** to turn on

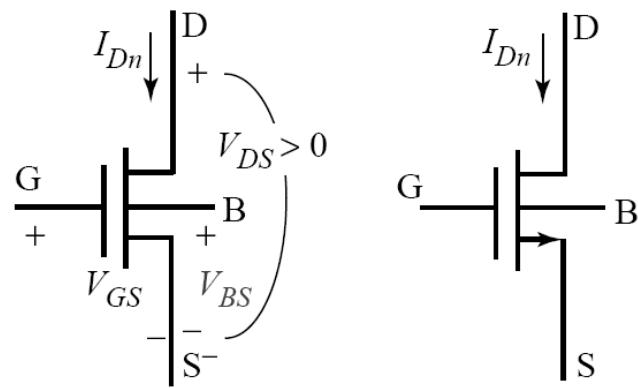

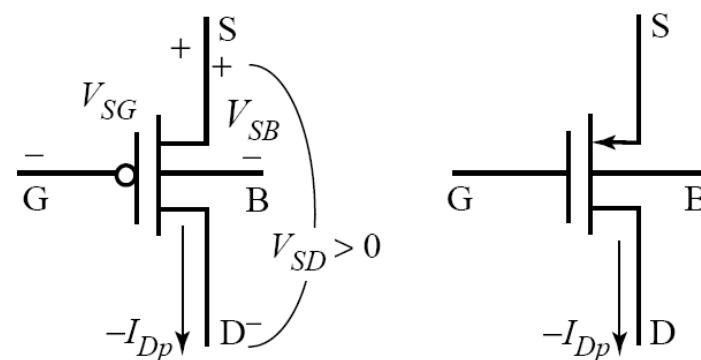

# MOSFET: terminology and symbols

n-channel device (n-MOSFET)

on p-Si substrate (uses electron

inversion layer)

p-channel device (p-MOSFET)

on n-Si substrate (uses hole

inversion layer)

- sometimes the body contact is not figured

# MOSFET: qualitative operation (1)

Water analogy of MOSFET:

- Source: water reservoir

- Drain: water reservoir

- Gate: gate between source and drain reservoirs

- **gate-to-source voltage** → gate height over source water level

- **drain-to-source voltage** → water level difference between reservoirs

## MOSFET: qualitative operation (2)

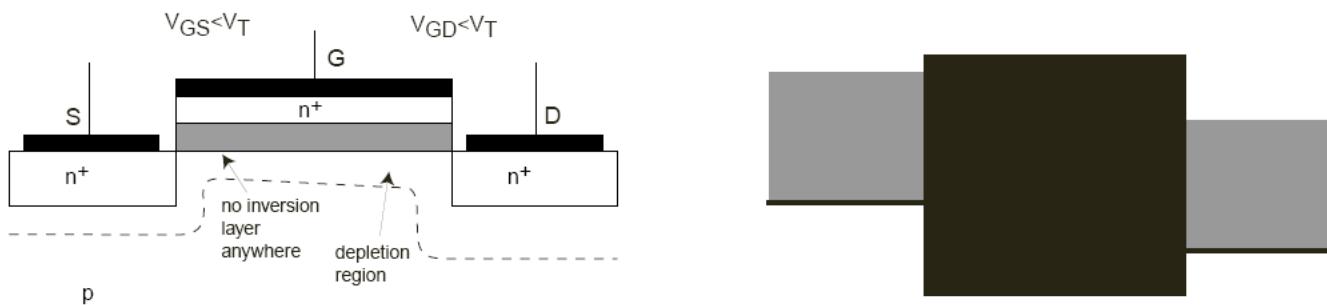

### Regime 1: Cut-off regime (Off)

- MOSFET:  $V_{GS} < V_T$ ,  $V_{GD} < V_T$  with  $V_{DS} > 0$

- Water analogy: gate closed; no water can flow regardless of relative height of source and drain reservoirs.

no water flow

$$I_D = 0$$

# MOSFET: qualitative operation (3)

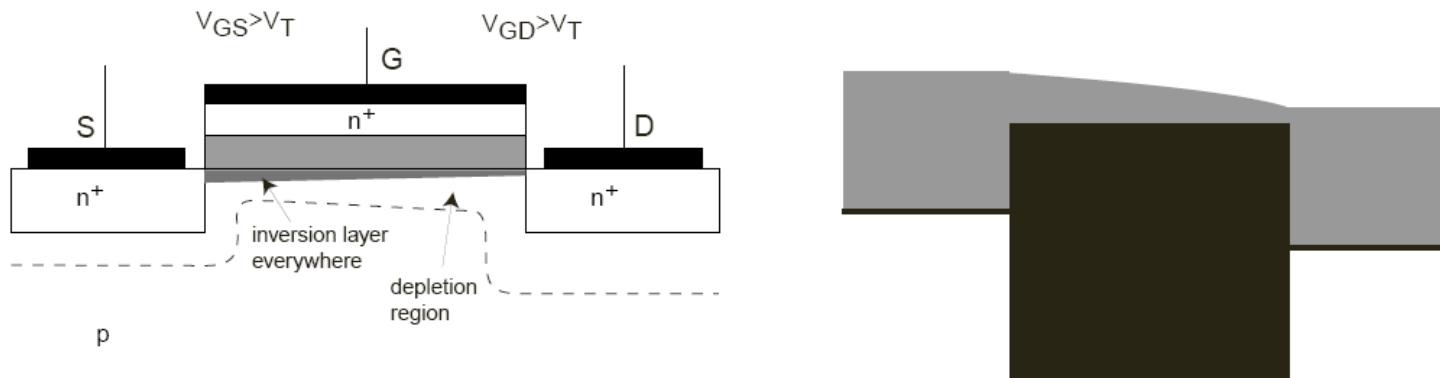

## Regime 2: Linear or Triode regime (On)

- MOSFET:  $V_{GS} > V_T$ ,  $V_{GD} > V_T$ , with  $V_{DS} > 0$ .

- Water analogy: gate open but small difference in height between source and drain; water flows.

Electrons drift from source to drain: **electrical current,  $I_D$ !**

## MOSFET: qualitative operation (4)

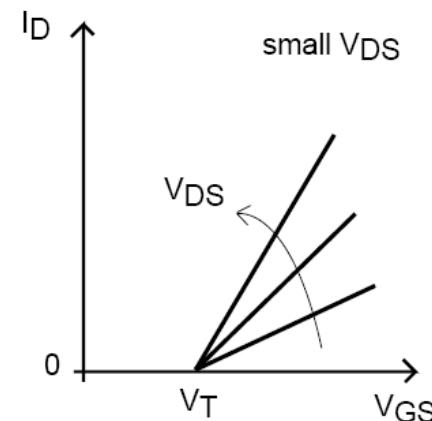

### Regime 2: Linear or Triode regime (On)

Current  $\sim$  inversion charge  $\sim (V_{GS} - V_T) \times V_{DS}$

- $V_{GS} \uparrow \rightarrow |Q_n| \uparrow \rightarrow I_D \uparrow$

- $V_{DS} \uparrow \rightarrow |E_y| \uparrow \rightarrow I_D \uparrow$

## MOSFET: qualitative operation (5)

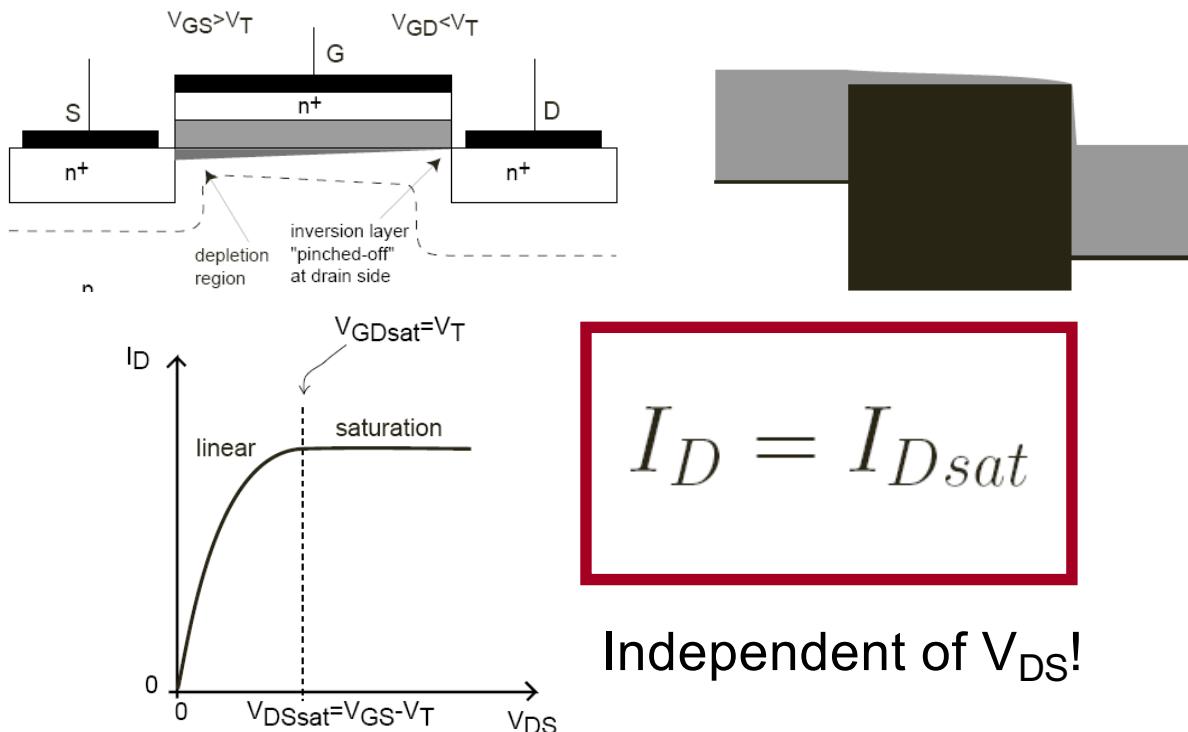

### Regime 3: Saturation regime (On)

- MOSFET:  $V_{GS} > V_T$ ,  $V_{GD} < V_T$  ( $V_{DS} > 0$ ).

- Water analogy: gate open; water flows from source to drain, but free-drop on drain side) total flow independent of relative reservoir height!

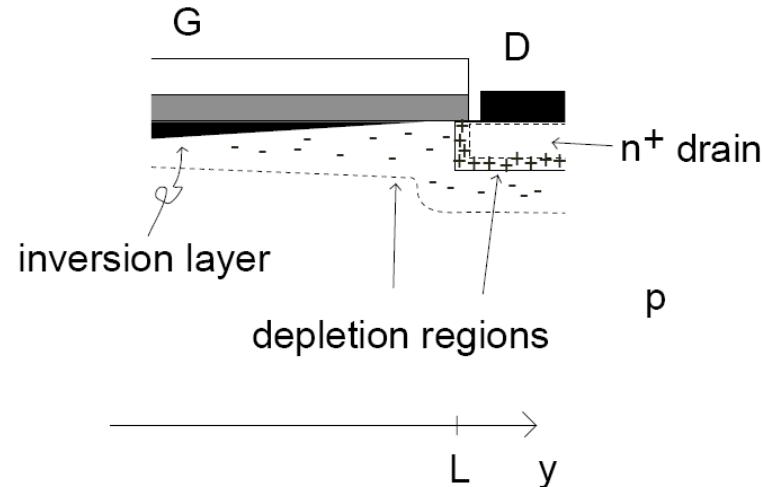

# MOSFET: basics for I-V characteristics

Geometry of problem (current flows in y-direction only)

Current can only flow in y-direction:

$$I_y = WQ_n(y)v_y(y)$$

Drain terminal current :

$$I_D = -WQ_n(y)v_y(y)$$

# MOSFET: the output characteristics

$$I_D = -WQ_n(y)v_y(y) \quad \text{Rewrite in terms of voltage at channel location } y, V_c(y):$$

$$v_y(y) \simeq -\mu_n E_y(y) = \mu_n \frac{dV_c(y)}{dy}$$

$$Q_n(y) = -C_{ox}[V_{GS} - V_c(y) - V_T] \quad V_{GS} - V_c(y) \geq V_T.$$

$$I_D = W\mu_n C_{ox}(V_{GS} - V_c(y) - V_T) \frac{dV_c(y)}{dy}$$

linear first-order differential equation with one unknown, the channel voltage  $V_c(y)$ ,

Solved by separating variables

$$I_D dy = W\mu_n C_{ox}(V_{GS} - V_c - V_T) dV_c$$

$$\text{for } y = 0, V_c(0) = 0$$

$$\text{for } y = L, V_c(L) = V_{DS} \text{ (linear regime)}$$

$$I_D \int_0^L dy = W\mu_n C_{ox} \int_0^{V_{DS}} (V_{GS} - V_c - V_T) dV_c$$

$$I_D = \frac{W}{L} \mu_n C_{ox} \left( V_{GS} - \frac{V_{DS}}{2} - V_T \right) V_{DS}$$

# MOSFET: the output characteristics

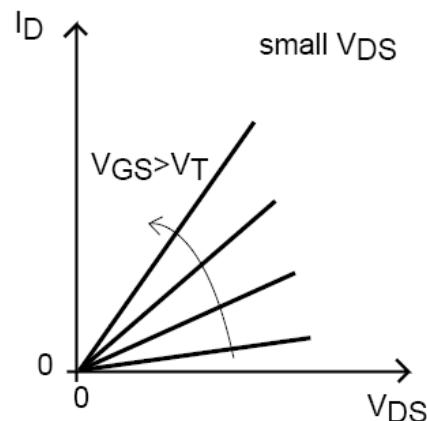

$$I_D = \frac{W}{L} \mu_n C_{ox} \left( V_{GS} - \frac{V_{DS}}{2} - V_T \right) V_{DS}$$

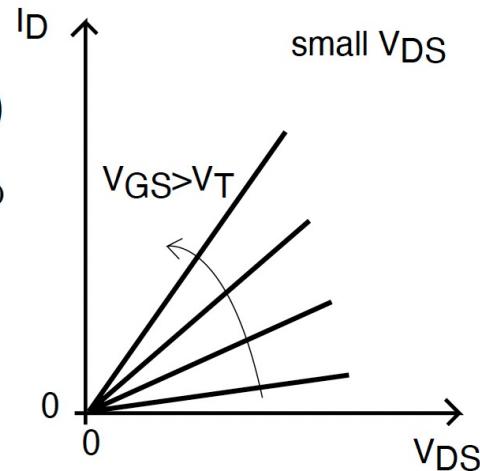

For small  $V_{DS}$ :  $I_D \simeq \frac{W}{L} \mu_n C_{ox} (V_{GS} - V_T) V_{DS}$

Linear (triode) regime

- $V_{DS} \uparrow \rightarrow I_D \uparrow$  (higher lateral electric field)

- $V_{GS} \uparrow \rightarrow I_D \uparrow$  (higher electron concentration)

- $L \uparrow \rightarrow I_D \downarrow$  (lower lateral electric field)

- $W \uparrow \rightarrow I_D \uparrow$  (wider conduction channel)

# MOSFET: the output characteristics

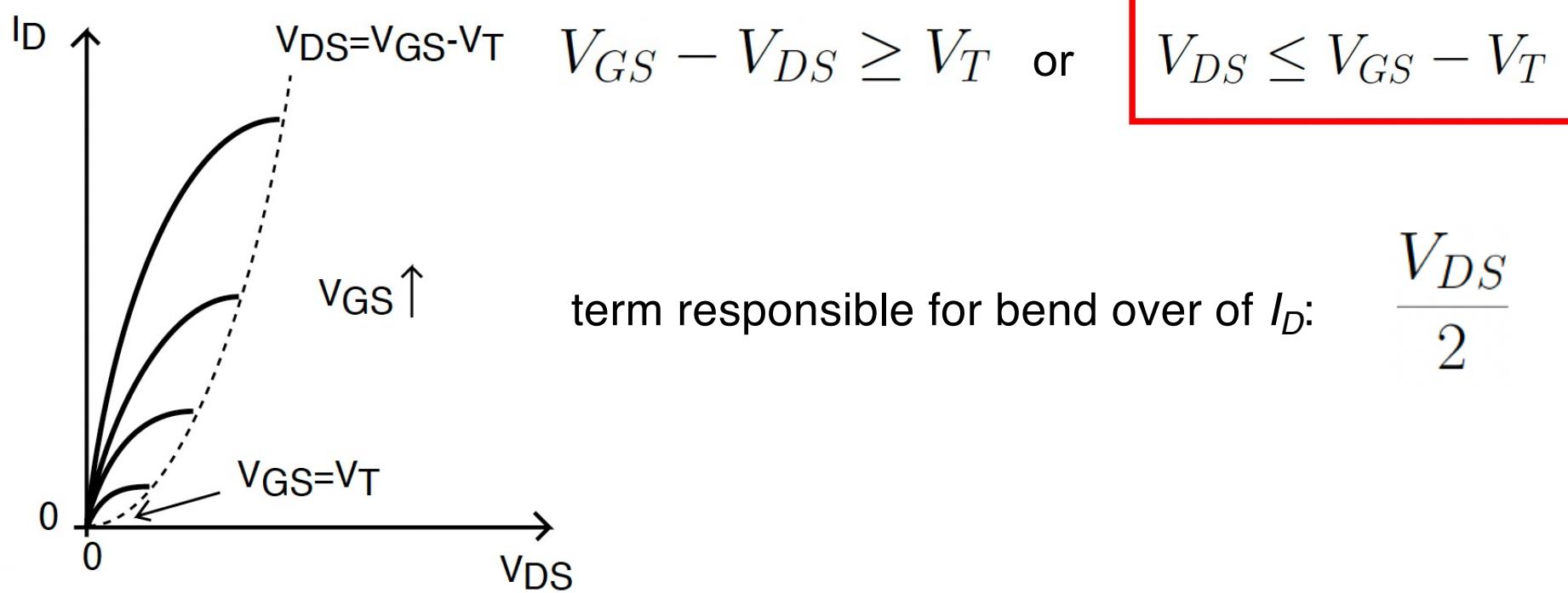

$$I_D = \frac{W}{L} \mu_n C_{ox} \left( V_{GS} - \frac{V_{DS}}{2} - V_T \right) V_{DS}$$

This general equation is valid for

$V_{GS} - V_c(y) \geq V_T$  for any  $y$

Worst point is  $y = L$ , where  $V_c(y) = V_{DS}$ , hence, equation valid if

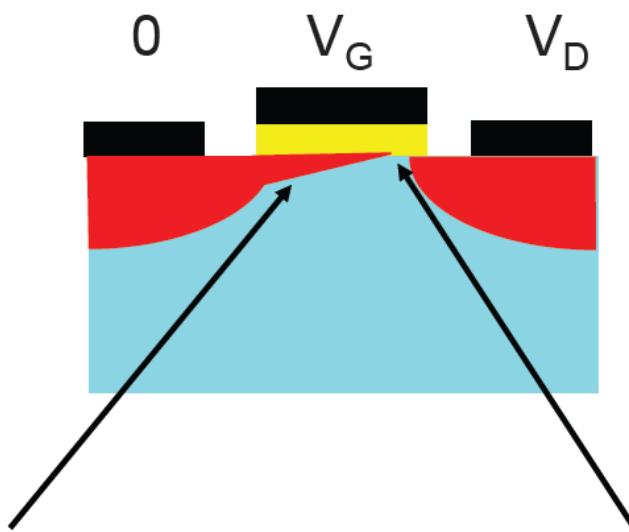

# Saturation (1)

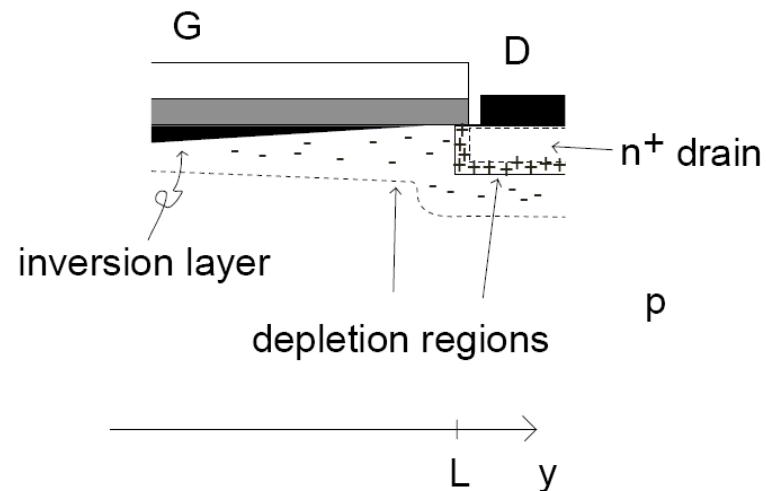

What happens when  $V_{DSsat} = V_{GS} - V_T$ ?

- Charge control relation at drain end of channel:

$$Q_n(L) = -C_{ox}(V_{GS} - V_{DS} - V_T) = 0$$

- No inversion layer at end of channel  $\Rightarrow$  **Pinch-off**

- At pinchoff:

- electron concentration small but not zero

- electrons move fast because electric field is very high

- dominant electrostatic feature: acceptor charge

- there is no barrier to electron flow (on the contrary!)

## Saturation (2)

$$I_D = \frac{W}{L} \mu_n C_{ox} \left( V_{GS} - \frac{V_{DS}}{2} - V_T \right) V_{DS}$$

$$V_{DSsat} = V_{GS} - V_T$$

$$I_{Dsat} = \frac{W}{2L} \mu_n C_{ox} (V_{GS} - V_T)^2$$

Drain current at pinchoff:

- $I_{Dsat} \propto 1/L$

- $I_{Dsat} \propto W; C_{ox}$

$$V_c(L) = V_{DSsat} = V_{GS} - V_T$$

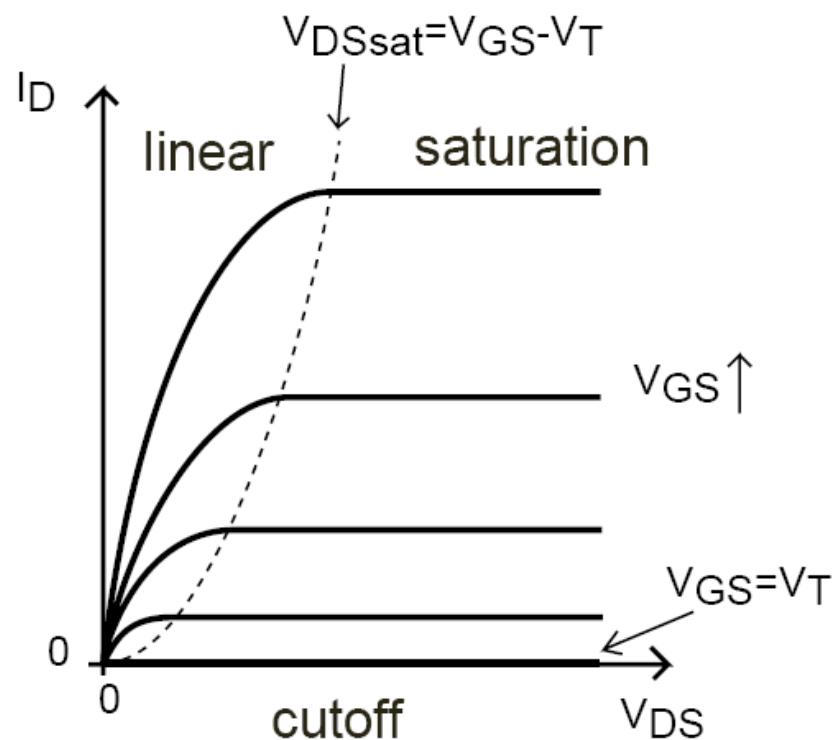

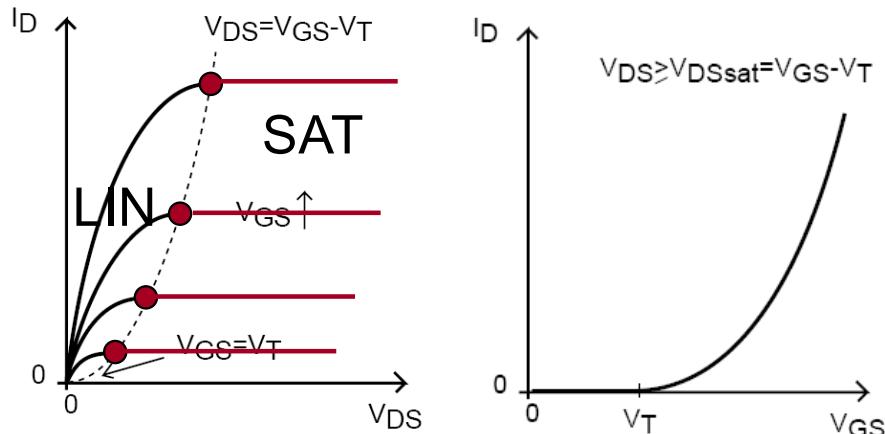

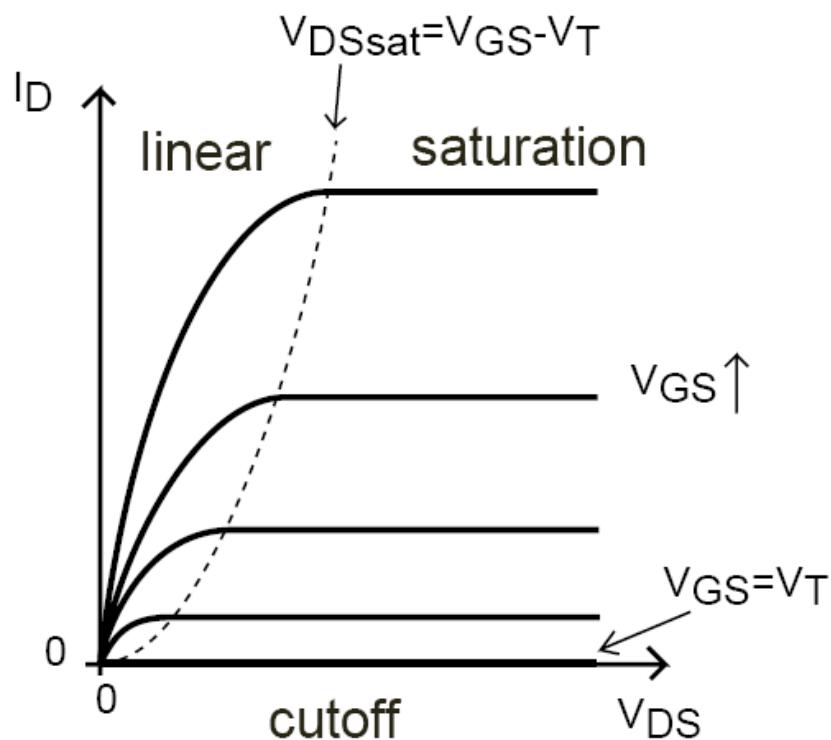

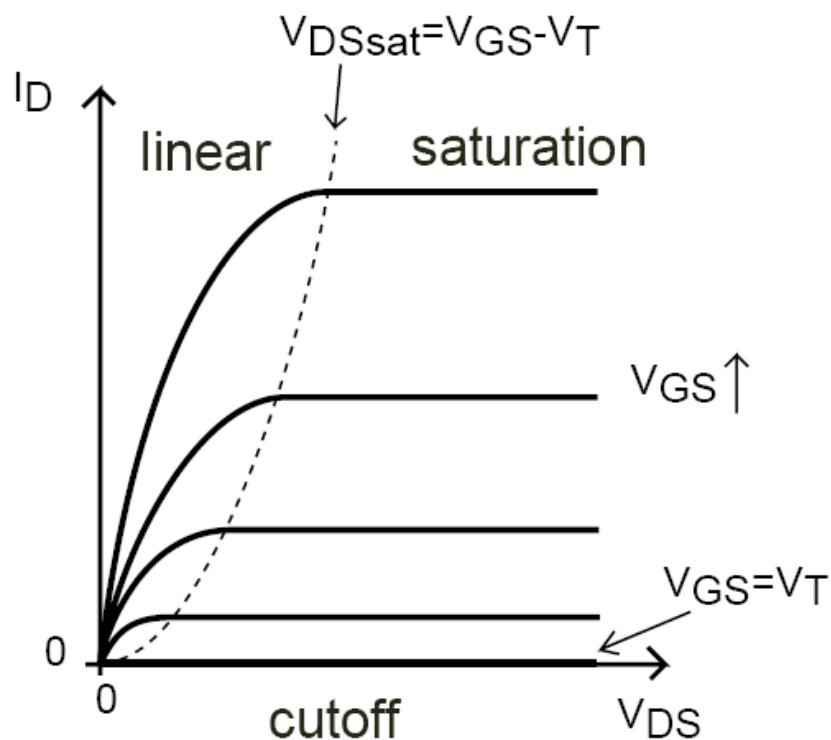

# MOSFET: regions of operation

- **Cutoff:**  $V_{GS} < V_T$  ( $V_{GD} < V_T$ ): no inversion layer anywhere underneath gate

$$I_D = 0$$

- **Linear:**  $V_{GS} > V_T$ , ( $V_{DS} > 0$ ): inversion layer everywhere underneath gate

$$I_D = \frac{W}{L} \mu_n C_{ox} \left( V_{GS} - \frac{V_{DS}}{2} - V_T \right) V_{DS}$$

- **Saturation:**

$$V_{GS} > V_T, V_{DS} > V_G - V_T = V_{Dsat}$$

$$I_{Dsat} = \frac{W}{2L} \mu_n C_{ox} (V_{GS} - V_T)^2$$

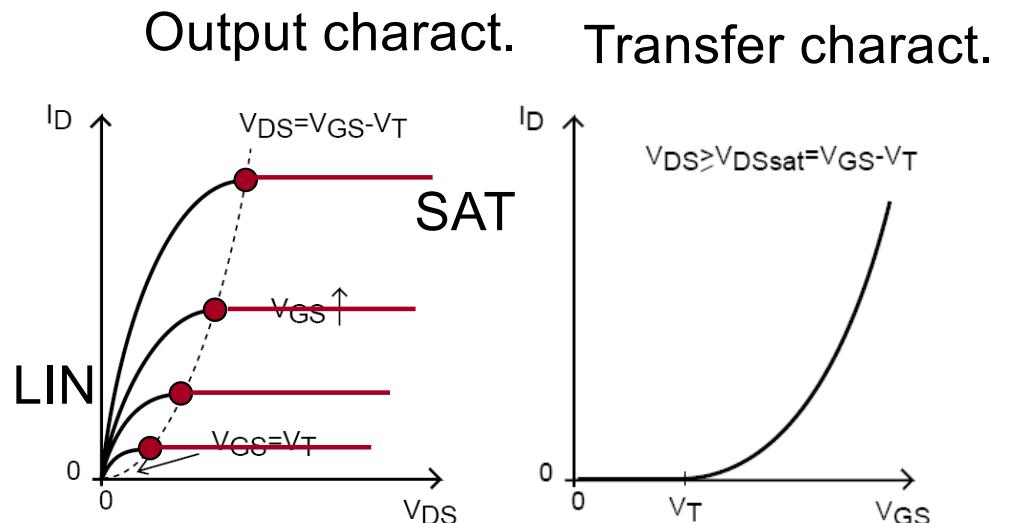

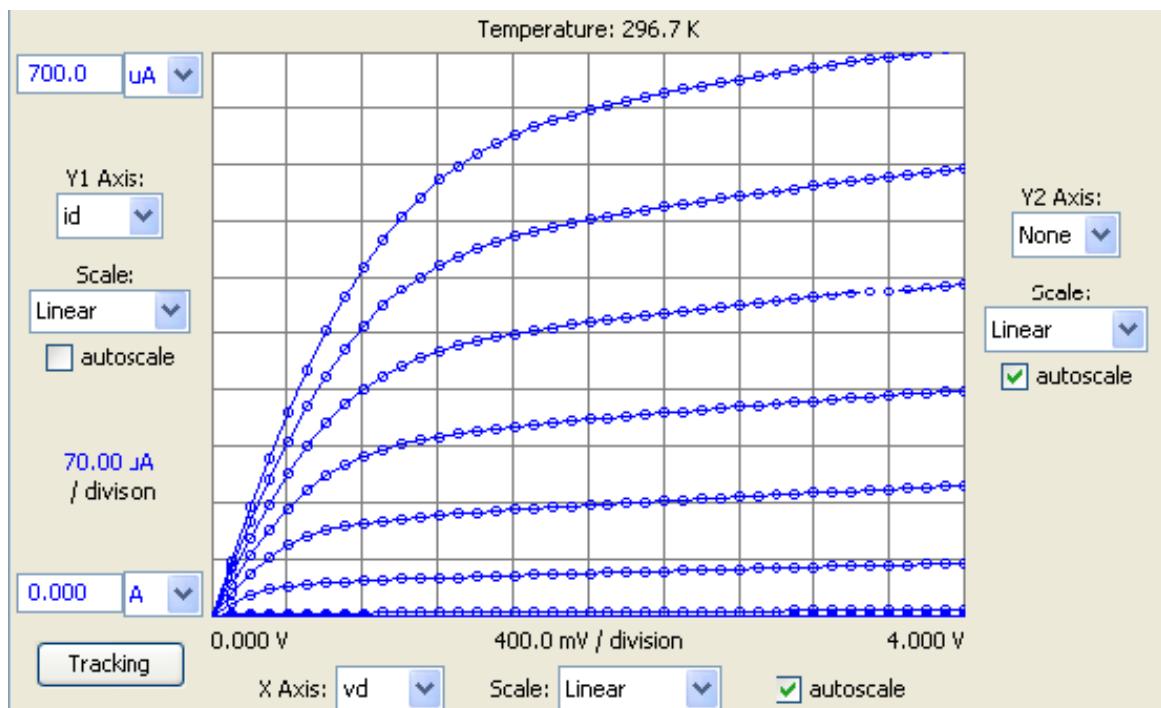

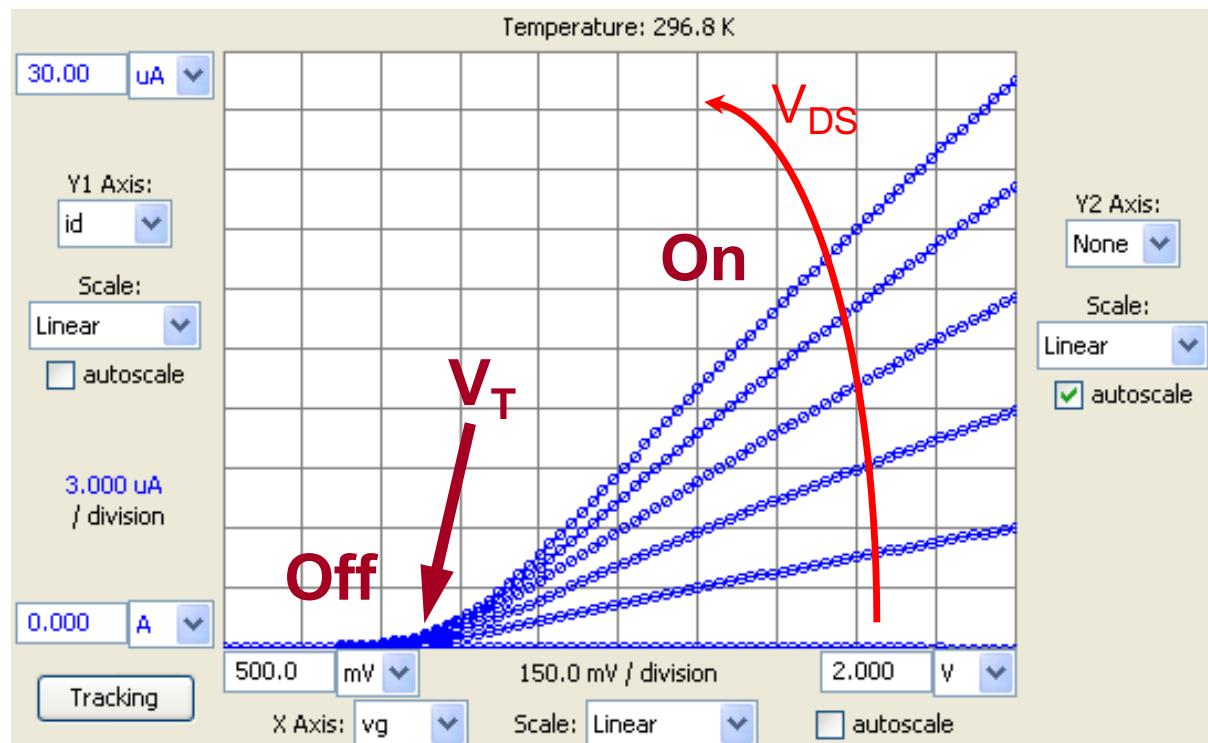

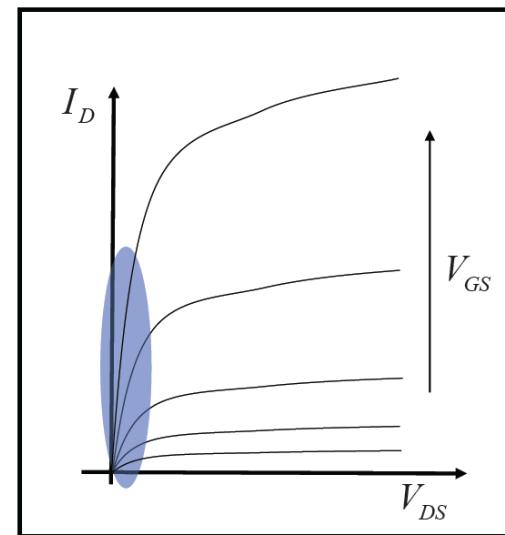

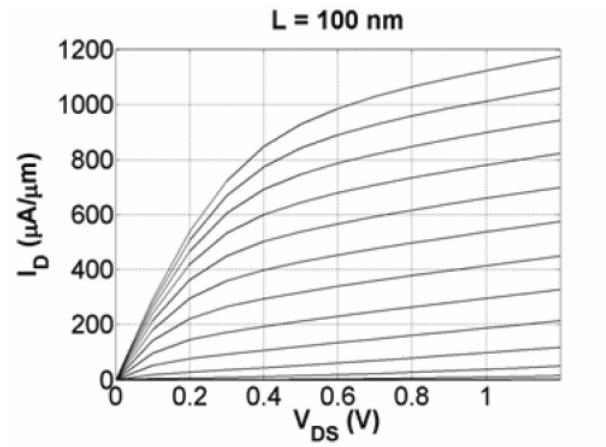

# MOSFET: I-V characteristics

Output characteristics:  $I_{DS} - V_{DS}$  @  $V_{GS} = \text{parameter}$

$(V_{GS}=0 - 4 \text{ V}, \Delta V_{GS}=0.5 \text{ V})$ :

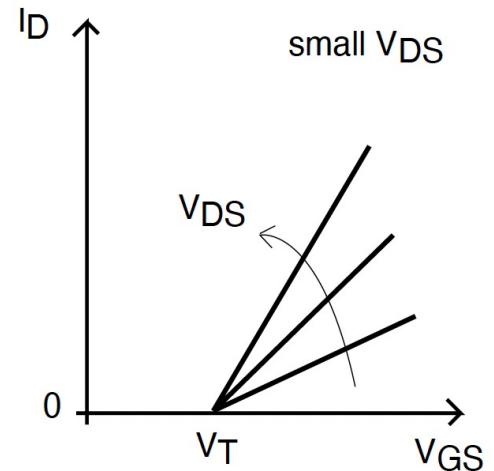

# MOSFET: I-V characteristics

Transfer characteristics:  $I_{DS}$  –  $V_{GS}$

@  $V_{DS}$  = parameter

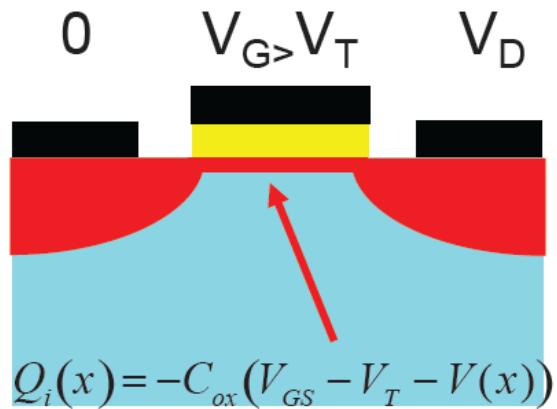

# MOSFET in linear region, strong inversion @ $V_{GS} > V_T$ and low drain voltage, $V_{DS}$

$$I_D = W Q_i(x) v_x(x)$$

$$I_D = W C_{ox} (V_{GS} - V_T) \mu_{eff} \mathcal{E}_x$$

$$\mathcal{E}_x = \frac{V_{DS}}{L}$$

$$I_D = \frac{W}{L} \mu_{eff} C_{ox} (V_{GS} - V_T) V_{DS}$$

Also modeled as resistor:

$$R_{DS} = \frac{V_{DS}}{I_{DS}} = \frac{L}{W \mu_{eff} C_{ox} (V_G - V_T)}$$

$\mu_{eff}$  is the **effective electron mobility**

## MOSFET: pinch-off at high $V_{DS}$

$$Q_i(x) = -C_{ox}(V_{GS} - V_T - V(x))$$

$$V(x) = (V_{GS} - V_T)$$

$$Q_i(x) \approx 0$$

Cross-over between the linear and saturation regimes

(note that in BJT devices totally different terminology is adopted)

# Saturation (1)

What happens when  $V_{DSsat} = V_{GS} - V_T$ ?

- Charge control relation at drain end of channel:

$$Q_n(L) = -C_{ox}(V_{GS} - V_{DS} - V_T) = 0$$

- No inversion layer at end of channel  $\Rightarrow$  **Pinch-off**

- At pinchoff:

- electron concentration small but not zero

- electrons move fast because electric field is very high

- dominant electrostatic feature: acceptor charge

- there is no barrier to electron flow (on the contrary!)

## Saturation (2)

$$I_{Dsat} = \frac{W}{2L} \mu_n C_{ox} (V_{GS} - V_T)^2$$

Drain current at pinchoff:

$\propto$  lateral electric field

$$\propto V_{DSsat} = V_{GS} - V_T$$

$\propto$  electron concentration

$$\propto V_{GS} - V_T$$

$$\Rightarrow I_{Dsat} \propto (V_{GS} - V_T)^2$$

- $I_{Dsat} \propto 1/L$

Output charact. Transfer charact.

$$V_c(L) = V_{DSsat} = V_{GS} - V_T$$

# MOSFET Scaling

## Key questions

- How does the channel geometry affects impact MOSFET operation in **saturation**? Does the pinch-off point represent a block to the current flow?

- What is the **short channel effect**?

- How should one scale down the MOSFET: what is **constant-field scaling** rule? How the scaling affects the device (technological) parameters?

- What are the **CMOS performance factors**?

# MOSFET: regions of operation

- **Cutoff:**  $V_{GS} < V_T$  ( $V_{GD} < V_T$ ): no inversion layer anywhere underneath gate

$$I_D = 0$$

- **Linear:**  $V_{GS} > V_T$ , ( $V_{DS} > 0$ ): inversion layer everywhere underneath gate

$$I_D = \frac{W}{L} \mu_n C_{ox} \left( V_{GS} - \frac{V_{DS}}{2} - V_T \right) V_{DS}$$

- **Saturation:**

$$V_{GS} > V_T, V_{DS} > V_{G} - V_T = V_{Dsat}$$

$$I_{Dsat} = \frac{W}{2L} \mu_n C_{ox} (V_{GS} - V_T)^2$$

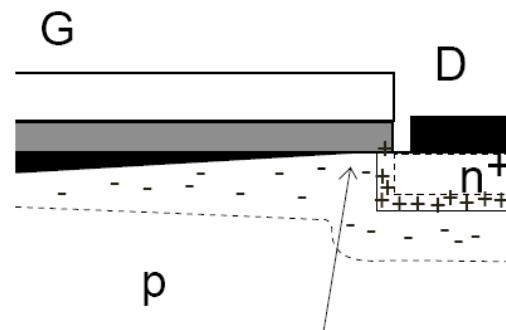

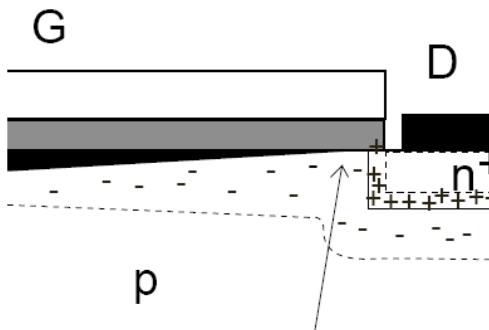

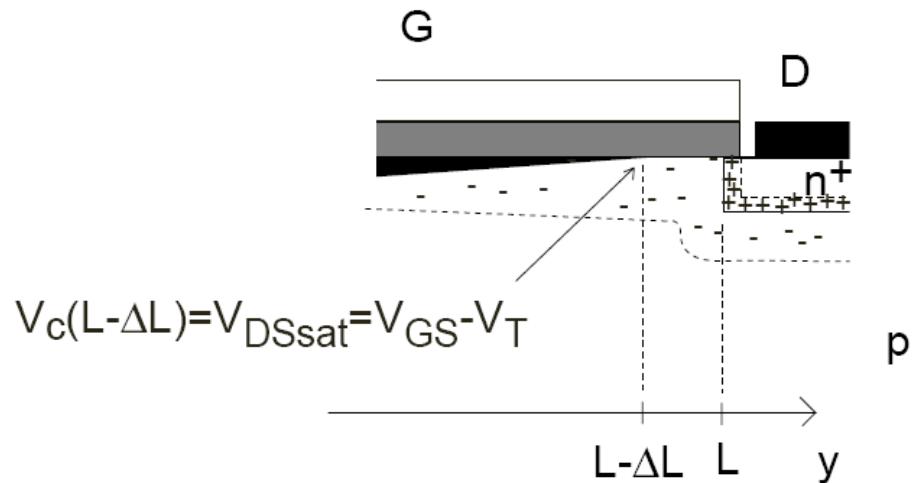

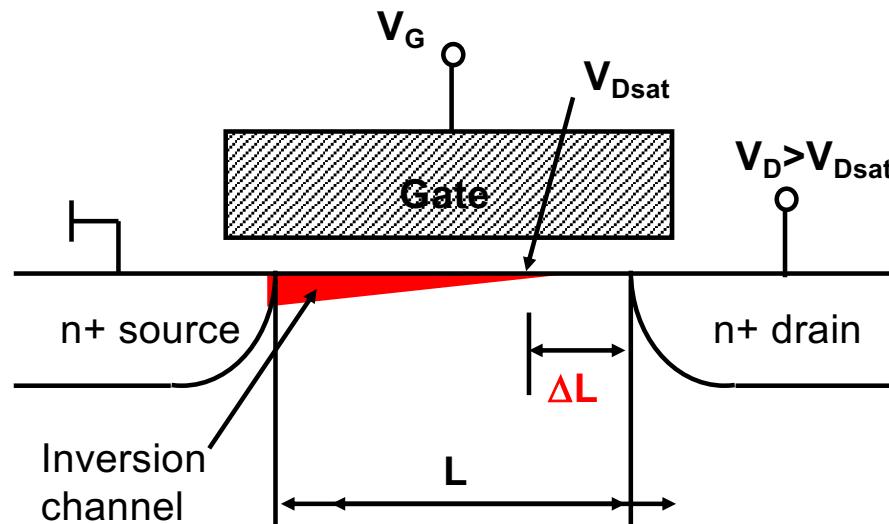

## MOSFET: channel length modulation (1)

What happens if  $V_{DS} > V_{DSsat} = V_{GS} - V_T$ ?

Depletion region separating pinch-off point and drain widens

(just like in reverse biased pn junction)

**Channel length modulation:**  $V_{DS} \uparrow \Rightarrow L_{\text{channel}} \downarrow \Rightarrow I_D \uparrow$

## MOSFET: channel length modulation (2)

Drain current continues to increase after saturation ( $V_D > V_{D_{sat}}$ )

- Pinch-off

- Equivalent length:  $L - \Delta L$

$$I_D = \frac{I_{Dsat}}{1 - (\Delta L / L)}$$

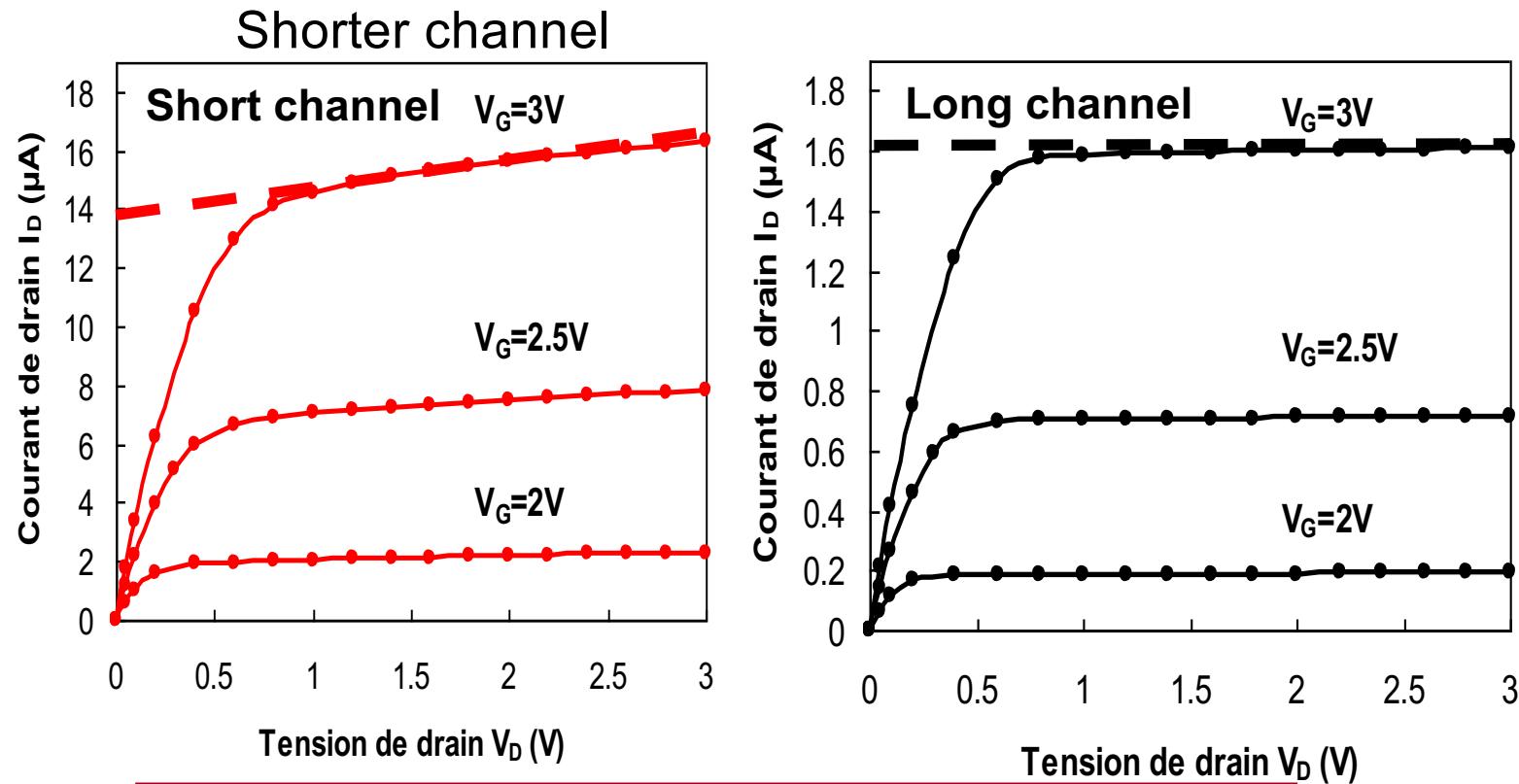

## Long channel

$$\Delta L \ll L \rightarrow I_D \approx I_{D\text{sat}} = \text{ct.} (V_D)$$

## Short channel

$\Delta L \uparrow$  with  $V_D \rightarrow I_D \uparrow$  with  $V_D$

# MOSFET: channel length modulation

How it looks like and is modeled?

$$I_D = I_{Dsat} = \frac{W}{2L} \mu_n C_{ox} (V_{GS} - V_T)^2 [1 + \lambda (V_{DS} - V_{DSSat})]$$

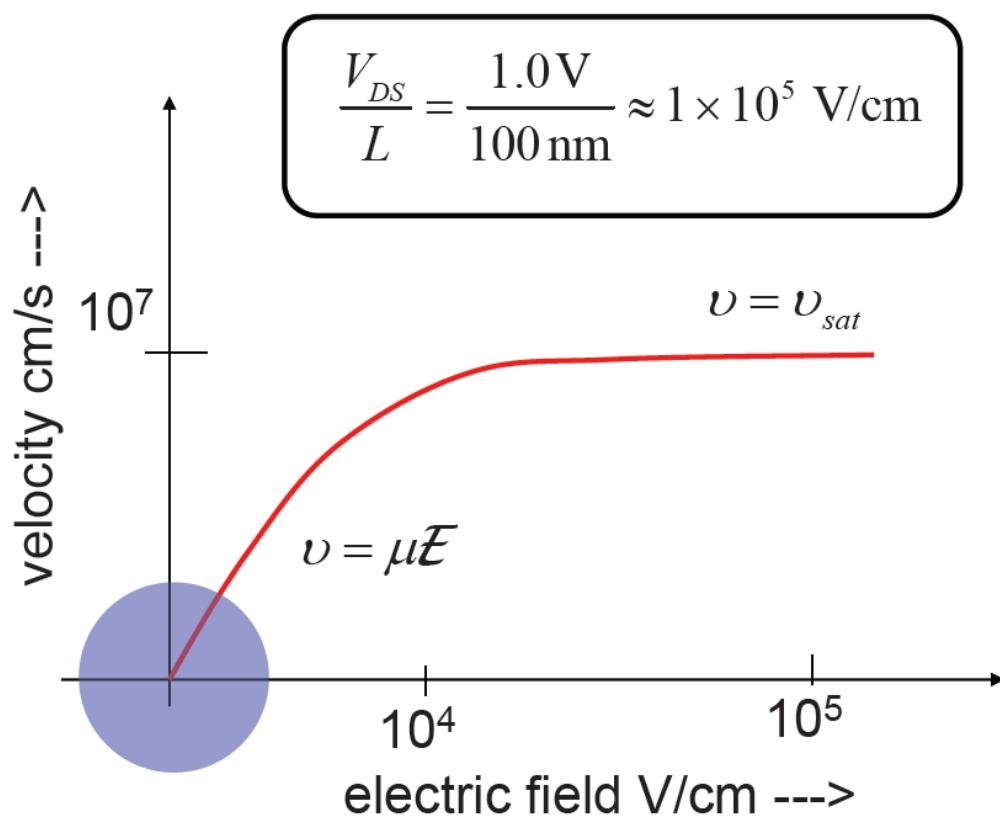

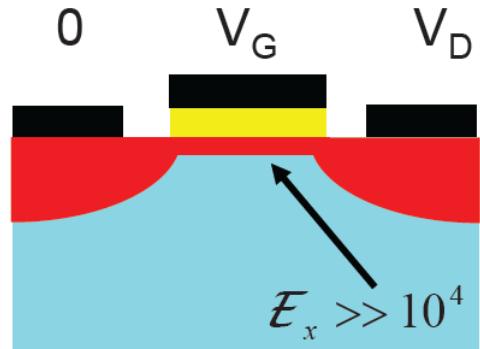

## MOSFET: velocity saturation @ small channel length (1)

In short-channel MOSFETs with velocity saturation, the current saturates **earlier** and becomes **limited by  $v_{sat}$**  rather than pinch-off.

# MOSFET: velocity saturation @ small channel length (2)

$$I_D = W Q_i(x) v_x(x)$$

$$I_D = W C_{ox} (V_{GS} - V_T) v_{sat}$$

$$I_D = W C_{ox} v_{sat} (V_{GS} - V_T)$$

saturation means that the **current is linearly dependent on  $V_{GS}$**  rather than quadratically, as in the long-channel model

# Small channel effects: length scale

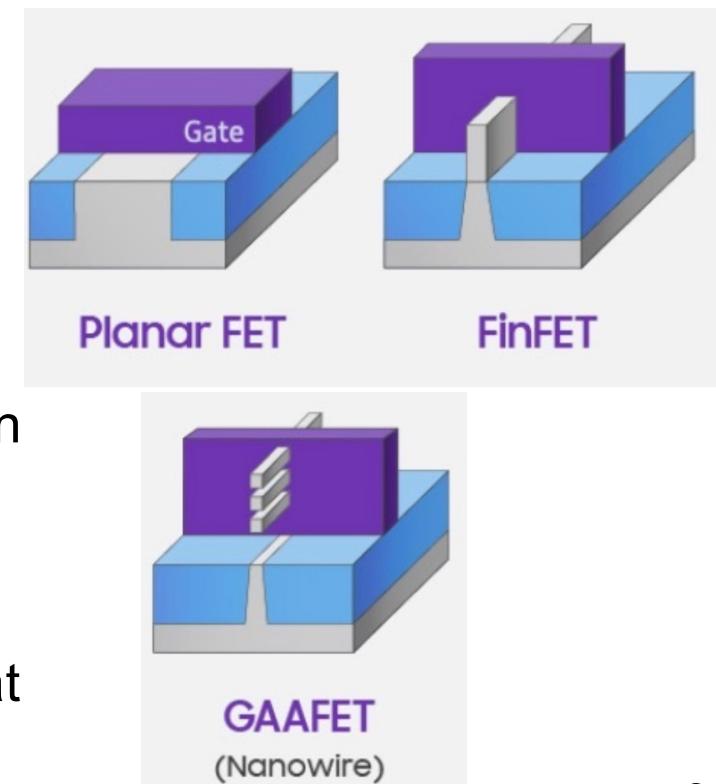

- For modern MOSFETs, short-channel effects start to become significant when the channel length drops below roughly 100 nm. The effects increase dramatically as the length approaches 20 nm and below.

In today's tech (5nm/3nm nodes):

- The physical gate length is often below 20 nm, and controlling SCEs becomes extremely difficult.

- That's why planar bulk MOSFETs are largely replaced by FinFETs or even Gate-All-Around FETs (GAAFETs) in cutting-edge nodes.

- These 3D structures provide better electrostatic control over the channel, which helps to better manage SCEs at extreme scaling.

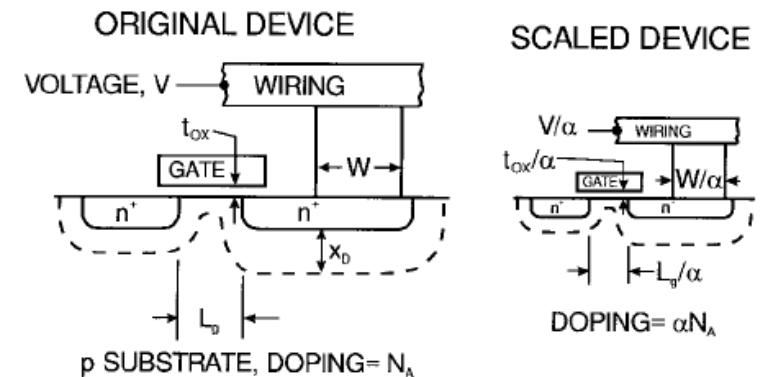

# MOSFET scaling: Dennard's rule

*proposed in 1974 by Robert Dennard and his team at IBM*

*describes how to **scale down** MOSFET dimensions to make smaller, faster, and more power- efficient transistors — the principle that fueled Moore's Law for decades*

- keeping short-channel effects under control by scaling down vertical and horizontal dimensions while also proportionally decreasing the applied voltages and increasing the substrate doping (decreasing the depletion width)

- the principle of constant-field scaling lies in scaling the device voltages and dimensions by the same factor  $\alpha$ , so that the electric field remains unchanged

## Before scaling:

Channel length =  $L_{eff}$

Oxide thickness =  $t_{ox}$

Channel doping =  $N_B$

Operating voltage =  $V_{DD}$

## After scaling:

$L_{eff} / \alpha$

$t_{ox} / \alpha$

$N_B \times \alpha$

$V_{DD} / \alpha$

- Most important: once the device dimensions and power-supply are scaled, the circuit speeds up by the same factor!

# MOSFET scaling: Dennard's rule

| Parameter          | Scales by          | Description                                |

|--------------------|--------------------|--------------------------------------------|

| Channel length (L) | $1/\kappa$         | Shorter channel                            |

| Width (W)          | $1/\kappa$         | Smaller width                              |

| Supply voltage (V) | $1/\kappa$         | Lower voltage                              |

| Threshold voltage  | $1/\kappa$         | Also scaled to maintain switching behavior |

| Capacitance (C)    | $1/\kappa$         | Smaller gate area                          |

| Current (I)        | $1/\kappa$         | Lower current due to lower voltage         |

| Delay time (t)     | $1/\kappa$         | Faster switching                           |

| Power per circuit  | $1/\kappa^2$       | Less power per transistor                  |

| Power density      | $\approx$ constant | Because area and power scale together      |

**post-Dennard era came in mid-2000s**

Subthreshold leakage increased with smaller transistors

Inability to reduce threshold and supply voltages much further (leads to performance and reliability issues)

High power density causing thermal problems

# Summary- I: 3 principle regimes of MOSFET operation

- **Cutoff:**  $V_{GS} < V_T$  ( $V_{GD} < V_T$ ): no inversion layer anywhere underneath gate

$$I_D = 0$$

- **Linear:**  $V_{GS} > V_T$ , ( $V_{DS} > 0$ ): inversion layer everywhere underneath gate

$$I_D = \frac{W}{L} \mu_n C_{ox} \left( V_{GS} - \frac{V_{DS}}{2} - V_T \right) V_{DS}$$

- **Saturation:**  $V_{GS} > V_T$ ,  $V_{DS} > V_G - V_T = V_{Dsat}$

$$I_{Dsat} = \frac{W}{2L} \mu_n C_{ox} (V_{GS} - V_T)^2$$

## Summary- II: scaling MOSFET

- Short-channel effects impact planar FET scaling and must be taken into account

- Channel length modulation and velocity saturation are among the most important factors associated with the short channel

- Dennard scaling rule offer an approach that permits keeping the short channel effects under control

- Modern technology nodes belong to “post-Dennard era” where alternative 3D geometries are required.