# **Neural Interfaces**

**Neural Amplifiers**

Mahsa Shoaran IEM and Neuro-X Institutes

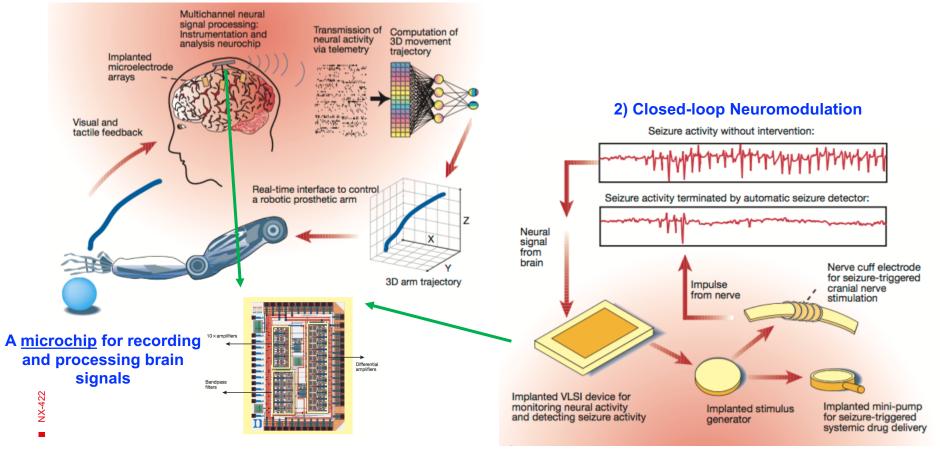

# **Recap: Two Types of Neural Interfaces**

1) Brain-Machine Interface

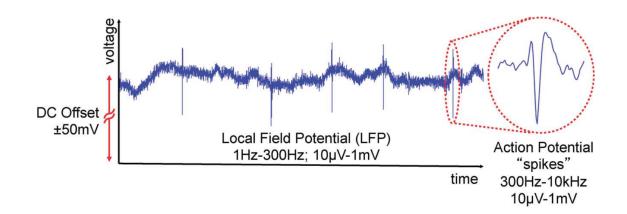

- < 300 Hz : Local Field Potentials (LFP)</p>

- 300 10kHz : Single-Unit Activity (AP or "spikes")

- Local Field Potential (LFP) electrical activity of all cells averaged over some spatial neighborhood

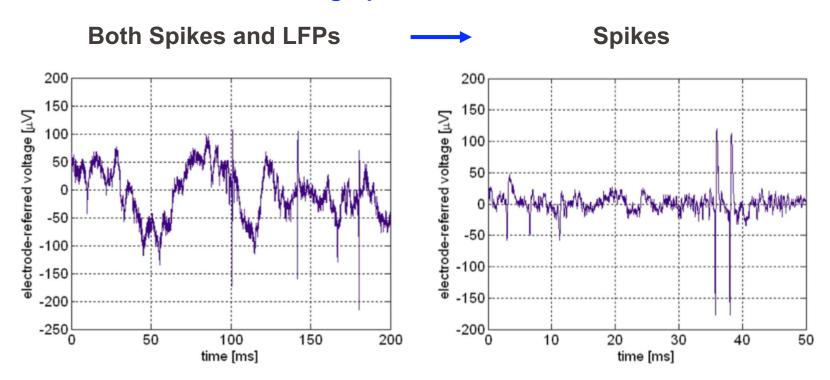

- High-pass filtering gives spikes

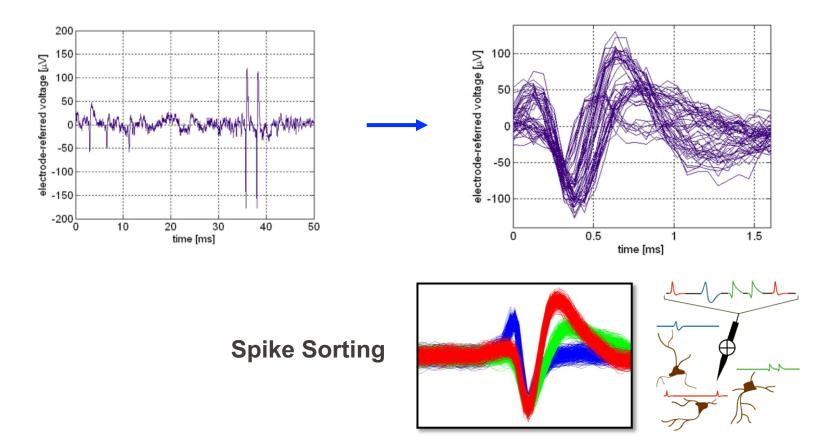

# **Spike/LFP Recording**

#### **High-pass filter at 300Hz**

# **Spike Sorting**

NX-422

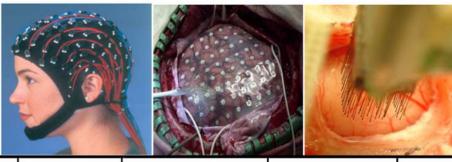

# **Comparison: EEG, ECoG, LFP, and AP**

|                  | EEG         | ECoG                            | LFP                       | AP                           |  |

|------------------|-------------|---------------------------------|---------------------------|------------------------------|--|

| Bandwidth        | 0.5-50Hz    | 1-500Hz                         | 1-500Hz                   | 250-10kHz                    |  |

| Amplitude        | 1-50µV      | 1-500µV                         | 10μ-1mV                   | 10μ-1mV                      |  |

| Spacing          | 3cm         | 0.2-10mm                        | 0.1-1mm                   | 0.1-1mm                      |  |

| Invasive         | No          | Craniotomy,<br>no neural damage | Craniotomy, neural damage | Craniotomy,<br>neural damage |  |

| Area<br>Coverage | Whole Brain | ~ cm² ,<br>whole brain          | ~ mm²                     | ~ mm²                        |  |

| Stability        | Decades     | Decades                         | Years                     | Months                       |  |

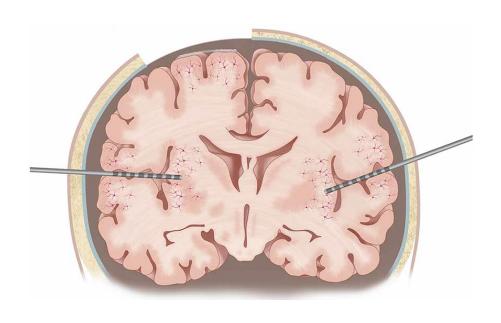

# **Stereo EEG (sEEG)**

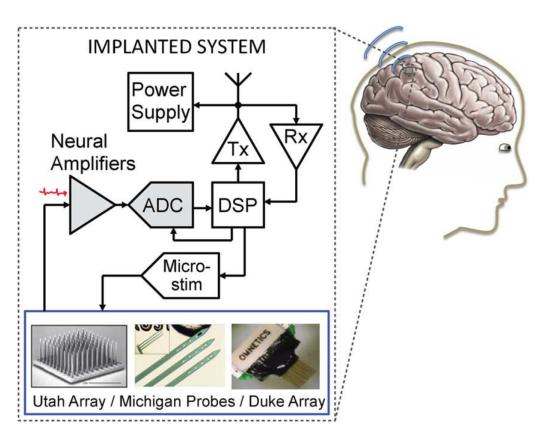

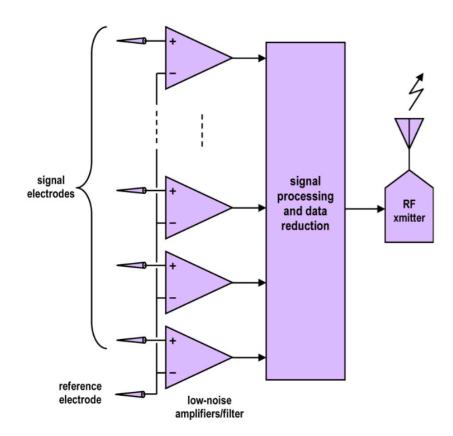

# **Circuit Block Diagram of a Neural Interface**

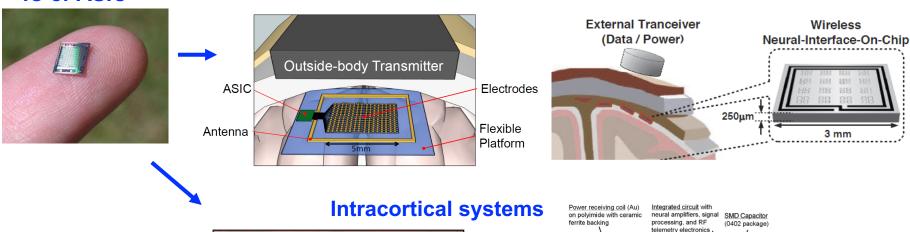

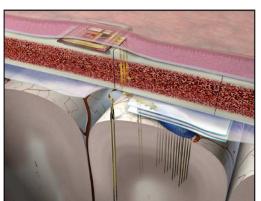

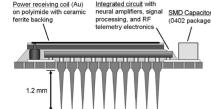

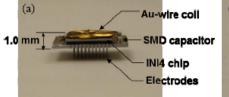

# **Cortical and Intracortical Systems**

9

#### **Cortical or ECoG-based systems**

### **EPFL**

# **Neural Recording IC**

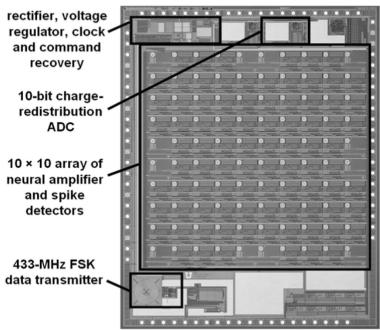

Microchips include amplification, filtering, digitization, compression, processing: feature extraction/spike detection/classification, wireless power and data telemetry, bias generation, stimulation, ...

Power and area are highly limited

Die photo of 4.7 mm x 5.9 mm chip

# **Low-Noise Neural Amplifier**

### **EPFL**

# **Design Requirements for Neural Amplifier**

- 1. Sufficiently low input-referred noise to resolve spikes as small as 10 μV in amplitude

- 2. Sufficient dynamic range to record spikes or LFPs as large as 1–2 mV in amplitude

- 3. Much higher input impedance than the electrode-tissue interface

- 4. Amplify signals in the frequency bands of interest (roughly 300 Hz–10 kHz for spikes and 1–300 Hz for local field potentials)

- 5. Block DC offsets present at the electrode-tissue interface to prevent saturation of the amplifier

### **EPFL**

# **Design Requirements for Neural Amplifier**

- 1. Sufficiently low input-referred noise to resolve spikes as small as 10 μV in amplitude

- 2. Sufficient dynamic range to record spikes or LFPs as large as 1–2 mV in amplitude

- 3. Much higher input impedance than the electrode-tissue interface

- 4. Amplify signals in the frequency bands of interest (roughly 300 Hz–10 kHz for spikes and 1–300 Hz for local field potentials)

- 5. Block DC offsets present at the electrode-tissue interface to prevent saturation of the amplifier

- 6. Consume little silicon area and use few or no off-chip components to minimize size

- 7. High common-mode rejection ratio to minimize interference from 50/60 Hz power line noise, and a high power-supply rejection ratio if power supply noise is significant (e.g., from ac inductive power links);

- 8. Consume low power to limit the chronic heating of surrounding tissue to less than 1°C.

. . .

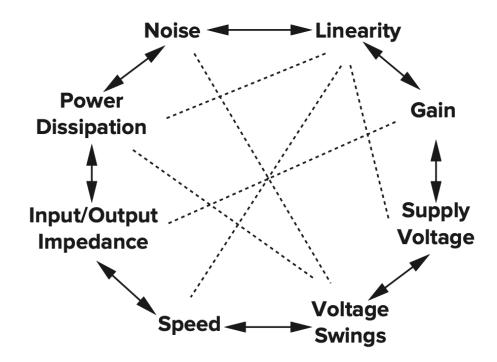

# **Design Trade-offs**

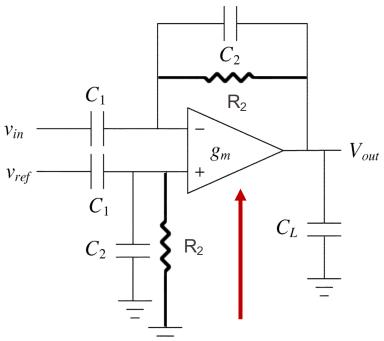

## **Neural Amplifier: Capacitive Feedback Architecture**

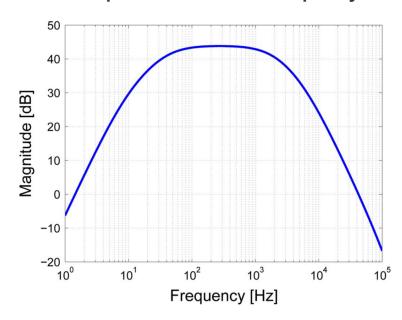

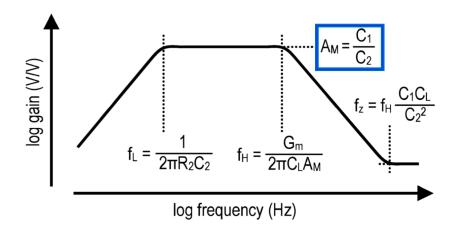

#### **Amplifier Gain versus Frequency**

**OTA**:

**Operational Transconductance Amplifier**

## **Neural Amplifier: Transfer Function**

$$\frac{v_{\text{out}}}{v_{\text{in+}} - v_{\text{in-}}} = \frac{C_1}{C_2} \cdot \frac{1 - sC_2/G_m}{\left(\frac{1}{sR_2C_2} + 1\right) \left(s\frac{C_LC_1}{G_mC_2} + 1\right)}$$

$$= A_M \frac{1 - s/(2\pi f_z)}{\left(\frac{2\pi f_L}{s} + 1\right) \left(\frac{s}{2\pi f_H} + 1\right)}.$$

# **Neural Amplifier: Capacitive Feedback Architecture**

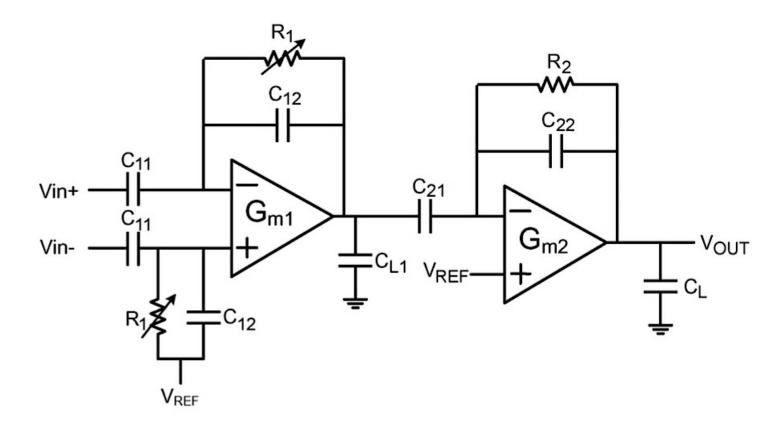

# **Neural Amplifier: Multi-Stage, Higher Gain**

## **Neural Implants: Power, Area, Noise, ...**

A typical performance and comparison table

|                                   | JSSC ,08<br>[3] | [4]<br>JSSC '07 | [6]<br>BioCAS '07 | [7]<br>ISSCC '10 | [24]<br>VLSI '11 | This<br>Work     |

|-----------------------------------|-----------------|-----------------|-------------------|------------------|------------------|------------------|

| Power (µW)                        | 15              | 42.2            | 7.56              | 0.64             | 43               | 5.04             |

| IRNoise (μV), Spike               | 7.0             | 5.1             | 3.06              | 14               | 2.2              | 4.9              |

| Spike Bandwidth                   | 5kHz            | 5kHz            | 5.3kHz            | 6.2kHz           | 10kHz            | 10kHz            |

| NEF                               | 4.6             | 9.8             | 2.67              | 6.5              | 5                | 5.99             |

| NEF <sup>2</sup> •V <sub>DD</sub> | 63.48           | 316.9           | 20                | 33.8             | 30               | 17.96            |

| IRNoise (μV), LFP                 | -               | -               | 1.66*             | -                | 14               | 4.3              |

| LFP Bandwidth                     | -               | -               | 300Hz*            | -                | 100Hz            | 300Hz            |

| CMRR (dB)                         | -               | -               | 66                | 59               | -                | 75               |

| PSRR (dB)                         | -               | -               | 75                | 71               | -                | 64               |

| V <sub>DD</sub> (V)               | 3               | 3.3             | 2.8               | 0.8              | 1.2              | 0.5              |

| Area (mm²)                        | 0.04            | 0.16            | 0.16              | 0.4**            | 0.2**            | 0.013            |

| Technology                        | 0.35µm          | 0.5µm           | 0.5µm             | 0.13µm           | 0.13µm           | 65nm             |

| Blocks included in comparison     | LNA, BPF        | LNA,<br>BPF     | LNA, BPF          | LNA, BPF         | LNA, BPF,<br>ADC | LNA, BPF,<br>ADC |

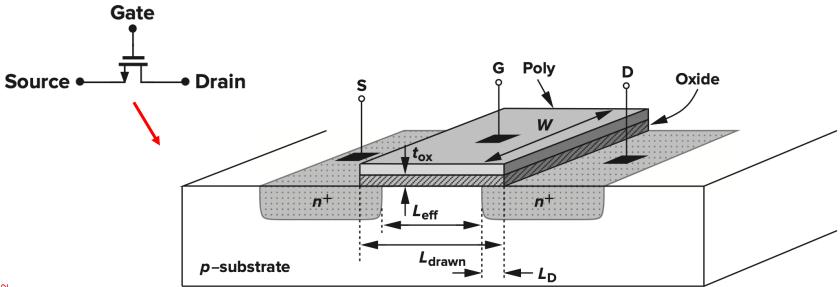

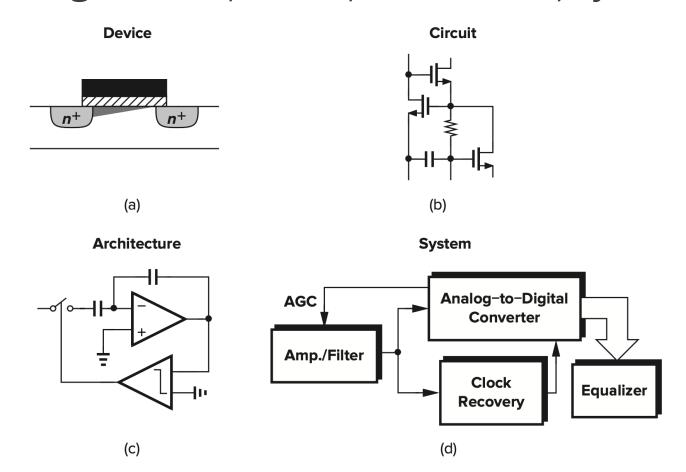

## IC Design: Device, Circuit, Architecture, System

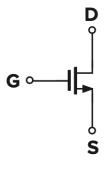

### **Transistor?**

#### **NMOS**

$$I_D pprox rac{1}{2} \mu_n C_{ox} rac{W}{L} (V_{GS} - V_{TH})^2$$

### **EPFL** NMOS Transistor

- An n-type MOS (NMOS) device on a p-type substrate

- a heavily-doped polysilicon (conductor) operating as the gate

- a thin layer of silicon dioxide (SiO<sub>2</sub>) **insulating** the gate from the substrate

- two heavily-doped n regions: source and drain terminals