## NX-422 EXERCISE 3 – Implantable Electronics Solutions

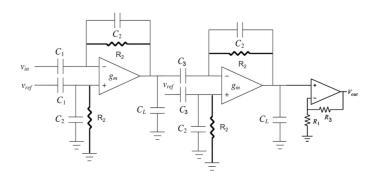

1. Let's check the details of the three-stage neural amplifier.

(a) The equation for the overall mid-band gain:

$$|A_{V}|_{3-Stage} = |A_{V1} \times A_{V2} \times A_{V3}| = \left(\frac{C_{1}}{C_{2}}\right) \times \left(\frac{C_{3}}{C_{2}}\right) \times \left(\frac{R_{1} + R_{3}}{R_{1}}\right)$$

(b) Assuming  $C_2=C_u$ , we will find the values of  $C_1$  and  $C_3$  in terms of  $C_u$ . Ignore  $C_L$ , and assume  $R_1$ =40k $\Omega$  and  $R_3$ =60k $\Omega$ . For our calculations, we are asked to have a total mid-band gain of 1000 and minimize the chip area by minimizing the total capacitance.

## Let's start:

$$\textbf{C}_2 = \textbf{C}_u$$

assume  $\textbf{C}_1 = \textbf{M} \times \textbf{C}_u$  and  $\textbf{C}_3 = \textbf{N} \times \textbf{C}_u$

We know that  $R_1$ =40k $\Omega$  and  $R_3$ =60k $\Omega$ . Hence,  $\frac{R_1+R_3}{R_1}=\frac{100k\Omega}{40k\Omega}=2.5$ .

$$|A_V|_{3-Stage} = 1000 \rightarrow \left(\frac{c_1}{c_2}\right) \times \left(\frac{c_3}{c_2}\right) = \frac{1000}{2.5} = 400 = M \times N$$

Total capacitance excluding C<sub>L</sub> is

$$= 2C_1 + 2C_2 + 2C_3 + 2C_2 = 2 \times (M + N + 2) \times C_{11}$$

Area

$$\propto 2 \times (M + N + 2) \times C_{n}$$

$$2 \times (\mathbf{M} + \mathbf{N} + 2) \times \mathbf{C_u} = 2 \times \left(\mathbf{M} + \frac{400}{\mathbf{M}} + 2\right) \times \mathbf{C_u} = f(\mathbf{M})$$

To minimize the total capacitance and area  $\frac{df}{dM}=0 \rightarrow 1-\frac{400}{M^2}=0 \rightarrow M_{opt}=20$

$$\rightarrow C_1 = 20C_u \text{ and } C_3 = \frac{400}{20}C_u = 20C_u$$

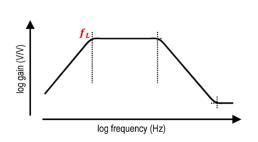

(c) The amplifier's bandwidth is set by the first stage and  $C_2 = 400 \mathrm{fF}$ .

$$\begin{split} f_L = & \frac{1}{2 \times \pi \times R_2 \times C_2} = 1 \text{ Hz} \\ & C_2 = C_u = 400 \text{ fF} \\ R_2 = & \frac{1}{2 \times \pi \times 400 \times 10^{-15}} = 3.98 \times 10^{11} \\ & = 0.398 \text{ T}\Omega \end{split}$$

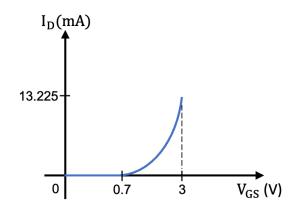

**2.** We will draw the drain current of an NMOS  $(I_D)$  as a function of  $V_{GS}$  where  $V_{GS}$  varies from  $0 \rightarrow 3V$ .

•

$$\frac{W}{L} = \frac{50}{0.5}$$

,  $V_{DS} = 3$  V,  $V_{TH} = 0.7$  V,  $\mu_n C_{ox} = 50$   $\mu A/V^2$  and  $\lambda = 0$ .

Saturation condition:  $V_{DS} > V_{GS} - V_{TH}$

$3V > (0 \rightarrow 3V) - 0.7V$ , which means that the assumption is correct. The transistor is in saturation.

The drain current equation for the saturation ( $\lambda = 0$ ):

$$I_D = \frac{1}{2}\,\mu_n C_{ox} \frac{W}{L}\,(V_{GS}-V_{TH})^2 \label{eq:ID}$$

$$I_D = \frac{1}{2} \times (50 \frac{\mu A}{V^2}) \times \frac{50}{0.5} \times (V_{GS} - 0.7)^2$$

$$I_D = 2.5 \frac{\text{mA}}{V^2} (V_{GS} - 0.7)^2$$

$$\text{At } V_{GS}=3V \rightarrow I_D=13.225 mA$$

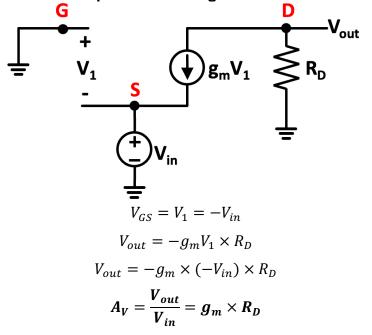

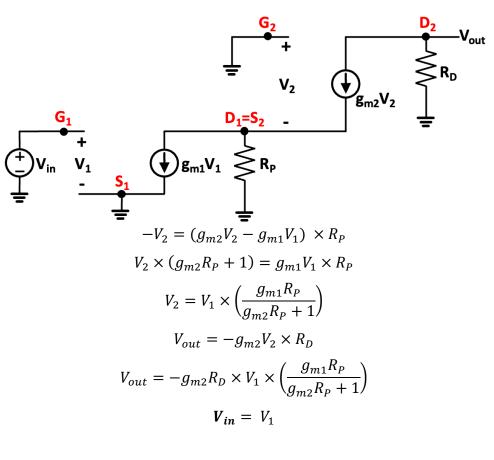

## 3. (a) Common-Gate Amplifier Small-Signal Model:

## (b) Cascode Amplifier Small-Signal Model:

$$A_{V} = \frac{V_{out}}{V_{in}} = -\frac{g_{m1}g_{m2}R_{P}R_{D}}{g_{m2}R_{P} + 1}$$