# **Neural Interfaces**

Mahsa Shoaran

IEM and Neuro-X Institutes

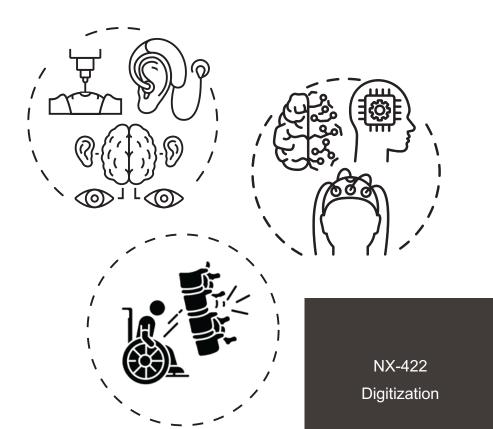

#### **Recap: Neural Amplifier: OTA architecture**

- a) 2-stage

- b) Current mirror

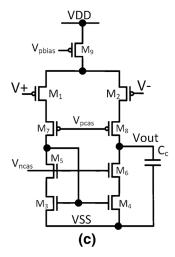

- c) Telescopic cascode

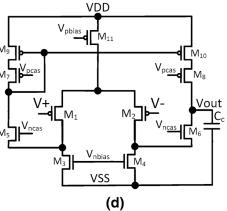

- d) Folded cascode

(b)

## **Recap: Noise basics**

Thermal noise:

Flicker (1/f) noise:

#### **EPFL**

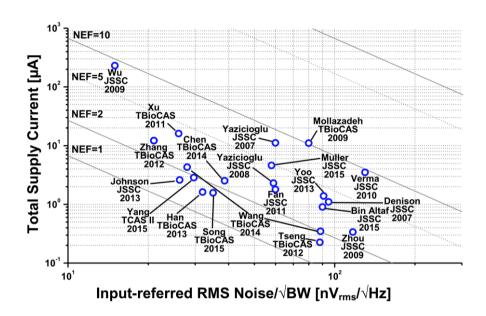

## **Noise Efficiency Factor (NEF)**

- V<sub>rms,in</sub>: The total input-referred noise

- I<sub>tot</sub>: The total current drain

- V<sub>t</sub>: The thermal voltage

- BW: The 3-dB bandwidth of the system

$$NEF = V_{rms,in} \sqrt{\frac{2I_{tot}}{\pi V_t \cdot 4kT \cdot BW}}$$

## **DC Offset Cancellation with DC-Coupled Amplifier**

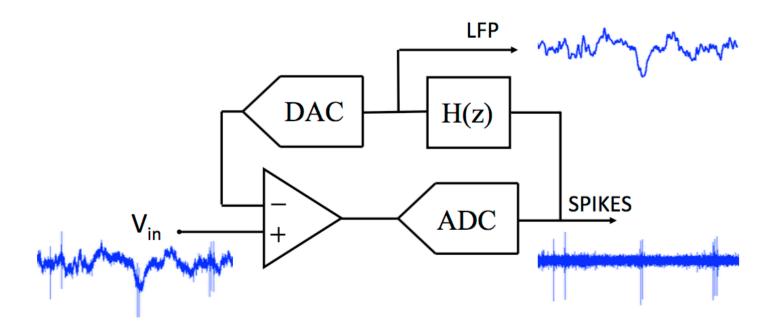

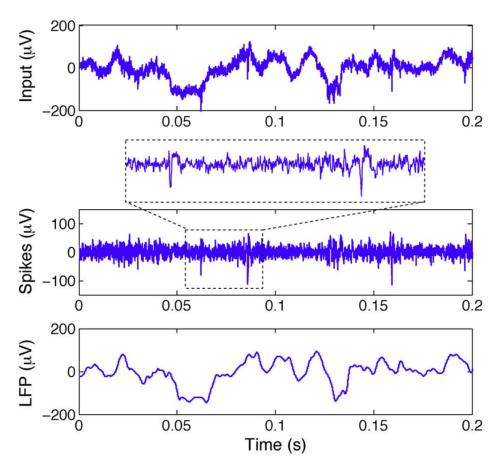

## **Spike and LFP Measurements**

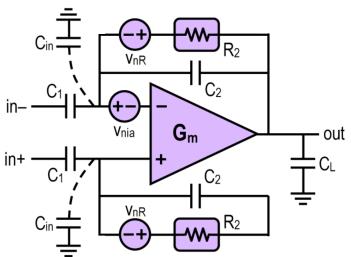

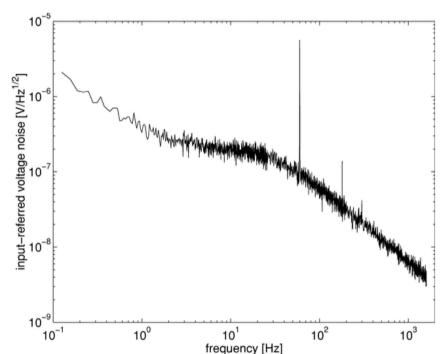

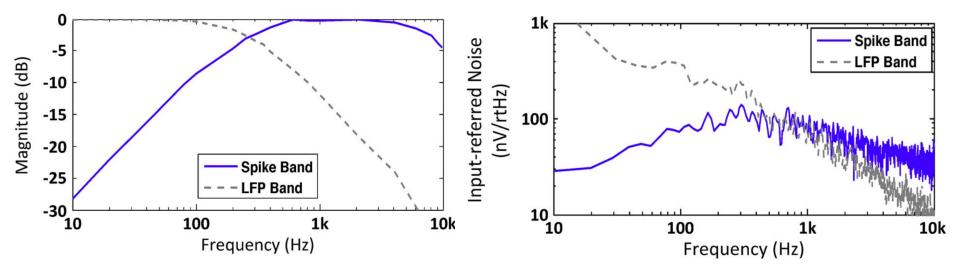

## **Amplifier gain and input-referred noise**

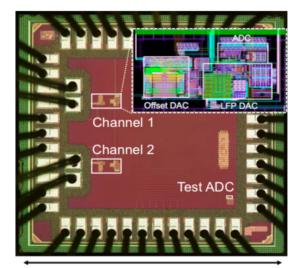

# Die photo and performance smmary

1.2mm

|                         | Power  | Area                  |

|-------------------------|--------|-----------------------|

| Merged Amplifier-DAC    | 4.13μW | 0.0037mm <sup>2</sup> |

| Summing Amplifier & DAC | 0.66μW | 0.0045mm <sup>2</sup> |

| ADC                     | 0.24μW | 0.0018mm²             |

| Digital Filters         | 0.1μW* | 0.0017mm <sup>2</sup> |

|                                   | JSSC '09 | [4]<br>JSSC '07 | [6]<br>BioCAS '07 | [7]<br>ISSCC '10 | [24]<br>VLSI '11 | This<br>Work     |

|-----------------------------------|----------|-----------------|-------------------|------------------|------------------|------------------|

| Power (µW)                        | 15       | 42.2            | 7.56              | 0.64             | 43               | 5.04             |

| IRNoise (μV), Spike               | 7.0      | 5.1             | 3.06              | 14               | 2.2              | 4.9              |

| Spike Bandwidth                   | 5kHz     | 5kHz            | 5.3kHz            | 6.2kHz           | 10kHz            | 10kHz            |

| NEF                               | 4.6      | 9.8             | 2.67              | 6.5              | 5                | 5.99             |

| NEF <sup>2</sup> •V <sub>DD</sub> | 63.48    | 316.9           | 20                | 33.8             | 30               | 17.96            |

| IRNoise (μV), LFP                 | -        | -               | 1.66*             | -                | 14               | 4.3              |

| LFP Bandwidth                     | -        | -               | 300Hz*            | -                | 100Hz            | 300Hz            |

| CMRR (dB)                         | -        | -               | 66                | 59               | -                | 75               |

| PSRR (dB)                         | -        | -               | 75                | 71               | -                | 64               |

| V <sub>DD</sub> (V)               | 3        | 3.3             | 2.8               | 0.8              | 1.2              | 0.5              |

| Area (mm²)                        | 0.04     | 0.16            | 0.16              | 0.4**            | 0.2**            | 0.013            |

| Technology                        | 0.35µm   | 0.5µm           | 0.5µm             | 0.13µm           | 0.13µm           | 65nm             |

| Blocks included in comparison     | LNA, BPF | LNA,<br>BPF     | LNA, BPF          | LNA, BPF         | LNA, BPF,<br>ADC | LNA, BPF,<br>ADC |

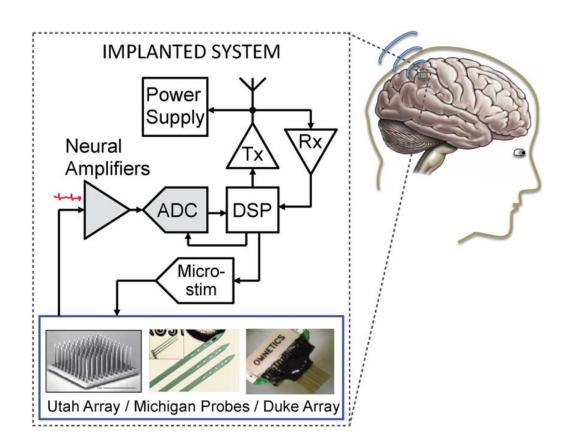

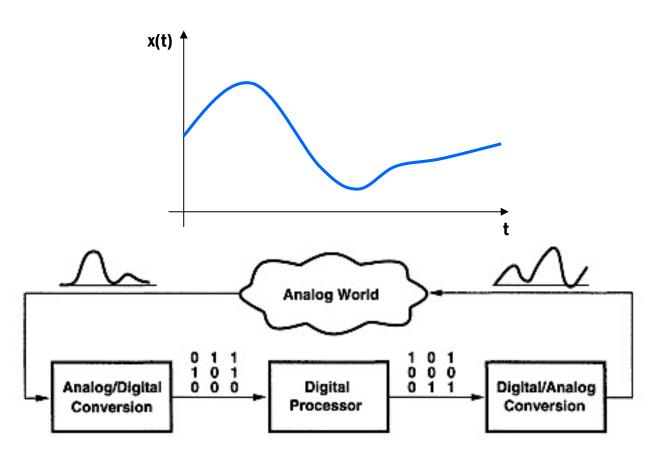

#### **Circuit Block Diagram of a Neural Interface: ADC**

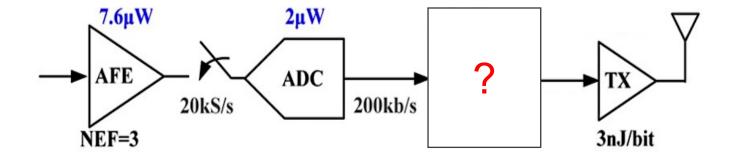

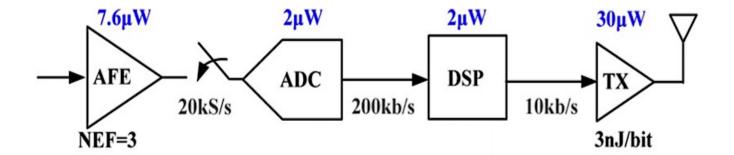

#### **Neural Interface: ADC and Compression**

The typical circuit blocks used in sensors for medical monitoring and their associated energy cost and power consumption

#### **Neural Interface: ADC and Compression**

The typical circuit blocks used in sensors for medical monitoring and their associated energy cost and power consumption

#### **EPFL**

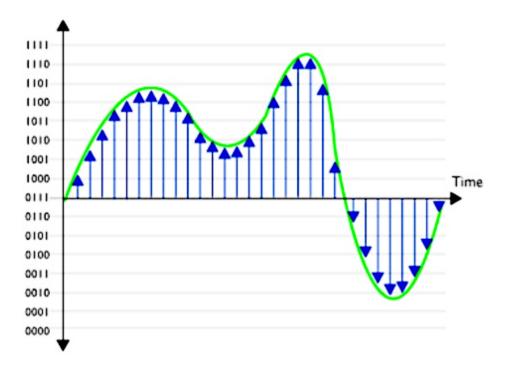

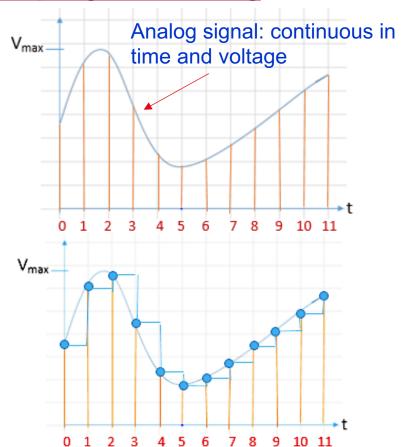

#### **Analog to Digital Conversion**

After amplification and filtering, signal is digitized (sampled at a fixed rate)

## **Analog and Digital Signals**

## **Digital Data Acquisition**

#### Foundation: Shannon/Nyquist sampling theorem

"if you sample densely enough (at the Nyquist rate), you can perfectly reconstruct the original analog data"

A bandlimited analog signal can be perfectly reconstructed from a sequence of samples if the sampling rate fs exceeds 2f<sub>max</sub> samples per second, where f<sub>max</sub> is the highest frequency in the original signal.

#### **EPFL**

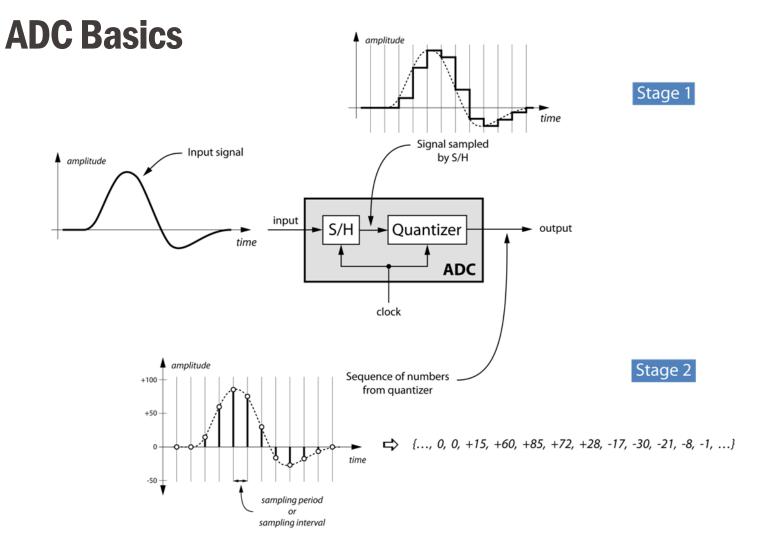

#### **ADC Operation**

#### **Sampling and Holding**

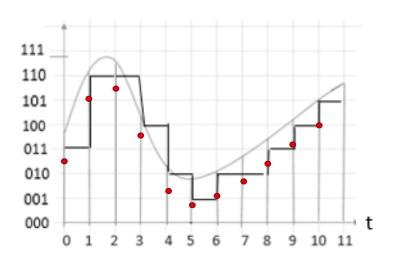

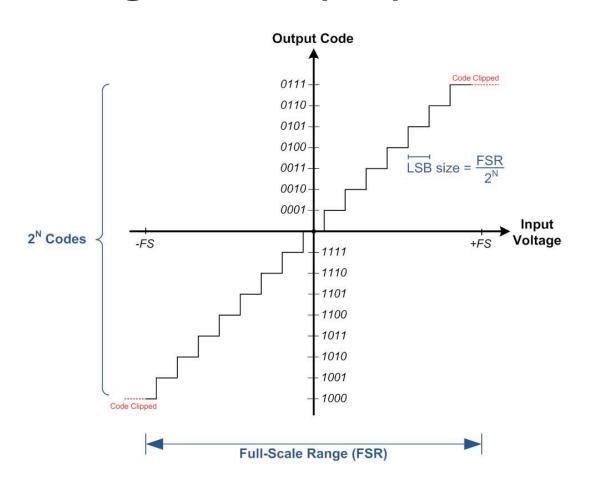

#### **Quantization and Encoding**

Sequence of digital codes: 011, 110, 110, 100, 010, 001, 001, 010, 011, 100, 101, ...

#### The least significant bit (LSB)

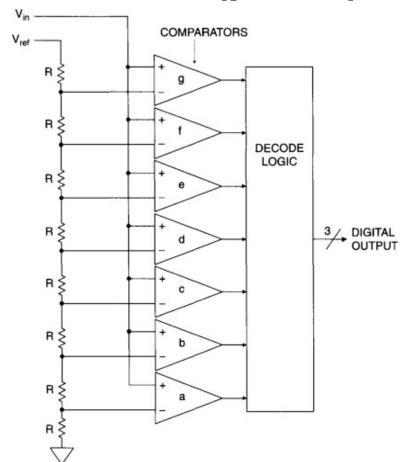

## 3-bit flash (parallel) ADC

- An n-bit flash ADC uses 2<sup>n</sup>-1 comparators, 2<sup>n</sup> resistors and a decode logic.

- Pros: the fastest type of ADC.

- Cons: limited resolution, expensive, large power consumption and low accuracy

- Applications: Data acquisition, sampling oscilloscope and highdensity disk drives.

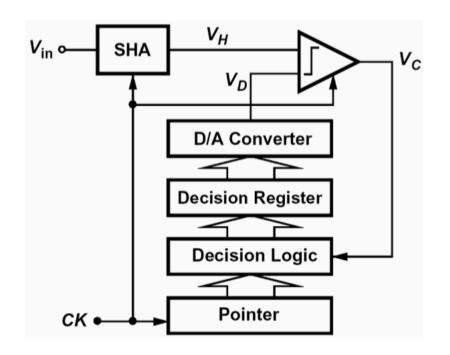

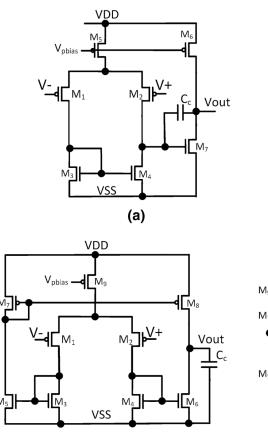

#### **Successive-approximation-register (SAR) ADC**