# The Bimorph Cantilever

Advanced Microfabrication Practicals (MICRO-373) - EPFL - Spring 2024

| 0. | INTR  | ODUCTION AND GENERAL INFORMATION                                              | 1  |

|----|-------|-------------------------------------------------------------------------------|----|

|    | 0.1.  | Organization                                                                  | 2  |

|    | 0.2.  | OVERVIEW OF THE FABRICATION PROCESS                                           | 3  |

|    | 0.3.  | MASKS                                                                         | 4  |

|    | 0.4.  | DIMENSIONS OF THE DEVICES                                                     | 6  |

| 1. | THEC  | RY AND DESIGN                                                                 | 7  |

|    | 1.1.  | 1 <sup>st</sup> session : Theory – 01.03.2024                                 | 7  |

|    | 1.2.  | ADVICE FOR THE A1 REPORTS                                                     | 9  |

|    | 1.3.  | $2^{\text{ND}}$ Session: design and simulation - $08.03.2024$                 | 10 |

|    | 1.3.1 | Modification of 2b – group assignments                                        | 10 |

|    | 1.3.2 | Modification of 1b – free design                                              | 11 |

|    | 1.3.3 | KOH etching simulation                                                        | 11 |

| 2. | CLEA  | NROOM FABRICATION AT CMI – SEE SCHEDULE                                       | 14 |

|    | 2.1.  | GENERAL INSTRUCTIONS                                                          | 14 |

|    | 2.2.  | DETAILED FABRICATION STEPS                                                    | 14 |

|    | 2.2.1 | « RCA » cleaning, wet oxidation and chromium evaporation [Runcard §1]         | 15 |

|    | 2.2.2 | Metallization by chromium evaporation [Runcard §2]                            | 15 |

|    | 2.2.3 | Photolithography for the Cr tracks (mask LAYER 1 METAL) [Runcard §3]          | 16 |

|    | 2.2.4 |                                                                               |    |

|    | 2.2.5 | Electrical/optical characterization of the metallic layer [Runcard §4.4-4.5]  | 18 |

|    | 2.2.6 | . Photolithography for the SiO₂ beams (mask LAYER 2 OXIDE) [Runcard §5]       | 20 |

|    | 2.2.7 |                                                                               |    |

|    | 2.2.8 | Optical and mechanical characterization [Runcard §6.4-6.5]                    | 23 |

|    | 2.2.9 | KOH anisotropic etching of Silicon (performed by the assistants) [Runcard §7] | 24 |

|    | 2.3.  | HOW TO REPORT THE FABRICATION STEPS                                           | 25 |

| 3. | CHA   | RACTERIZATION OF THE DEVICES AT LMIS1 – SEE THE SCHEDULE                      | 26 |

|    | 3.1.  | SETUP                                                                         | 26 |

|    | 3.2.  | TASKS                                                                         | 26 |

| 4. | FINA  | L REPORT                                                                      | 27 |

| 5. | REFE  | RENCES                                                                        | 28 |

# 0. Introduction and general information

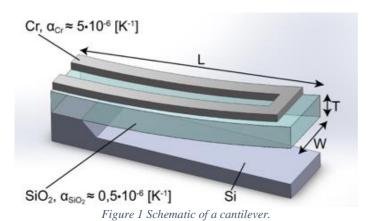

The goal of this practical work is to create thermal micro-actuators consisting of micro-cantilevers made out of silicon dioxide (SiO<sub>2</sub>) and covered by chromium (Cr) meander-shaped electrical tracks and contact pads (Figure 1).

The micro-actuator is actuated by Joule effect: the current injected into the chromium track, with a certain electric resistance, dissipates energy and heats up the materials. The difference between thermal expansion coefficients of the two materials (chromium and silicon oxide) induces the movement of the micro-cantilever. Depending on the frequency of the excitation signal and on the mechanical resonance frequency of the cantilever, the amplitude of the movement will change. This micro-actuator is used as a micro-optical element or an electromechanical actuator.

# 0.1. Organization

This practical work is divided in two preparation sessions and four 4h-sessions in the cleanroom. Sessions dedicated to characterization and Finite Element modeling will take place in the labs at LMIS1. The following sessions are briefly described below.

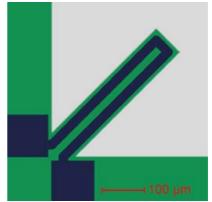

**Theory and Mask Design:** These are two preparation sessions, during which the students will study the theory of the behavior of this device and will design their own cantilevers (Figure 2). This will help you understand the influence of the structure on the behavior of the actuator. All the groups will attend the sessions together.

There are 2 important submissions regarding the preparation sessions.

- Friday, 1 March, 14h15-18h: Session on theory

- **Tuesday, 5 March 13h:** submission of your answers to the preparation questions studied during the theory session + feedback on the softwares.

- Friday, 8 March, 14h15-18h: Session on design and simulation.

- **Tuesday 12 March, 13h:** submission of your designs and answers to the questions studied in the design session.

**Cleanroom sessions:** These 4h-long sessions will take place in cleanroom at CMi to produce the cantilevers. First, patterning the Cr tracks, then patterning the SiO2 cantilevers. The KOH release will be performed by the teaching assistants (TAs). Each group will perform all the cleanroom sessions with the supervision of a teaching assistant.

Characterization session: This session will request the students to characterize the fabricated devices in the lab (LMIS1).

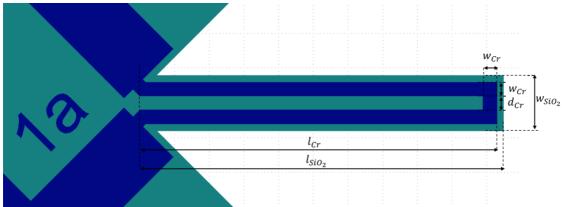

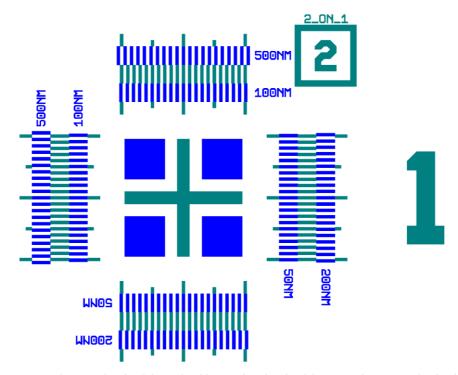

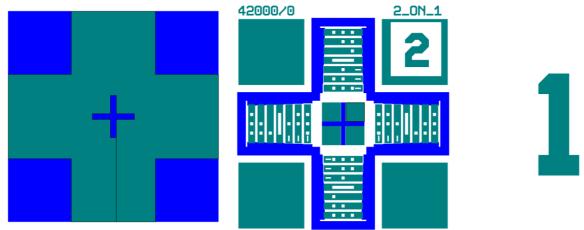

Figure 2 Design of the masks used to pattern a cantilever. Blue: Cr; green: SiO2

Figure 1 shows a 3D schematic of a cantilever. Figure 2 shows the schematic of the top view over a cantilever, which also corresponds to the masks used for the patterning of the Cr and SiO<sub>2</sub> layers.

# 0.2. Overview of the fabrication process

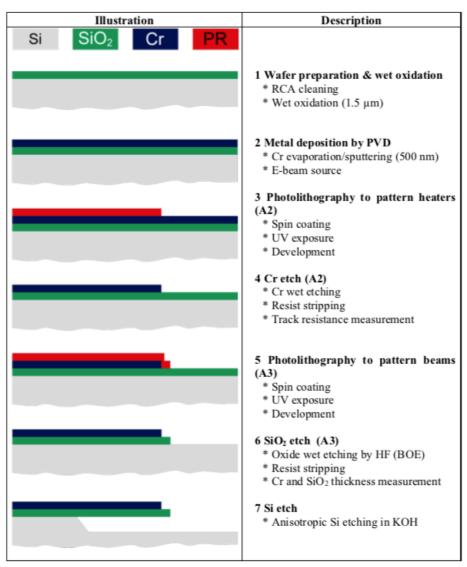

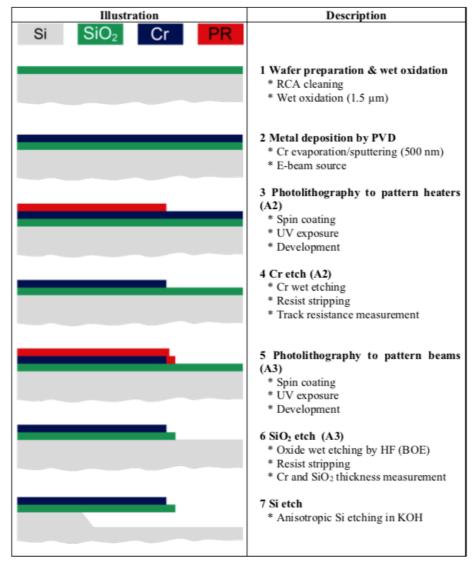

Producing this micro-actuator implies technological steps used for many micro-systems such as metallic thin film deposition under vacuum, photolithography and anisotropic etching of silicon. Table 1 and Figure 3 report the fabrication steps. The detailed steps are described in section §2.

Table 1 Fabrication steps

| 1 | "RCA" Cleaning and wet oxidation (T=1050°C, 1.5um SiO2)         | Done by CMi.     |  |

|---|-----------------------------------------------------------------|------------------|--|

| 2 | Evaporation Cr 500nm (EVA 600, e-beam source)                   | Done by CMi.     |  |

| 3 | Photolithography LAYER 1 METAL, definition of the heating track | A2               |  |

| 4 | Cr etching, resist strip                                        | A2               |  |

| 5 | Photolithography LAYER 2 OXYDE, definition of cantilevers       | A3               |  |

| 6 | Wet etching of SiO2, resist strip                               | A3               |  |

| 7 | Anisotropic etching of Si (KOH)                                 | Done by the TAs. |  |

Figure 3 Process flow: 1) Wafer preparation and growth of 1.5µm SiO2 layer (by CMi), 2) 500nm Cr deposition by evaporation (by CMi), 3) photolithography to pattern the Cr tracks, 4) Cr etch, 5) photolithography to pattern the SiO2 beams, 6) SiO2 etch, 7) release of the beams by KOH etching of Si.

### 0.3. Masks

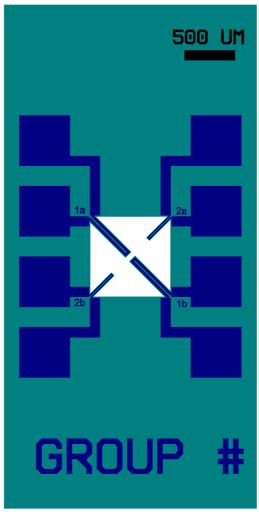

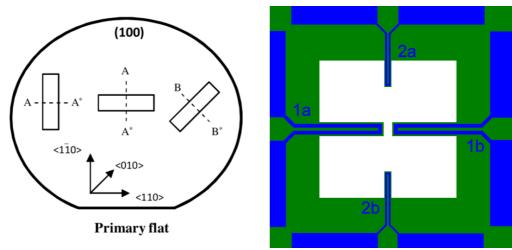

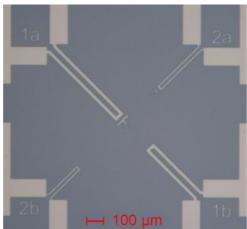

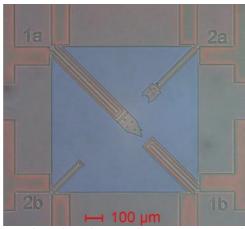

The fabrication of this micro-actuator requires the production of two masks: one for the chromium track (LAYER 1 METAL) and one for the silicon dioxide structure (LAYER 2 OXIDE). The mask for chromium will be used first, in step 3 (Table 1). Then the mask for SiO<sub>2</sub> structure will define the cantilevers in step 6 (Table 1). Alignment of the two masks is crucial during this process. It's important to use alignment crosses (the pattern on mask 1 fits the pattern on mask 2). Masks are composed of 96 cells, each containing 4 micro-actuators (two large ones, 1a and 1b, and two small ones, 2a and 2b, see Figure 3).

The first mask (LAYER 1 METAL), type bright field, is designed to be used with a positive photoresist to define chromium tracks. Each micro-actuator has one chromium track (meander-shaped) with 500µm x 500µm squares at each end as connection pads. This track is used to drive an electrical current that actuates the cantilever. The distance between the two tracks changes with the width of the cantilever as shown in Table 2. This mask also contains alignment crosses and its name.

The second mask (LAYER 2 OXIDE), type dark field, is designed to be used with a positive photoresist. It defines the micro-cantilevers structure in the silicon dioxide layer. Its alignment crosses fit the alignment crosses of the first mask. The Vernier scale around the alignment crosses enable to evaluate the quality of the alignment. For more information on the readout of the Vernier scale, you can refer to Wikipedia.

Figure 4 The device cell with 4 cantilevers. Green: SiO2. Blue: Cr. White: Si.

# **0.4.** Dimensions of the devices

The dimensions of the actuators are reported in Table 2 and the schematic of the actuator 1a is illustrated in Figure 5.

Table 2 Dimensions of the features of the actuators

|                  | $\mathrm{SiO}_2$        |                                          |                                  | Cr                        |                                                 |                                       |                               |

|------------------|-------------------------|------------------------------------------|----------------------------------|---------------------------|-------------------------------------------------|---------------------------------------|-------------------------------|

| Feature          | Length $l_{SiO_2}$ [µm] | Width<br><i>w<sub>SiO2</sub></i><br>[µm] | Thickness $t_{SiO_2}$ [ $\mu$ m] | Length $l_{Cr}$ $[\mu m]$ | Track<br>width<br><i>w<sub>Cr</sub></i><br>[µm] | Distance between tracks $d_{Cr}$ [µm] | Thickness $t_{Cr}$ [ $\mu$ m] |

| Actuators 1a, 1b | 500                     | 80                                       | 1.5                              | 490                       | 20                                              | 20                                    | 0.5                           |

| Actuators 2a, 2b | 300                     | 40                                       | 1.5                              | 293                       | 10                                              | 10                                    | 0.5                           |

Figure 5 Dimensions of the actuator 1a.

## 1. Theory and design

## 1.1. Theory

The preparation questions will be answered during the session planned the 8 March 2024. See the end of this section for the details of the **submission of your answers until Tuesday, 5 March 13h.**

#### **Questions:**

- 1. Calculate the electrical resistances of the Cr tracks (thickness 500nm) for the 2 standard cantilevers 1a and 2a.

- a. Let's say you apply a DC voltage V across the electrical track, how much power will be dissipated by Joule heating?

- b. How much power will be dissipated if you apply a sinusoidal AC voltage V?

- 2. From the literature, find the oxidation time to obtain 1 µm of oxide at 1050°C.

- a. Why are we using wet oxidation and not dry oxidation?

Refer to the CMi website (CMi Centrotherm Furnaces) and to the references to answer that question.

- 3. In which direction will the cantilever bend initially, at 20°C, just after the release by KOH etching? Provide a schematic and a qualitative answer about the internal stress in materials. The references will help you answer that question. Think about the growth/deposition process.

- 4. Explain how KOH etching of silicon works, why it's anisotropic.

- a. Explain why the cantilevers are in the corners of a square and explain why the orientation of the square with respect to the crystal planes of silicon is of importance; which crystal plane (Figure 6)?

- b. What would it change in terms of KOH etching if we were to put the cantilevers on the sides of the square (Figure 7)?(The references will help you answer that question. Remember that when discussing geometrical matters, a schematic is always a good idea.)

Figure 6 Orientation of the silicon crystal on the wafer used in this practical (reproduced from [11]).

Figure 7 Cantilevers on the sides of the square.

- 5. Estimate the resonance frequency of both standard micro-fabricated cantilevers 1a and 2a (see design in Figure 5). To do so, use the formulas below. An approach you can follow consists in transforming the 2-material structure into an equivalent 1-material structure as described in the section §9.1 *Composite Cross-Sections* of the reference [13]. You'll also need to evaluate the total area moment of inertia for the two materials. Report the total area moment of inertia I, the spring constant k, the mass of the structure m and the resonance frequency f. (Note that obtaining a fully expanded analytical formula relating the dimensions of the cantilevers to the resonance frequency is not expected as this will result in a quite heavy formula, but it might help you in the next session when you'll need to modify the geometry of the cantilevers to tune the resonance frequency.)

- a. Why won't this resonance frequency perfectly match the actual resonance frequency of the cantilever that you'll measure in session A4?

Help for question 5:

$$k_{cantilever} = \frac{3EI}{l^3}$$

$k_{cantilever}$  is the spring constant, E the Young modulus, I the area moment of inertia and l the length of the beam

$$\omega = \sqrt{\frac{k_{cantilever}}{\alpha \, m_{beam}}}$$

$\omega$  is the pulsation,  $m_{beam}$  the mass of the beam and  $\alpha = 0.24276$ , a factor that accounts for the fact that the weight is evenly distributed along the beam.

$E_{SiO2} = 70 \ GPa$  (http://www.memsnet.org/material/silicondioxidesio2film/)  $E_{Cr} = 140 \ GPa$  (https://www.memsnet.org/material/chromiumcrfilm/) <u>Remark</u>: The references are useful for understanding the practical work and answering questions.

- 1) Verify if you can **run/use Klayout (Windows, MacOS, Linux)** on your computer and **ACES (Windows only, only 1 student per group will need to run it)**. Let us know if you have any software issue or if everything runs well.

- 2) Answer the preparation questions 1 to 5 in a short PDF report (called "Topic2-373-Preparation\_Group#\_Name1\_Name2\_Name3.pdf". Replace # by the group number and Name1, Name2, Name3 by the names of the people in your group).

- → Perform tasks 1) and 2) and submit your PDF report to <a href="mailto:chenxiang.zhang@epfl.ch">chenxiang.zhang@epfl.ch</a> until Tuesday 5 March 13h. You'll get a feedback during the next session.

# 1.2. Advice for the reports

- Detail the calculations (with units and description of the variables) and add schematics when discussing geometrical matters for a better understanding.

- Avoid spelling/grammar mistakes (negative points can be added to the final mark).

- Discuss and criticize your results. Try to evaluate if the results you obtain make sense.

# 1.3. Design and simulation session

During this part, you'll use a software for computer-assisted design (the user manuals are on moodle), Klayout (<u>available here</u>, with basic <u>video tutorial</u>) to implement two modified designs of the cantilevers.

You'll leave the cantilevers 1a and 2a unchanged, whereas you'll modify 2b according to your group's specifications (§1.3.1) and you'll modify 1b freely so as to get a fancy cantilever with a custom design of your choice (§1.3.2). You'll then run KOH etching simulations to ensure that the devices will be released at the end of the fabrication process (§1.3.3).

See the end of this section for the list of files you'll have to submit until **Tuesday, 12 March, 13h.**

# **1.3.1.** Modification of 2b – group assignments

The first task is to modify the design of the cantilever 2b (small one) according to **the specifications of each group given in Table 3.** Use the formulas from the previous session to justify how you change the geometry and then implement the designs in the design file "Topic2-373-Standard4.gds" on moodle with Klayout

Also, don't forget to modify your group number in the design and rename the design file as "Topic2-373\_2024\_Group#\_Name1\_Name2\_Name3.gds" (replace # by your group number, Name1, Name2, Name3 by the names of the people in your group).

| Group | Specific assignment for cantilever 2b                                     |

|-------|---------------------------------------------------------------------------|

| 1     | Tune the resonance frequency to 1.13x the resonance frequency of 2a.      |

| 2     | Tune the resonance frequency to 0.97x the resonance frequency of 2a.      |

| 3     | Tune the resonance frequency to 1.18x the resonance frequency of 2a.      |

| 4     | Tune the resonance frequency to 0.93x the resonance frequency of 2a.      |

| 5     | Tune the resonance frequency to 1.27x the resonance frequency of 2a.      |

| 6     | Tune the resonance frequency to 0.88x the resonance frequency of 2a.      |

| 7     | Tune the resonance frequency to 1.31x the resonance frequency of 2a.      |

| 8     | Tune the resonance frequency to 0.82x the resonance frequency of 2a.      |

| 9     | Tune the resonance frequency to 0.68x the resonance frequency of 2a.      |

| 10    | Tune the resonance frequency to 0.78x the resonance frequency of 2a.      |

| 11    | Tune the resonance frequency to 0.73x the resonance frequency of 2a.      |

| 12    | Tune the resonance frequency to $0.63x$ the resonance frequency of $2a$ . |

Table 3 Group assignments

### Summary of the tasks in §1.3.1:

- → Save the "Topic2-373-Standard4.gds" file as

- "Topic2-373\_2024\_Group#\_Name1\_Name2\_Name3.gds" (replace # by your group number, Name1, Name2, Name3 by the names of the people in your group).

- → Modify the group number in the design in the

- "Topic2-373 2024 Group# Name1 Name2 Name3.gds" file.

- → Modify the cantilever 2b according to your group specification in the "Topic2-373\_2024\_Group#\_Name1\_Name2\_Name3.gds" file.

- → Explain your modifications in the report.

## **1.3.2.** Modification of 1b – free design

In order to study the effects of the geometry of the SiO2 layer during KOH etching of silicon, you will also modify the cantilever 1b to implement a non-conventional structure (fancy cantilever) of your choice (i.e., a cantilever with a Christmas tree shape or the logo of your favorite hornuss club). For that purpose, you can modify both the SiO2 and the Cr layers but you need at least to modify the SiO2 layer. Moreover, if you want to actuate your cantilever, don't forget to include closed Cr tracks. An example from a previous year in illustrated in Figure 8.

#### Advice:

- shallow SiO<sub>2</sub> structures are prone to breaking;

- structures with critical dimensions or critical alignment below 5μm might not come out as nice as you'd like them to due to overetching;

- long cantilevers with heavy weight at the tip might break due to stress or due to stiction to the bottom of the Si square (Figure 9).

Figure 8 Example of a fancy design, the FC Barcelona crest, realized during a past practical, right before the SiO<sub>2</sub> etching step. In that case the Cr tracks are open and the cantilever can't be actuated. Green: SiO<sub>2</sub> unprotected; orange: SiO<sub>2</sub> covered by PR; orange with shades: SiO<sub>2</sub> covered by Cr and PR

Figure 9 Example of a fancy design, a teddy bear/mouse that sticks to the bottom of the silicon square after the KOH etching. Also the Cr tracks delaminated due to poor Cr adhesion to SiO2.

#### Summary of the tasks in §1.3.2:

- → Modify the cantilever 1b to realize a fancy cantilever of your choice in the "Topic2-373\_2024\_Group#\_Name1\_Name2\_Name3.gds" file.

- → Report a picture of the design of the 4 cantilevers.

# **1.3.3.** KOH etching simulation

Modeling of KOH etching with the software ACES will enable to ensure that all the cantilevers will be released within the fixed KOH etching duration (130 minutes) at the end of the fabrication process.

Using ACES you'll upload your design and simulate the KOH etching following the steps below:

- a. If you've used Clewin, follow the steps in the file "Topic2-373-ACES\_manual-Anisotropic etching 250915.pdf" on moodle.

- b. If you've used Klayout, follow the steps below:

- i. Save a copy of your design file just to be safe.

- ii. Select the SiO2 layer. In the layer toolbox, select stipple and select the fully filled option.

- iii. Go to View, unselect Show Grid.

- iv. Select all the components in the SiO2 layer, go to Edit>Selection>Merge Shapes.

- v. Use the Rectangle tool in the Add mode to draw a rectangle anywhere in an empty layer.

- vi. Use the Select tool to double-click the rectangle and open its properties.

- vii. Change the height and width to 1000μm and change the position of the center to X=0μm and Y=0μm. Click Apply, click OK.

- viii. Select the shape containing the designs of the cantilevers in the SiO2 layer first, then while pressing Shift, select the rectangle you created.

- ix. Go to Edit>Selection>Intersection Others with First.

- x. You should now get a single shape containing the designs of the cantilevers within a frame of 1000µm x 1000µm in the SiO2 layer.

- xi. Hide all the layers, except the SiO2 layer.

- xii. Create a printscreen and crop the image right on the borders of the frame. Crop slightly tighter so that the pixels on the borders are colored. Colored pixels will be interpreted as SiO2 by ACES for the simulation, whereas white pixels will be interpreted as Si.

- xiii. Save the image as a .bmp file.

- xiv. Follow the steps in the file "Topic2-373-ACES\_manual-Anisotropic etching 250915.pdf" from the Simulation Wizard section.

You've now obtained your first ACES simulation results.

→ Report the evolution of the KOH etching process for the <u>initial</u> design you simulated at times 30, 60, 90, 130 minutes by using pictures of the results.

If everything went well, you should have etched all the Si underneath the cantilevers within 130 minutes. If not, then you'll have to update your design and run the simulation with the new design until all the Si below the cantilevers gets etched after 130 minutes.

→ Report the evolution of the KOH etching process for the <u>final</u> design you simulated at times 30, 60, 90, 130 minutes by using pictures of the results. Explain which modifications you had to implement with respect to the initial design and why they were efficient.

Using ACES again, verify your answer to the question 4 (§1.1) when the cantilevers are at the center of the sides of the square.

→ Report the picture of the design used and the simulation results after 130 minutes by using the picture of the result. Explain the differences between the configuration where the cantilevers are at the corners and the configuration where the cantilevers are on the sides.

### Summary of the tasks in §1.3.3

- → Run the ACES simulation on the picture of your initial design in the "Topic2-373 2024 Group# Name1 Name2 Name3.gds" file.

- Report a picture of the **initial** design and the pictures showing the results of the ACES simulation after 30, 60, 90, 130 minutes of KOH etching in the PDF report "Topic2-373 2024\_Preparation\_Group#\_Name1\_Name2 Name3.pdf".

- → If not all the Si below the cantilevers was etched within 130 minutes, according to the ACES simulation, then modify the designs in "Topic2-373 2024 Group# Name1 Name2 Name3.gds" and repeat the simulations in ACES until all the Si below the cantilevers got etched by the KOH within 130 minutes.

- Report a picture of the **final** design for which the simulation resulted in all the Si etched within 130 minutes and the pictures showing the results after 30, 60, 90, 130 minutes of KOH etching in the report

- "Topic2-373 2024\_Preparation\_Group#\_Name1\_Name2 Name3.pdf".

- → Comment the designs modifications you implemented between the initial simulation (when Si remained within 130 minutes) and the final simulation (when all the Si was etched within 130 minutes) and comment the evolution of the simulated KOH etching between these 2 designs in the report "Topic2-373 2024\_Preparation\_Group#\_Name1\_Name2 Name3.pdf".

- Report a picture of the design with the cantilevers on the sides and the pictures showing minutes the results after 130 of **KOH** etching in report "Topic2-373 2024\_Preparation\_Group#\_Name1\_Name2 Name3.pdf". Explain the results

You have until Tuesday 12 March, 13h to send the following files to chenxiang.zhang@epfl.ch:

- 1) the final .gds design file (modified with Klayout) called

- "Topic2-373 2024 Group# Name1 Name2 Name3.gds" replace # by the group number and Name1, Name2, Name3 by the names of the people in your group) containing your designs (unmodified cantilevers 1a and 2a, modified cantilever 2b according to your group's assignments, modified fancy cantilever 1b, your updated group number written below);

- 2) the updated "Topic2-373\_2024\_Preparation\_Group#\_Name1\_Name2 Name3.pdf" report file containing the screenshots of the ACES simulation, together with your answers/explanations to the questions asked in the 2<sup>nd</sup> session.

- 3) (Optional) A good idea would be to implement the corrections suggested during the feedback to your initial report in order not to forget about them when you write the final report at the end of the session A4, but you can also implement these corrections later.

### 2. Cleanroom fabrication at CMi

Each group will perform a part of the fabrication of the cantilevers on a silicon wafer. Each session takes about 3 to 4h in the clean room at the CMi+1 level. Cleaning, oxydation and metal deposition on the wafers will already be done. The fabrication will be about performing a photolithography step followed by the Cr etching step and resist stripping, a second photolithography step with alignment on the structures patterned previously, followed by the SiO2 etching step and resist stripping.

#### **WARNING!**

It's important to be aware that all the processes using chemicals are potentially dangerous. Wearing protection glasses and a 2<sup>nd</sup> layer of gloves is mandatory for photoresist handling, spin coating, development. For the etching steps in the chemical hood, a face shield, long chemical gloves and apron are obligatory!

After each step involving a chemical, clean the wet bench.

Please read the Safety instructions and Wet Bench Safety.

If you don't feel comfortable, let us know about it.

### 2.1. General instructions

Due to the gowning procedure to enter the clean room and to the fact that your teaching assistant will be responsible for you, everybody will appreciate if you're on time. If you can't be on time or need to leave before the end of the session, please let your teaching assistant know in advance. Also, we usually do the entire session without any break, so prepare yourselves accordingly. There are some lockers at the entrance of the clean room for you to store your belongings, however be aware that they're not always available. Things usually go smoothly for everybody during these practical, but if you have any question or feel anxious about going to the clean room, feel free to contact Chenxiang Zhang (chenxiang.zhang@epfl.ch) or Pol Torres-Vila (pol.torresvila@epfl.ch).

# 2.2. Detailed fabrication steps

Before the practical session, go through the fabrication steps described below and through the runcard available on moodle to get an understanding of the process you're going to complete in the clean room. There are some questions that you'll have to answer during the practical session that you'll find in the description below. As an overview, the process flow is illustrated in Figure 10.

- The steps in Runcard §1 (2.2.1) and Runcard §2 (2.2.2) will be performed by the CMi staff.

- Steps in Runcard §3 (2.2.3), Runcard §4 (2.2.4) and Runcard §4 (2.2.5) will be performed first.

- Steps in Runcard §5 (0), Runcard §6 (2.2.7) and Runcard §7 (2.2.8) will be performed next.

- The steps in Runcard §7 (2.2.9) will be performed by the teaching assistants.

Figure 10 Process flow: 1) Wafer preparation and growth of 1.5µm SiO2 layer (by CMi), 2) 500nm Cr deposition by evaporation (by CMi), 3) photolithography to pattern the Cr tracks, 4) Cr etch, 5) photolithography to pattern the SiO2 beams, 6) SiO2 etch, 7) release of the beams by KOH etching of Si.

# 2.2.1. « RCA » cleaning, wet oxidation and chromium evaporation [Runcard §1]

The surface of silicon is highly reactive. It presents a high chemical affinity. It is difficult to obtain and keep a clean surface. Cleaning is decisive to obtain devices with stable and reproducible characteristics. RCA cleaning step is described in details on the CMi website: RCA Cleaning (Figure 10 1)). This step is followed by the formation of a 1.5µm silicon dioxide (SiO2) layer in wet conditions, out of which the micro-cantilevers will be patterned. The CMi staff will perform these steps for us.

# 2.2.2. Metallization by chromium evaporation [Runcard §2]

The deposition of thin layers (0.2-0.5 um) of metal on a wafer is often done by evaporation under vacuum. The simplest method consists in heating a tungsten cup containing pieces of the metal to be evaporated by Joule effect. The heat causes the metal to melt and then evaporate. It

later condensates on the substrate, i.e. the wafer. In this practical work, a chromium (Cr) layer of 500nm will be deposited by evaporation with the equipment Alcatel EVA 600 (Figure 10 2)). The adhesion of the two layers ( $SiO_2$  and Cr) is not only critical during the fabrication process, but also for the thermal actuation of the beam.

# 2.2.3. Photolithography for the Cr tracks (mask LAYER 1 METAL) [Runcard §3]

The photolithography process (<u>Process</u>) to pattern the Cr tracks (Figure 10 3)) is divided in 3 steps at CMi+1 (<u>CMi Access</u>).

# 2.2.3.1. Wafer dehydration, photoresist coating and soft bake [Runcard §3.1-3.3]

A manual coater (SSE coater line - Zone 13) is used for the thermal dehydration of the wafer (AZ1512 Process) without HMDS (HMDS explained) and the spin coating of the positive photoresist AZ1512 on the Cr layer. The PR gets then softbaked to evaporate the solvent and form a solid layer.

Q1. We have a wafer with SiO2 and Cr, why aren't we using the vapor HMDS surface treatment?

Q2.We aim to obtain a 1.5 $\mu$ m thick AZ1512 layer, what parameters need to be used for the spin coating? Look for the answer on the CMi website.

# **2.2.3.2. Exposure [Runcard §3.4]**

The photoresist is then exposed using a manual mask aligner, Suss MJB4 in Zone 13. This machine allows the alignment of the mask with the substrate and the exposure of the photoresist. In this practical work, alignment is done on one face only (simple face). **The position of wafer meplat is important for the future step of anisotropic etching of the <100> planes.** The wafer meplat has to be oriented parallel with the side on the mask (and hence, with the side of the square containing the beams). As this is the first exposure, no fine alignment has to be performed, but the MASK 1 will produce alignment crosses useful to align the second photolithography MASK 2 later.

Q3. Determine the duration of exposure from the data sheet of the photoresist given by the supplier and from the light power at the level of the substrate (information available next to the machine, approximately  $20 \text{mW/cm}^2$ ). The photoresist is AZ1512 and is  $1.5 \mu \text{m}$  thick. Q4. Do you expose the parts where you want Cr to remain after the etching step or the parts where you want to etch the Cr?

Q5. How do you place the mask: the Cr side or the glass side towards the PR? Why? How do you recognize which side goes towards the wafer?

## 2.2.3.3. Development and check [Runcard §3.5-3.6]

The development is done manually on the base wet bench in Zone 13. During this step, the exposed photoresist get dissolved by the developer solution (CD26 or AZ726 MIF) because it is a positive photoresist. At the end of this step, the wafer should present similar patterns to the ones in Figure 11.

Q6. How long should you put the wafer in the developer? Why is this an important parameter?

Q7. Why do we pattern the photoresist to cover the Cr at the places where we want the electrical tracks to be?

Q8. Take a few pictures (including one at high magnification to measure the width of PR/Cr track). Does the width of the PR features match the one of the Cr features in your design file?

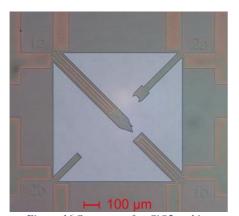

Figure 11 Structure after photolithography with mask Layer 1 Metal: gray = Cr, brown = photoresist on Cr.

# 2.2.4. Etching of the Cr [Runcard §4]

This step will now take place in the Z14 under the Acid bench. We'll etch the Cr to define the electrical tracks (Figure 10 4)). Be extra-cautious when manipulating any object in this zone, especially if the object has been under the hood.

# **2.2.4.1.** Cr etching [Runcard §4.1-4.2]

Chromium etching is performed at room temperature (<u>Arias ACID Z14</u>). The wafer is immersed in a solution called "Chrome-Etch" made out of (NH<sub>4</sub>)<sub>2</sub>Ce(NO<sub>3</sub>)<sub>6</sub> and HClO<sub>4</sub>.

Q9. Given that we have a 500nm thick Cr layer and Cr features separated by at least  $5\mu$ m and at least  $5\mu$ m wide, how long should you put the wafer in the Chrome-etch solution? Why is this an important parameter? What happens if you leave it for too long? Use a schematic showing how the etching progresses to justify your answer.

#### **ATTENTION!**

No contact with eyes or skin. Clothes bleaching.

Face shield, long chemical gloves and apron are mandatory!

After each step involving a chemical, clean your gloves and clean the wet bench.

The procedure is as follows:

- a) Fill the plastic reservoir for single wafer with Chrome-Etch (check etching time in the runcard). Or use the readily-available Chrome-Etch bath in the acid hood.

- b) Hold the wafer in an "arrow"-carrier.

- c) Dip the wafer in the Chrome-Etch solution and observe carefully the etching to prevent over-etching.

- d) Take out the wafer and rinse under DI water twice for 3 minutes, prior to washing one last time with the DI water gun.

- e) Dry it out with the N2 gun.

- Q10. How long did you leave the wafer in the Chrome-etch solution? Why is this an important parameter? What happens is you leave it for too long? (Hint: look at the link Arias ACID Z14). Use a schematic showing how the etching progresses to justify your answer.

- Q11. How did you detect the end of the etching procedure? Describe what you observed.

# 2.2.4.2. Resist stripping [Runcard §4.3]

The photoresist is removed/stripped in Zone 13 on the base wet bench, using Technistrip solution (or acetone) in a beaker. After 10 min, the wafer is rinsed in DI water and dried out.

# 2.2.5. Electrical/optical characterization of the metallic layer [Runcard §4.4-4.5]

You will first acquire pictures of your wafer on a microscope in Zone 15. This will enable you to check the width of your Cr tracks and determine the impact of the overetching. The devices should now look like Figure 12.

- Q12. Acquire pictures of your overall design and of zones of interest (defects,...).

- Q13. Acquire high magnification pictures of the same track as you observed in

- 2.2.3.3 to compare the width of the Cr track and the width of the PR. Does the width of these features match the width of the features in the design file? Why?

Then, using the Süss PM8 equipment in CMi+1 Zone 11, you'll characterize the resistance of the Cr tracks that you've just patterned. You'll perform and compare the results of the 2 points and 4 points measurements.

- Q14. What's the advantage of the 4 points measurement? Why? Explain the principles.

- Q15. Compare the resistance you measured to the resistance you computed in the preparation, do they match? Explain the differences. (Hint: have a look at the parameters for thin Cr films deposited by evaporation on the EVA 760: <u>Parameters EVA 760</u>. These parameters aren't reported for the EVA 600 used for this practical, but you can assume they're the same.)

Figure 12 Structure after resist strip (Cr on SiO2); white=Cr on SiO2, gray = SiO2.,

# 2.2.6. Photolithography for the SiO<sub>2</sub> beams (mask LAYER 2 OXIDE) [Runcard §5]

In this session, we're going to pattern a photoresist layer on the unpatterned SiO2 and patterned Cr layers, to define the places where we want the SiO2 beams. A similar process to the one used for the first photolithography step (§2.2.3) is used to pattern the photoresist for the SiO<sub>2</sub> layer patterning, with a few adjustments [Runcard §5.1-5.6].

# 2.2.6.1. Wafer dehydration, photoresist coating and soft bake [Runcard §5.1-5.3]

To improve the adhesion of photoresist [Runcard §5.1], the wafer is thermally dehydrated using the hotplate of the equipment "manual SSE coater line" (AZ1512 Process) and treated with Hexamethyldisilazane (HMDS) in Zone 13 (HMDS explained).

This coater line is also used to spin coat the positive photoresist AZ1512 on the SiO2/Cr layer. The PR gets then softbaked to evaporate the solvent and form a solid layer.

- Q16. We have a wafer with SiO2 and Cr, why are we now using the vapor HMDS surface treatment?

- Q17. We aim to obtain a 1.5 $\mu$ m thick AZ1512 layer, what parameters need to be used for the spin coating?

## 2.2.6.2. Exposure with alignment [Runcard §5.4]

The photoresist is then exposed using a manual mask aligner Suss MJB4 in Zone 13. This machine allows the alignment of the mask with the substrate and the exposure of the photoresist. In this practical work, alignment is done on one face only (simple face). As this is the second photolithography step, a fine alignment has to be performed with the structures patterned by the MASK 1 which contain alignment crosses to align the MASK 2 layer with.

For this exposure step [Runcard  $\S5.4$ ], the mask LAYER 2 OXIDE will need to be aligned to the Cr patterns on the wafer to make sure the Cr tracks will be on the SiO<sub>2</sub> beams. You'll first find the alignment marks on the MASK 2 (Figure 13 and Figure 14 - green) and then find the corresponding alignment crosses on the wafer (Figure 13 and Figure 14 - blue). Then you'll align these marks together using the controls on the mask aligner. The goal is to align them as in (Figure 13 and Figure 14). The Vernier scale (Figure 13) will enable to evaluate the quality of the alignment.

Figure 13 Alignment marks on each side of the wafer (blue) and each side of the MASK 2 (green). The thin bars represent the Vernier scale to evaluate the quality of the alignment.

Figure 14 Examples of other alignment marks available on the wafer (blue) and on the MASK 2 (green). Use the ones you prefer.

- Q18. Determine the duration of exposure from the data sheet of the photoresist given by the supplier and from the light power at the level of the substrate (information available next to the machine, approximately  $20 \text{mW/cm}^2$ ). The photoresist is AZ1512 and is  $1.5 \mu \text{m}$  thick.

- Q19. Do you expose the parts where you want  $SiO_2$  to remain after the etching step or the parts where you want to etch the  $SiO_2$ ?

- Q20. How do you place the mask: the Cr side or the glass side towards the PR? Why? How do you recognize which side goes towards the wafer?

# 2.2.6.3. Development and check [Runcard §5.5-5.6]

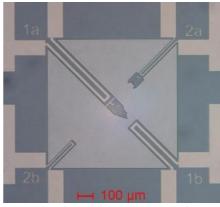

The development is done manually on the base wet bench in Zone 13. During this step, the exposed photoresist gets dissolved by the developer solution (CD26 or AZ726 MIF) because it is a positive photoresist. At the end of this step, the wafer should present similar patterns to the ones in Figure 15.

- Q21. How long should you put the wafer in the developer? Why is this an important parameter?

- Q22. Why do we pattern the photoresist to cover the SiO2 at the places where we want the beams to be?

- Q23. Take a few pictures (including one at high magnification to measure the width of PR/SiO2 beam). Does the size of the PR features match the size of the features in the design file?

Figure 15 Structure after photolithography with mask LAYER 2 OXIDE (orange with green shades = photoresist on Cr, green = photoresist on  $SiO_2$ ,  $gray=SiO_2$ ).

# 2.2.7. Etching of the SiO<sub>2</sub> beams [Runcard §6]

This part is about etching the SiO2 to pattern the beams.

# **2.2.7.1. SiO<sub>2</sub> etching [Runcard §6.1-6.2]**

SiO<sub>2</sub> will be etched by Hydrofluoric acid (HF) on acid wet bench in Zone 14. To etch large thicknesses of silicon oxide (>100nm), it's important to stabilize the HF solution making a buffer (BHF or BOE). It helps to prevent the degradation of the photoresist patterns and get a constant etching rate.

#### **ATTENTION!**

No contact with eyes or skins!

Hydrofluoric (HF) acid attacks directly bones without feeling any burn or tingling. Even diluted, Hydrofluoric acid is extremely dangerous.

The composition of the BHF solution at pH 1.7 is:

• HF (50%): 20mL

• NH<sub>4</sub>F (97%): 72.16g

• H<sub>2</sub>O-DI: 110mL.

The procedure is as follows:

- a) Fill the Teflon reservoir for single wafer with BHF (check etching time in the runcard).

- b) Hold the wafer in an "arrow"-carrier.

- c) Dip the wafer in the BHF solution and observe carefully the etching to prevent overetching.

- d) Take out the wafer and rinse under DI water twice for 3 minutes, prior to washing one last time with the DI water gun.

- e) Dry it out with the N2 gun.

- Q24. Given that you have a 1.5 $\mu$ m thick SiO2 layer with features spaced by minimum 5 $\mu$ m and with critical dimensions of minimum 5 $\mu$ m, how long should you put the wafer in the BHF/BOE solution? Why is this an important parameter? What happens is you leave it for too long? (Hint: look at the link <u>Arias ACID Z14</u>). Use a schematic showing how the etching progresses to justify your answer.

- Q25. How long have you left the wafer in the BOE solution?

- Q26. How did you detect the end of the etching step? Describe what you observed and explain it.

Figure 16 Structure after SiO2 etching

Figure~17~After~resist~strip~(Cr+SiO2~on~Si)

Note that  $SiO_2$  could also be etched with dry etching methods. This process consists of the formation of a plasma with highly reactive chemical species, which react on the surface of the sample to generate volatile products. (See <u>SPTS APS</u>).

# **2.2.7.2. PR stripping [Runcard §6.3]**

The photoresist is removed/stripped in Zone 13 on the base wet bench, using Technistrip solution (or acetone) in a beaker. After 10 min, the wafer is rinsed in DI water and dried out.

# 2.2.8. Optical and mechanical characterization [Runcard §6.4-6.5]

You'll now acquire pictures of your designs on the microscope in Zone 15. You can check the alignment of your SiO<sub>2</sub> and Cr layers by looking at the beams as well as by looking at the

alignment marks and by looking at the Vernier scales. You can also measure the width of your features to quantify the underetch.

- Q27. Acquire pictures of your overall design and of zones of interest (defects,...).

- Q28. Acquire high magnification pictures of the same beam as you observed in 2.2.6.3 to compare the width of the SiO2 beam and the width of the PR. Does the size of

- the SiO2 features match the size of the features in the design file? If there's a difference, explain why.

- Q29. Using the Vernier scale, evaluate the quality of the alignment.

Finally, you'll measure the thickness of the layers with the mechanical profilometer alpha-step in Zone 15. This will enable you to obtain more accurate thicknesses to compare the computed beam dynamics to the results obtained during the characterization session.

Q30. Acquire profile curves and extract the Cr and SiO2 thickness.

This is the end of the session A3.

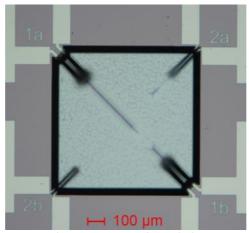

# 2.2.9. KOH anisotropic etching of Silicon (performed by the assistants) [Runcard §7]

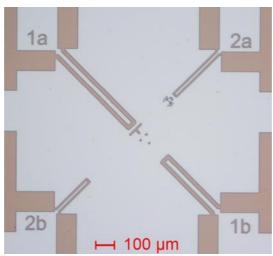

The last step consists of the release of the cantilevers. This is achieved by the teaching assistants by etching the silicon (Si) layer below the  $SiO_2$  beams with a KOH solution that presents anisotropic etch rates of Si, depending on the crystalline plans of the Si wafer. In this practical, the silicon wafer's surface coincides with a <100> crystal plan and the direction of its main flat is contained in a <110> plan. To release the  $SiO_2$  cantilevers, silicon has to be etched in 23%-KOH solution in Zone 14 on base wet bench. More information is available in the references. Figure 18 illustrates the state of the structures after the KOH release with the beams going out of the imaging plane due to the stress in the layers that induces bending.

$\textit{Figure 18 Structure after anisotropic etching of silicon (Cr + SiO2 \ on \ Si)}$

Note that Si could also be etched isotropically with dry etching methods such as with the <u>Alcatel AMS200</u> in Zone 2. In that case, the walls of the cell won't follow the (111) plans.

## 2.3. How to report the fabrication steps

The report will have to be submitted a week after your last session (see infos in §4).

In this report, you'll include a part about the fabrication process. We don't expect you to describe in details the steps that you haven't performed yourselves. For these steps, briefly mention what was done. You can use the illustrated process flow for that.

However we want you to explain the steps that you completed. Indicate the important parameters that you've used, the things to pay attention to during the different steps and your observations. Also answer the questions belonging to each session highlighted by the Q# items along the detailed fabrication steps (indicate in your report which question you're answering by reporting the related Q# item). You can illustrate the process using pictures. The best times to acquire pictures are after the development and after the stripping of the PR but you can of course add more. Don't forget to add scale bars and to explain what you see. Don't put pictures that you don't use or don't comment. Also, indicate what you see in these pictures (in the legend or even better, with arrows and text added in overlay).

### 3. Characterization of the devices at LMIS1

This session is dedicated to the study of the designed and fabricated cantilevers. Experimental results will be obtained and compared to the theory.

The observation of the dynamic behavior will give a practical example of the numerical simulations done in the COMSOL simulation session.

## **3.1. Setup**

The characterization is carried out in the lab of LMIS1 with the teaching assistants. The required equipment for the measurements are:

- Function generator

- Microscope

- Stroboscope

- 2 probes

- Multimeter

- Cables

### **3.2.** Tasks

- 1. Observation: try to explain the defects observed and measured on the structures. Use pictures.

- 2. Discuss the characterization set-up with your assistant. Which difficulties do you have? How did you solve them?

- 3. Measure the resistivity of the chromium tracks. Explain the differences between the measured values in clean room, the measured values in the lab and the theoretical values.

- 4. Measure the resonance frequencies of the different beams. Which behavior, dependent on frequency, can you observe? What is expected? Explain briefly.

- 5. Increase the voltage: what can you observe? Explain what happens and why.

- 6. Suggest modifications to improve your results.

## 4. Final report

Here are some guidelines for you to write the final report.

- Structure your report well and put a table of contents, an introduction and a conclusion.

- Put your names and group number on the front page.

- Include the preparation work (report from the end of session Theoretical and Design sessions with the ACES simulation), including the corrections received during the feedback at the beginning of the Design session.

- Include a part about the fabrication in clean room. Focus on the steps that you've completed and just briefly mention what was performed by cleanroom staff and TAs. See details in §2.3.

- Report your work during the characterization session. Report the setup you used for the characterization and the results from the tasks in §3.2.

- Compare the experimental results you obtained for characterization to the results from your calculations in the preparation. Also compare the resonance frequencies computed with COMSOL to the measured and calculated values.

- Discuss and criticize your results. Compare your experimental results to your theoretical predictions. Justify your results and be quantitative.

- After reporting measurements, summarize them, criticize them and conclude.

- Detail the computations (with units and description of the variables) and add schemes when discussing geometrical matters for a better understanding.

- Avoid spelling/grammar mistakes (negative points can be added to the final mark).

- When including Figures, don't forget to describe them and to indicate what people reading your report are looking at. Put scale bars.

- In appendix, add the scans of your notes during the practical sessions.

- Report the references that you used.

- If possible, when comparing curves, try to put the different curves on a single graph instead of using one graph per curve.

Upload the final report and all the relevant files on moodle.epfl.ch **1-week after** your last TP session.

### 5. References

- [1] N. Schwarzer, On the determination of film stress from substrate bending: Stoney's formula and its limits (reference available on moodle).

- [2] Thomas Gmur 2nd Bachelor Introduction à la mécanique des solides et des structures

- [3] Sandra Schweizer, Thermally actuated micro-mirror for one and two-dimensional optical beam scanning, Thèse EPFL, no 2359 (2001), Dir. Philippe Renaud, thesis link.

- [4] Dutoit, Laboratoire de Micro-électronique, Notices destinées aux étudiants de la section de Microtechnique. EPFL, 10/1993.

- [5] Site web du Centre de Microtechnologie de l'EPFL (CMI). http://cmi.epfl.ch/

- [6] M.J. Madou, Fundamentals of microfabrication. 1997, Boca Raton, U.S.: CRC Press LLC.

- [7] M.A.M Gijs, Technologie des Microstructures I+II, cours 3eme année Microtechnique, EPFL.

- [8] Unknown Author, The Silicon Cube, provided in the class Technologie des Microstructures I+II, cours 3eme année Microtechnique, EPFL.

- [9] MicroChemicals GmbH, Crystallography of Silicon, <a href="https://www.microchemicals.com/technical\_information/silicon\_crystallography.pdf">https://www.microchemicals.com/technical\_information/silicon\_crystallography.pdf</a>

- [10] M. Ilegems, Technologies Microelectroniques, 1998, Lausanne: Repro EPFL

- [11] Brockmeier et al., Surface tension and its role for vertical wet etching of silicon, J. Micromech. Microeng., 22,125012, 2012.

- [12] Hopcroft *et al.*, *What is the Young's Modulus of Silicon*, Journal of Microelectromechanical systems, Vol 19, No 2, 2010.

- [13] J. Lubliner and P. Papadopoulos, Introduction to Solid Mechanics. Cham: Springer International Publishing, 2017.

- [14] Deal et al., General relationship for the thermal oxidation of silicon, Journal of applied Physics, Vol 36, No 12, 1965.