# Exercice E10.2: VLSI et dissipation d'énergie

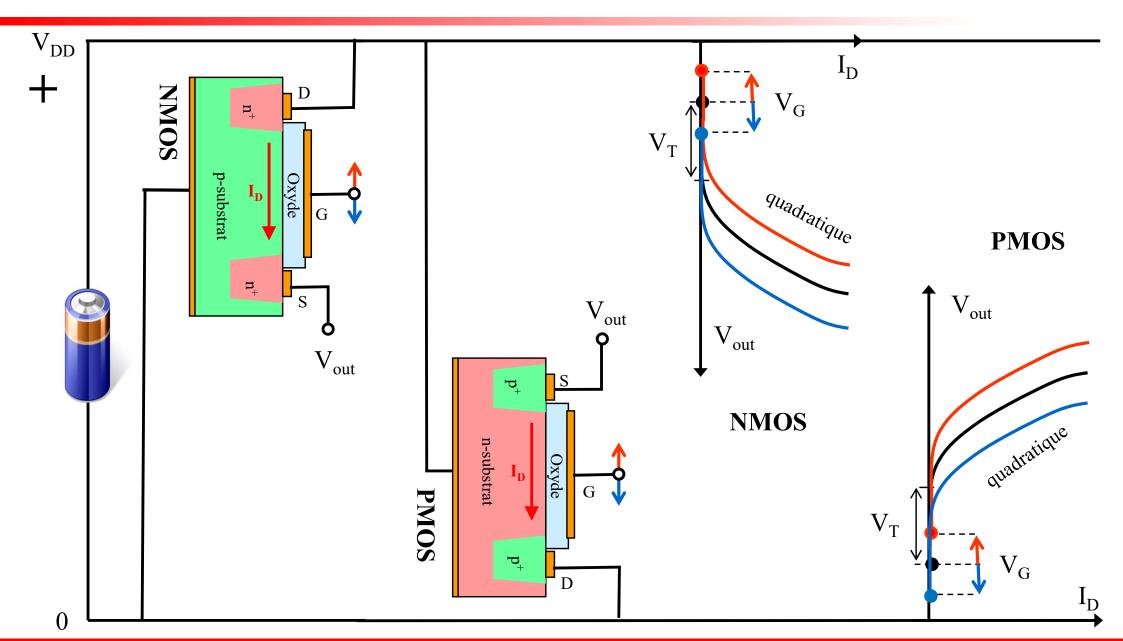

Considérons un chip avec une "Very Large Scale Integration" (VLSI) travaillant à température ambiante. Il contient  $10^9$  NMOS, tous "fermés" donc avec une tension de gate  $V_G=0$ . Le courant "subthreshold" est exprimé par:

$$I_{D,sub} \cong I_{0,sub} \cdot e^{q(V_G - V_T)/nkT}$$

avec  $n = 1.33$

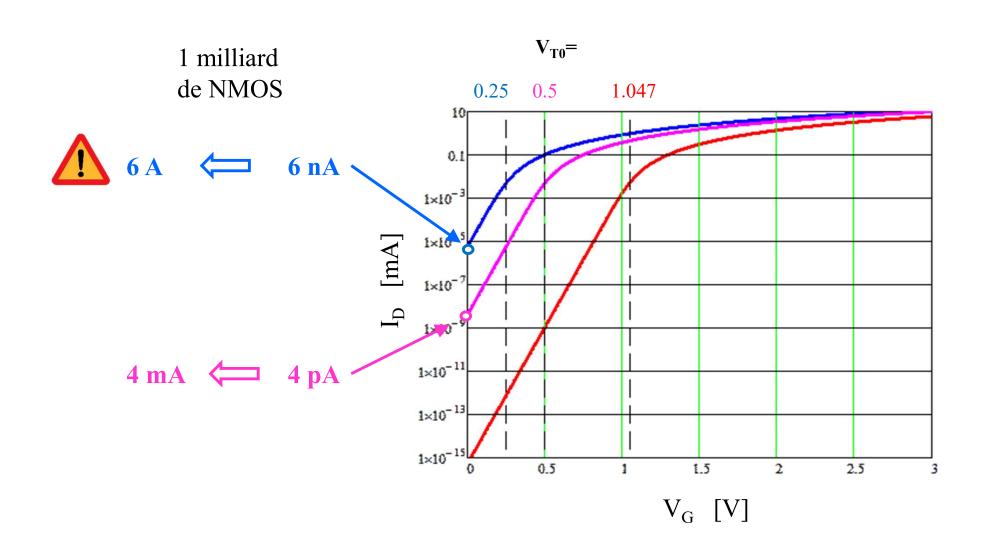

- A) Le courant à  $V_G=0$  V pour une tension de threshold  $V_T=0.5$  V est de 4 pA par transistor. Quelle est la consommation en courant de tout le chip lorsque les transistors sont tous fermés ?

- B) Nous diminuons la tension de threshold à  $V_T$ =0.25V. Quelle est maintenant la consommation en courant de tout le chip lorsque les transistors sont tous fermés ?

Commentaire: Cet exercice vise à montrer que le courant "subthreshold" pose une limite inférieure pour la tension de voltage, ceci afin d'assurer une bonne "fermeture" des transistors. Dans un micro-processeur, il y a en effet beaucoup plus de transistors au repos que de transistors "ouverts".

#### Ex. 10.2: solutions

$$I_{0.5V} \cong 10^9 \cdot 4 \cdot 10^{-12} = 4 [mA]$$

B) Courant dans chaque NMOS avec une tension V<sub>T</sub> réduite à 0.25V:

$$I_{D,sub} \cong I_{0,sub} \cdot e^{q(V_G - V_T)/nkT}$$

avec  $n = 1.33$

$$4 \cdot 10^{-12} [A] \cong I_0 \cdot e^{q(-0.5)/nkT} \implies I_0 = 8.2 [\mu A]$$

$$I_{D,sub} \cong I_0 \cdot e^{q(-0.25)/nkT} \cong 5.7 [nA]$$

$$I_{0.25V} \cong 10^9 \cdot 5.7 \cdot 10^{-9} = 5.7 [A]$$

#### Courant sur 1 transistor

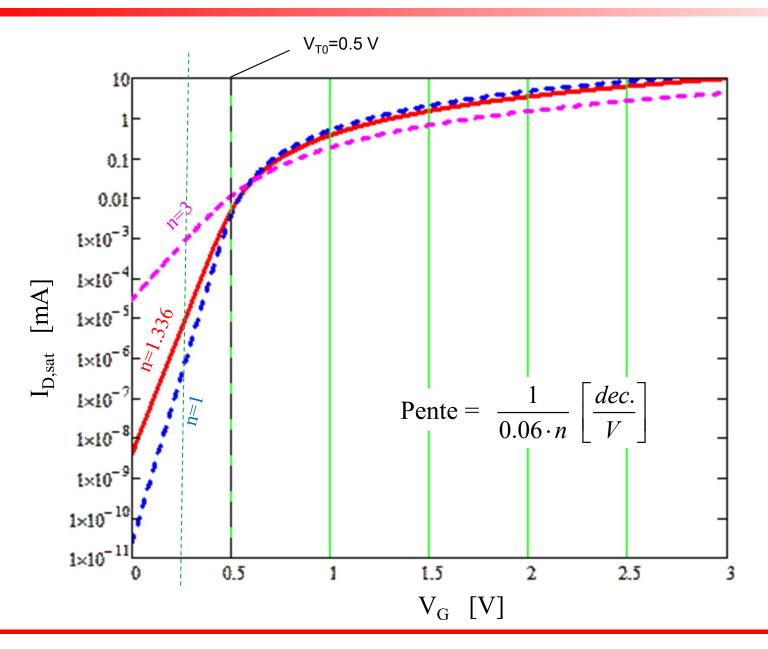

## Calcul numérique: Influence du slope factor n

$$n \equiv 1 + \frac{C_{B,th}}{C_{ox}}$$

$$C_{ox} = \frac{\mathcal{E}_0 \mathcal{E}_{ox}}{d_{ox}}$$

$$\begin{split} C_{B,th} &\equiv \frac{\mathcal{E}_0 \mathcal{E}_s}{W_{th}} \\ &= \frac{1}{2} \frac{\sqrt{2 \mathcal{E}_0 \mathcal{E}_s q N_A}}{\sqrt{2 \psi_B}} \end{split}$$

## Exercice E10.3: question de réflexion

Quelles sont les contraintes sur l'oxyde d'une structure MOS ?

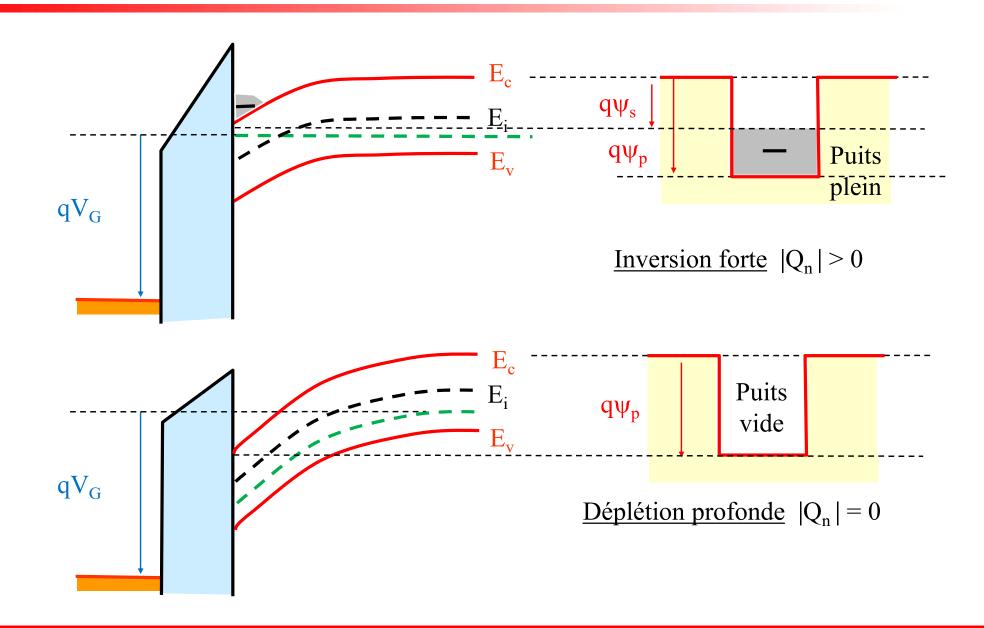

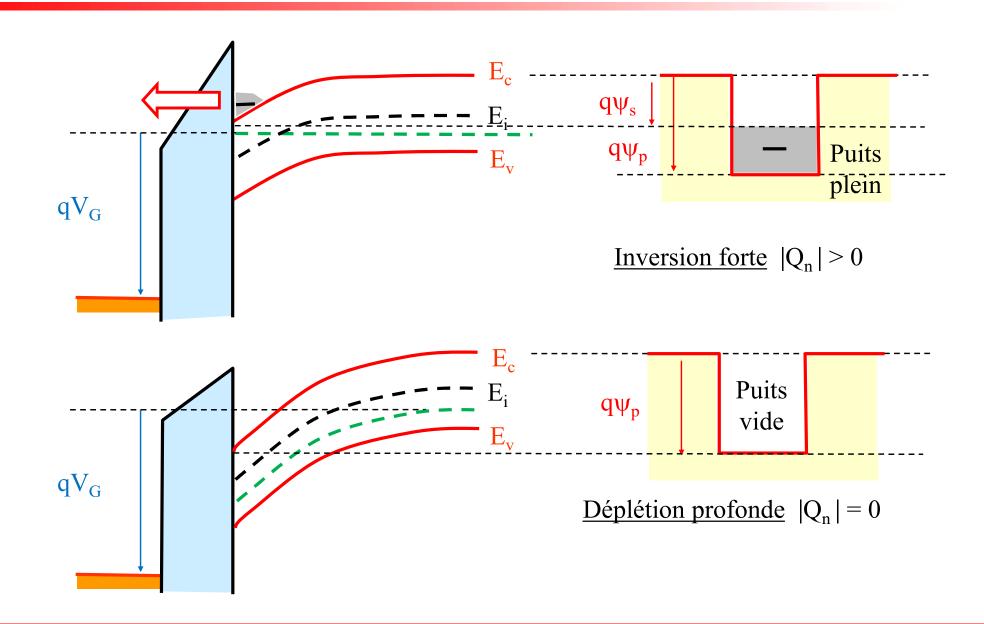

Discutez le cas d'une structure MOS sur substrat p en inversion forte (transistor) et celui de la même structure en déplétion profonde (CCD).

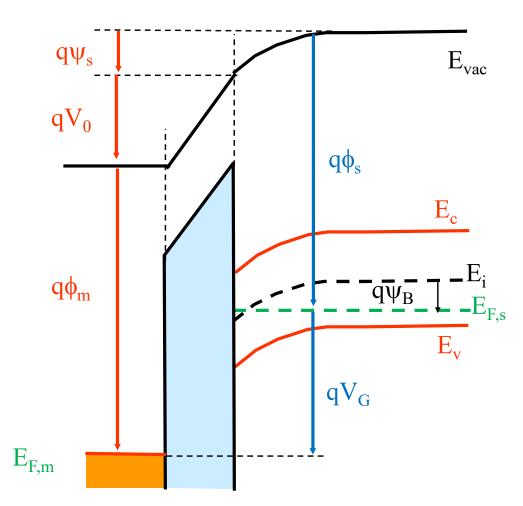

Avec la tension de gate, nous voulons modifier la structure de bande dans le semi-conducteur ou à sa surface. Pour être efficace il faut donc minimiser la chute de tension sur l'oxyde.

- → L'oxyde de gate doit être le plus fin possible.

- → Un oxyde avec une grande constante diélectrique est préférable.

Il existe une limite:

sous fort champ électrique, l'oxyde peut « claquer » et détruire le composant !

## Rappel: Potentiels et tensions

Potentiel sur le métal V<sub>G</sub>:

$$V_G + \phi_s = \psi_s + V_0 + \phi_m$$

$$V_G - V_{fb} = \psi_s + V_0$$

:

$$V_G - V_{M0} \cong n \cdot (\psi_s - 2\psi_B) - \frac{Q_n}{C_{ox}}$$

### Exercice 10.3: CCD

### Exercice 10.3: CCD

#### Q: où le risque de claquage de l'oxyde est-t-il le plus important ?

### Du côté de la source! Car le champ électrique y est maximal!

#### Exercices E10.4

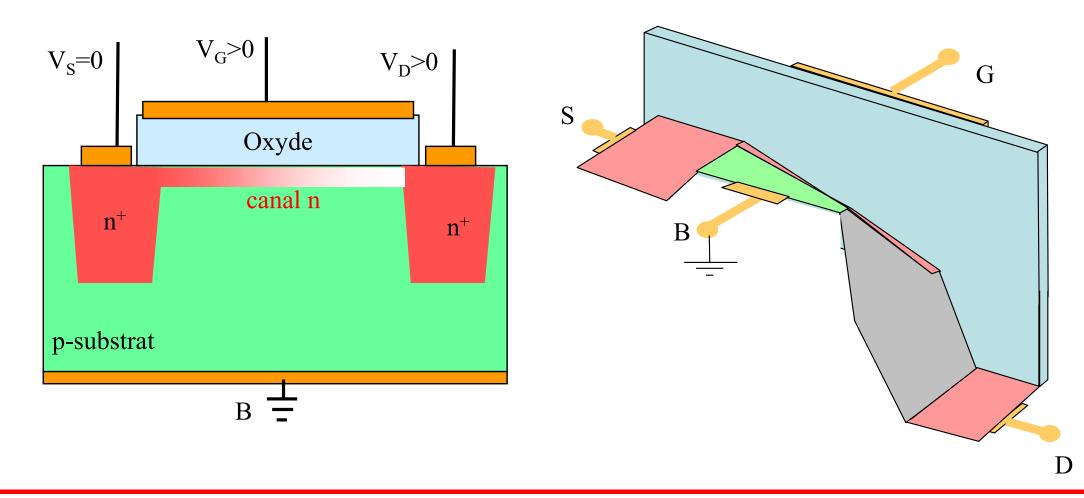

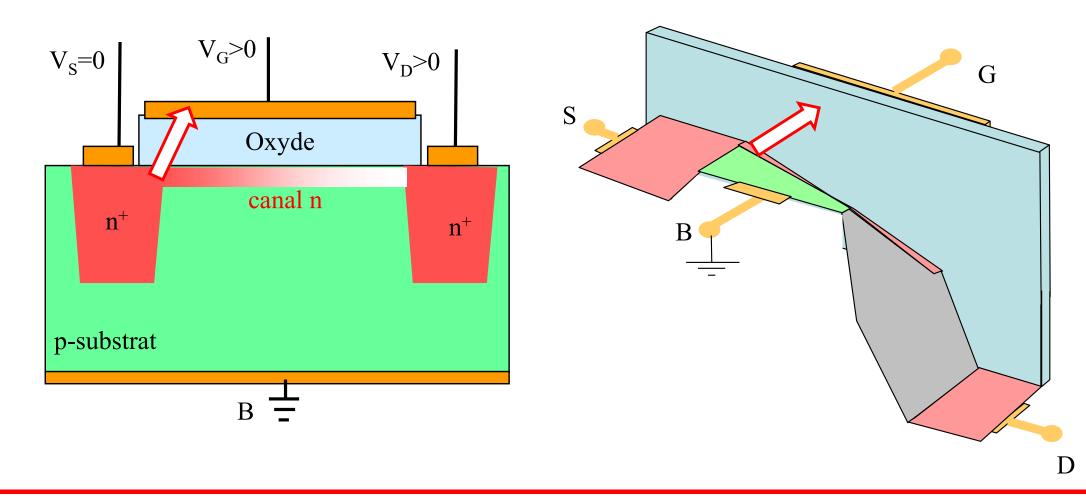

#### E10.4: MOSFET avec grille et drain court-circuités

- a) Lorsque la tension de drain et celle de gate sont court-circuitées ( $V_G=V_D$ ), comparez la tension de drain  $V_D$  avec la tension de saturation  $V_{D,sat}$ . (nous supposons une tension de threshold  $V_{M0}$  positive pour le NMOS, et la source et substrat connectés à la masse)

- b) Que peut-on en déduire sur le régime de fonctionnement du NMOS ?

- c) Déterminez la relation courant-tension de ce transistor NMOS avec la grille et le drain court-circuités.

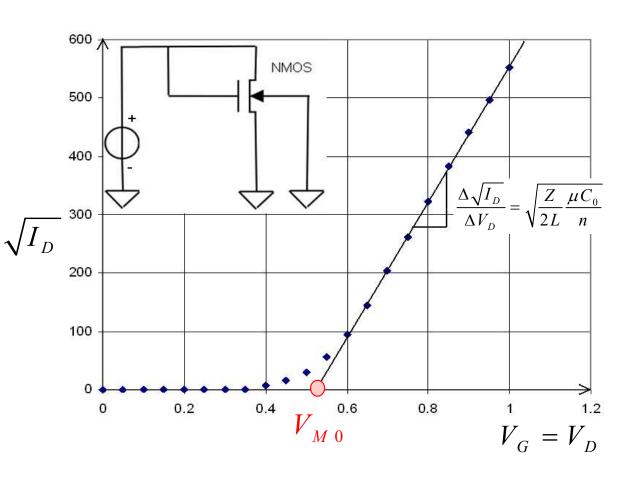

- d) Comment peut-on à partir de la mesure de cette caractéristique déterminer la tension de seuil ?

# Exercice 10.4: « diode connected NMOS »

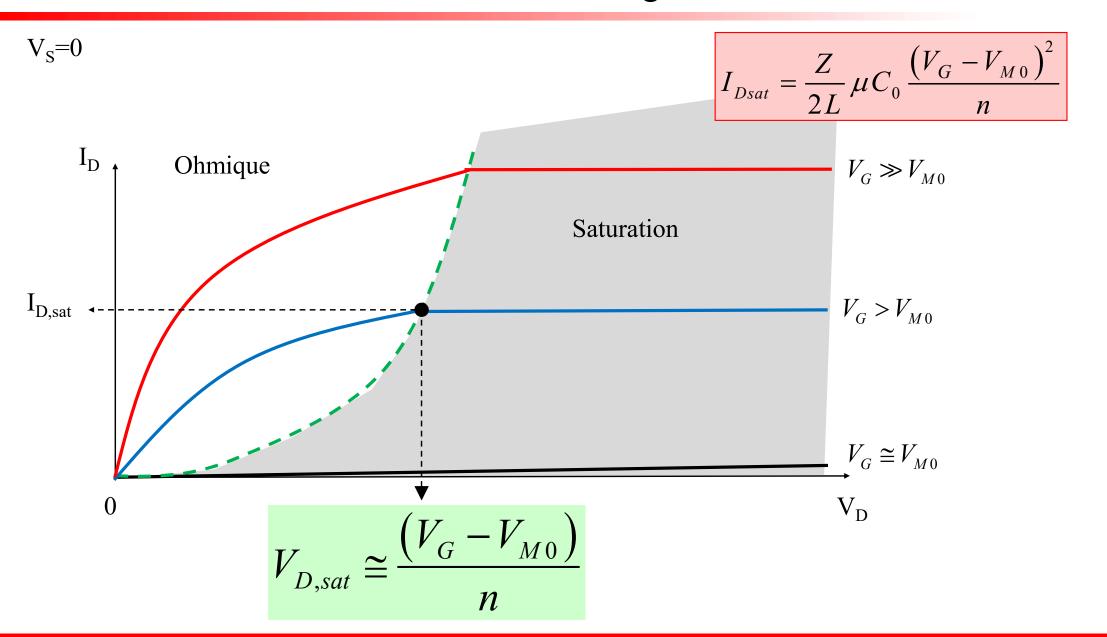

# Courbes de sortie en mode FET avec modulation de la longueur du canal

# Exercice 10.4: « diode connected NMOS »

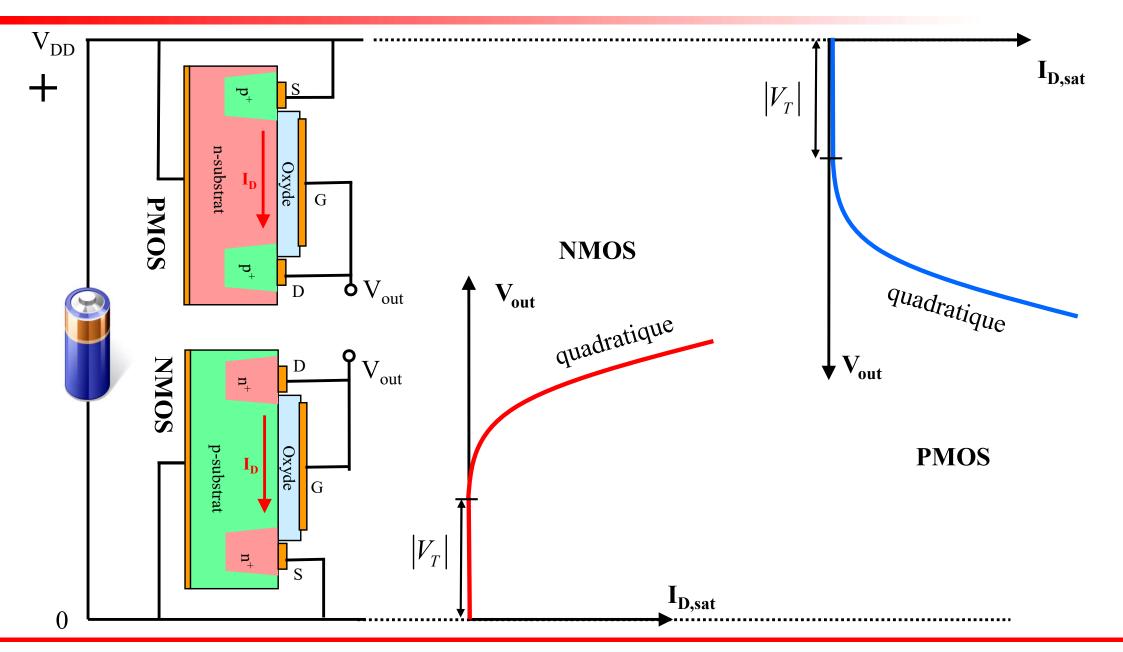

$$V_{Dsat} = \frac{V_G - V_{M0}}{n} = \frac{V_D - V_{M0}}{n} < V_D$$

Mode de saturation:

$$I_{Dsat} = \frac{Z}{2L} \mu C_0 \frac{\left(V_G - V_{M0}\right)^2}{n}$$

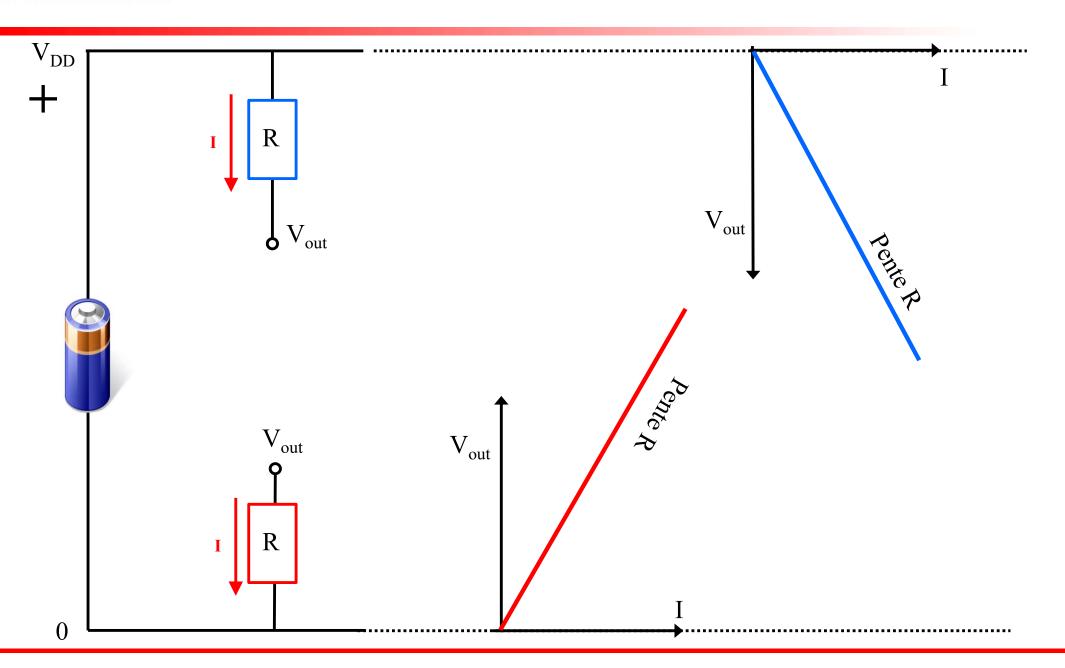

## Résistances de charge

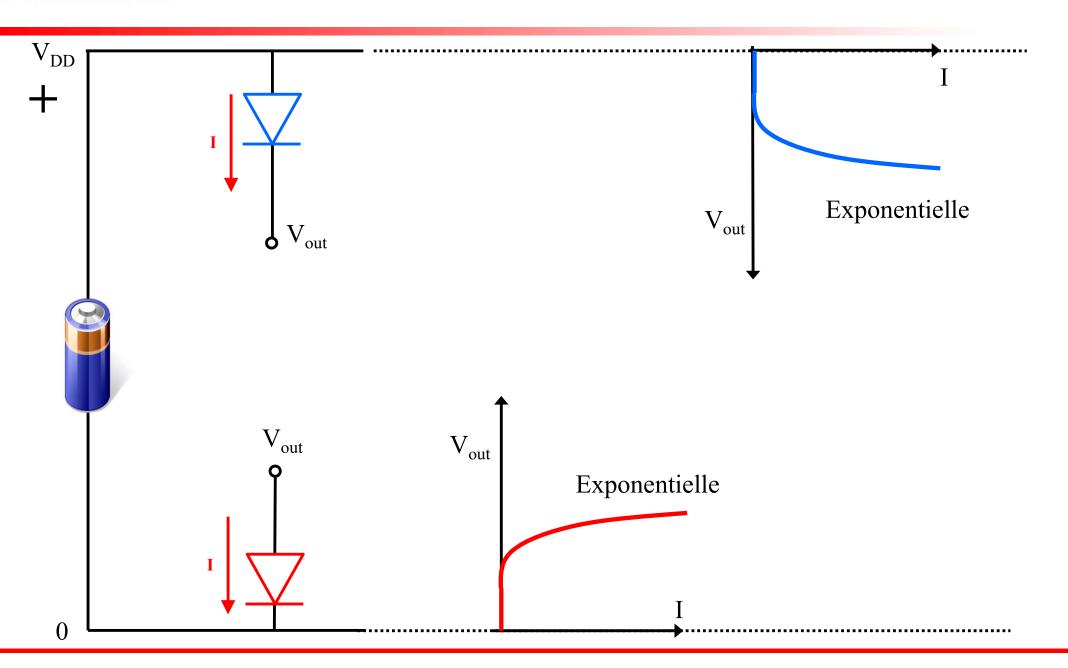

## Diodes de charge

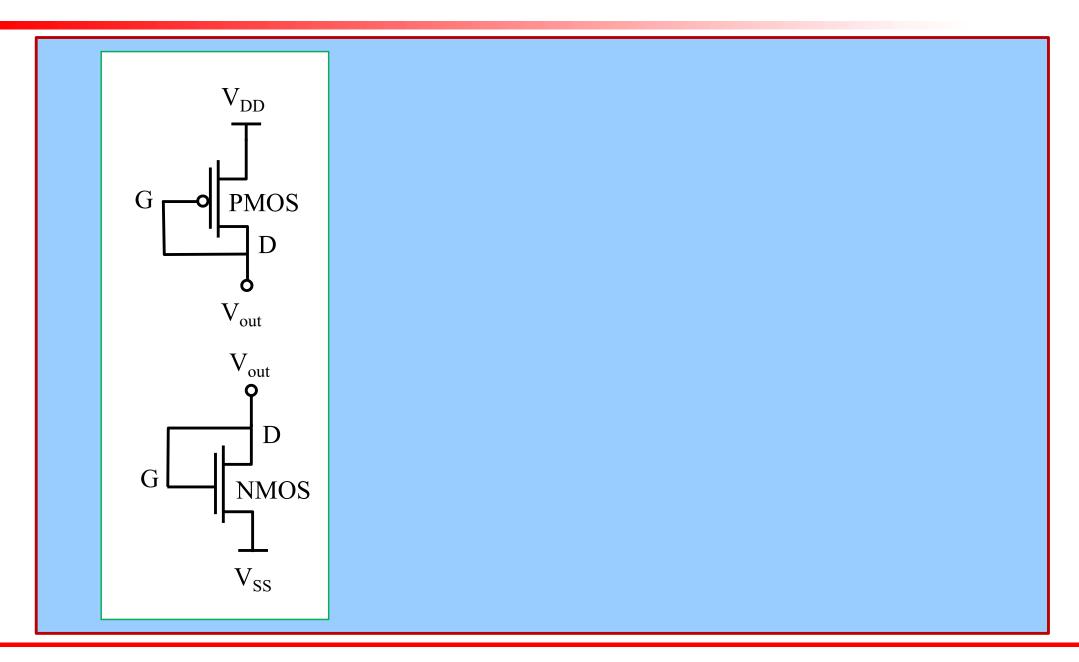

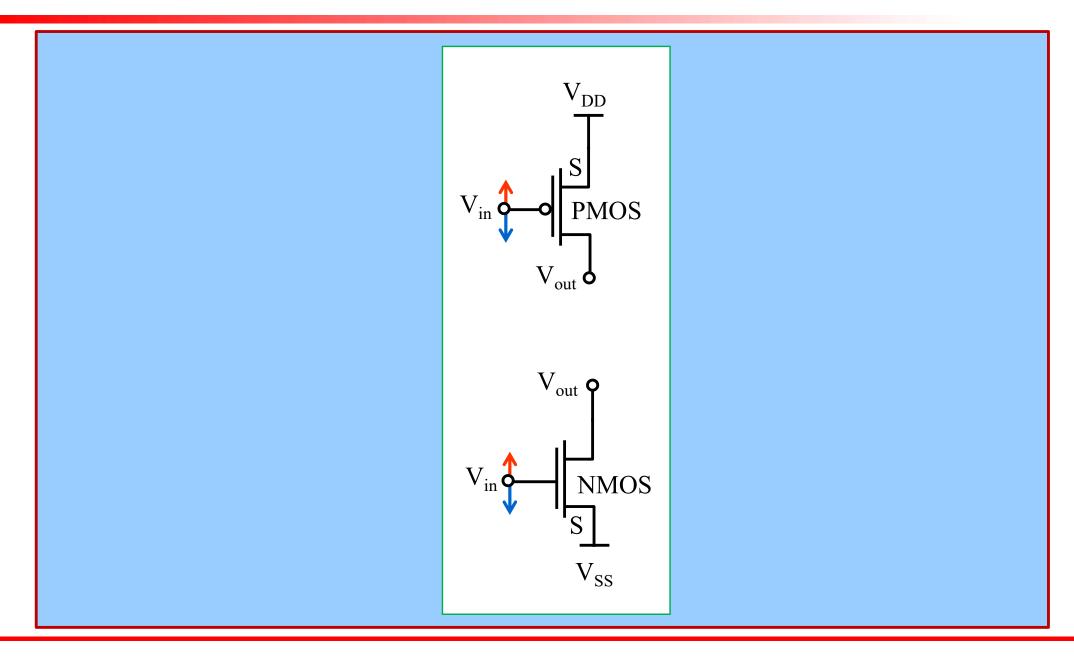

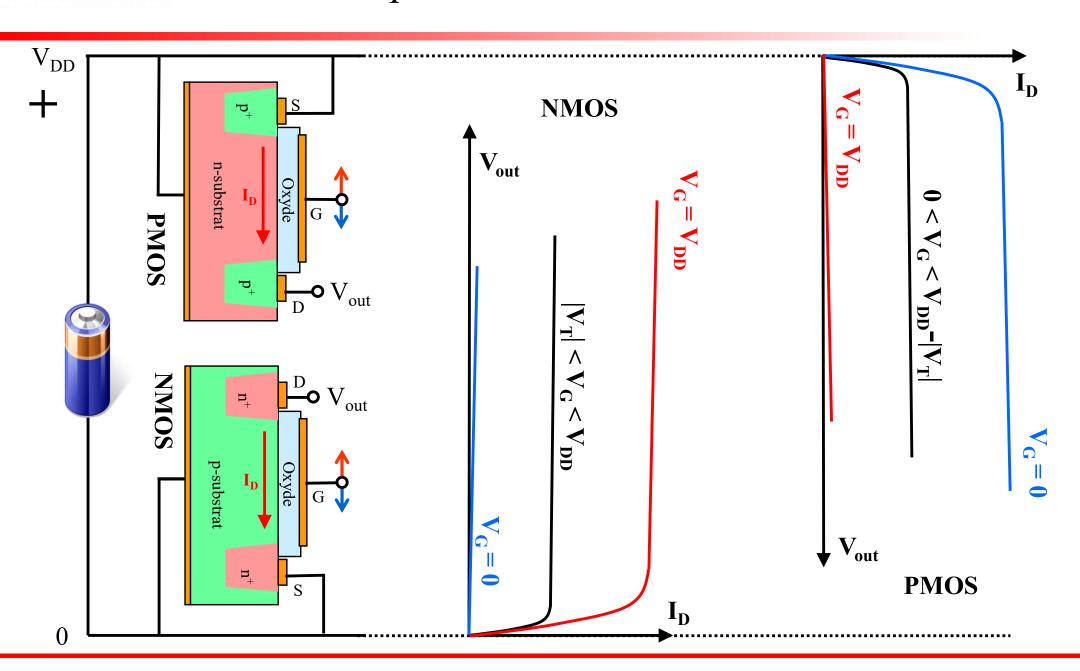

## Configurations en CMOS

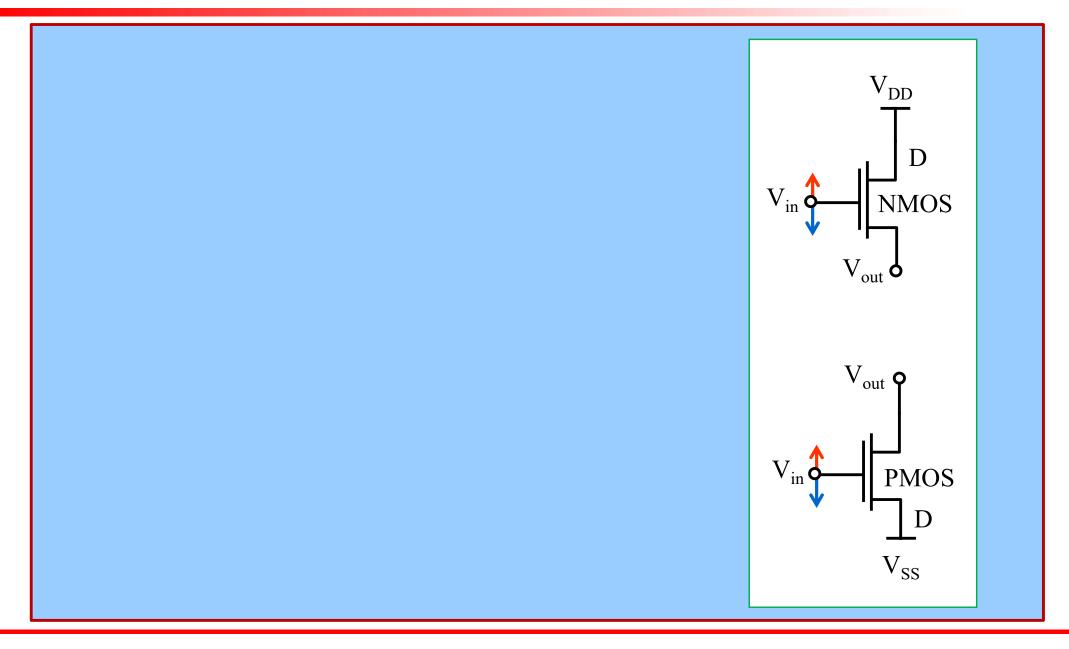

## Comparaison NMOS et PMOS avec G/D court-circuités

## Configurations en CMOS

## Comparaison NMOS et PMOS

## Configurations en CMOS

# Comparaison NMOS et PMOS en suiveurs