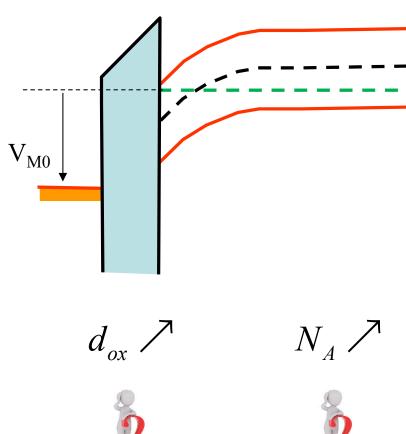

## Exercice E11.1: Contrôle de la tension de threshold $V_{M0}$

- a) Dessinez le schéma de bande d'une jonction MOS sur substrat p le long d'une droite verticale au milieu du gate à la tension  $V_G=V_{M0}$ .

- b) Considérons une augmentation de l'épaisseur de l'oxyde, tout en maintenant la structure au threshold:

- Comment varient le potentiel de surface, les charges d'espace dans la zone de déplétion, ainsi que le champ électrique dans l'oxyde.

- Comment varie la tension de threshold appliquée sur le gate ?

- c) Repartons de la situation a) et considérons maintenant une augmentation du dopage p du substrat, tout en maintenant la structure au threshold. Négligez la variation de  $\psi_B$ .

- Comment varient le potentiel de surface, les charges d'espace dans la zone de déplétion, le champ à l'interface semi-conducteur/oxyde ainsi que le champ électrique dans l'oxyde.

- Comment varie la tension de threshold appliquée sur le gate ?

<u>Idée:</u> Commencez votre analyse pour b) et c) à partir de la profondeur du substrat.

- d) Comparez vos résultats avec le cours chapitre 11!

# Exercice E11.1: Contrôle de la tension de threshold $V_{M0}$

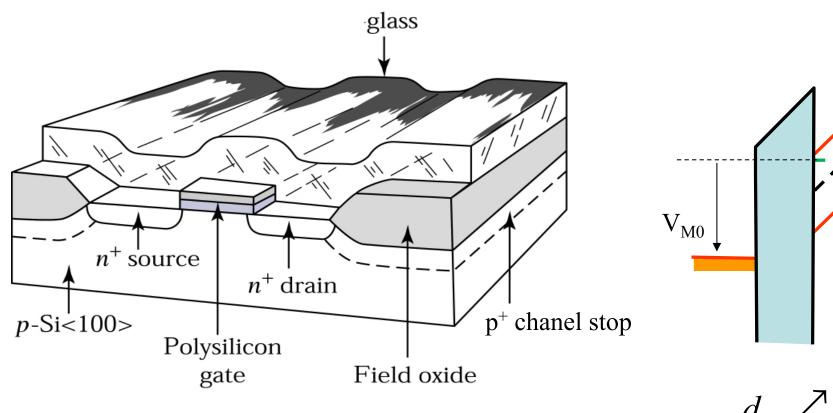

Semiconductor Devices, 2/E by S. M. Sze

$$V_{M0} = V_{fb} + 2\psi_B \left( 1 + 2 \frac{C_{B,th}}{C_{ox}} \right)$$

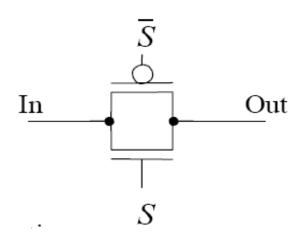

#### Exercices E11.2

#### E11.3: Transmission gate

- Considérez le circuit ci-contre. Les signaux sont digitaux. Trouvez la table de vérité donnant la sortie « out » en fonction de l'entrée « in » et du signal de contrôle « S ». « S » est l'inverse binaire de « S ».

- Pourquoi le PMOS est-il nécessaire ?

## Exercice 11.4: "Nanocrystals inside"

#### ক্ত Toulouse : TP « Nanocrystals inside » ক্ত

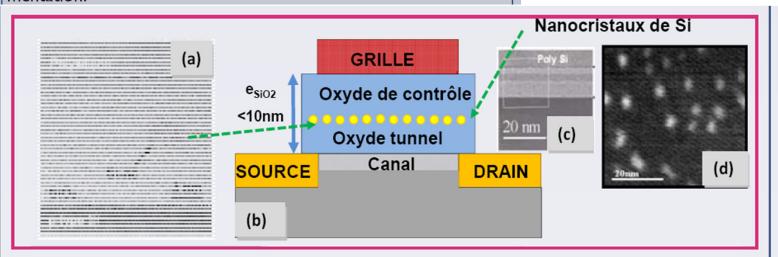

#### FABRICATION DE COMPOSANTS MEMOIRES MOS A BASE DE NANOCRISTAUX DE SILICIUM GÉNÉRALITÉS:

Cette formation de courte durée, en salle blanche, donne une approche pratique complète du concept « NANO-INSIDE » appliqué à l'intégration de nanocristaux de silicium dans la technologie NMOS. Il aborde alors toutes les opérations de fabrication des circuits intégrés de type « mémoires », ainsi que leurs caractérisations à la fois matériaux et composants. In fine, le but est de montrer comment une information peut être mémorisée avec des objets nanométriques de façon durable et conservée même sans alimentation.

### Lisez et interprétez ce texte

La puce à l'oreille No. 31, p. 4, nov. 2009.

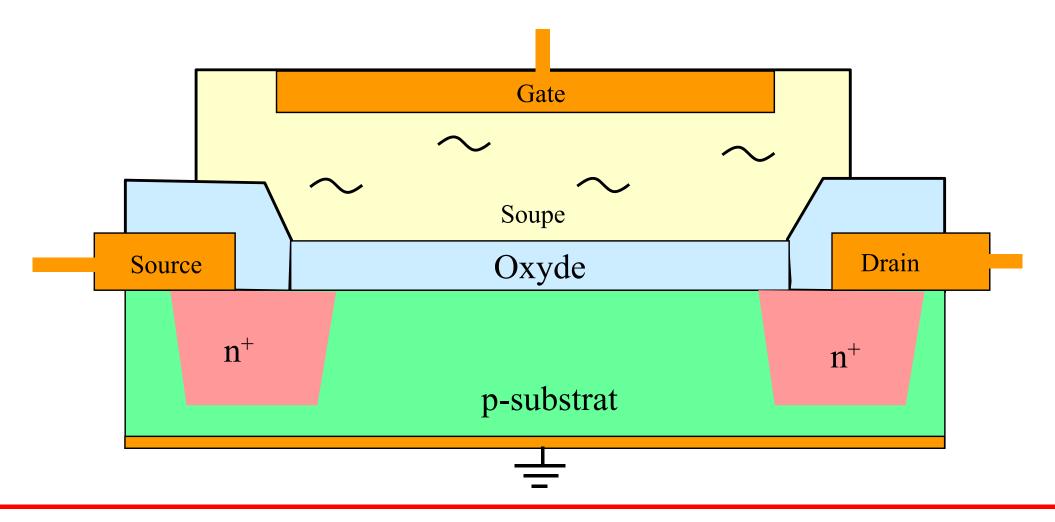

### Exercice 11.5 ISFET

Comment varie la tension de threshold si:

- A) la soupe contient des ions positifs (pH<7)

- B) la soupe contient des ions négatifs (pH>7)