### Institute of Electrical and Microengineering

Biomedical and neuromorphic microelectronic systems

Test of VLSI Systems2024, MNIS-MA3, EL-MA1, EL-MA3. EE530-2024-FWEP-v1.0.fm v1.0 A. Schmid 2024, October 22

# TEST OF VLSI SYSTEMS FINAL WRITTEN EXAMINATION POLICIES

#### 1. TIME AND PLACE

The duration of the final written examination is two hours.

The final written examination is scheduled by the Service Académique. Please check the web site of Service Académique prior to taking the exam, since the date and time may be changed.

http://is-academia.epfl.ch/

Provisionally, the examination has been scheduled by SAC on Wednesday, **January 29**, **2025**, from 15:15 through 17:15, in classroom BCH-2201.

It is your responsability to cross-check!

### 2. TOPICS

Full course, including the content of lectures, exercises, and practical laboratory sessions.

Following topics are part of the written examination.

Class #1 topics (full): Motivation for testing, economy of test, ATE, Yield and Defect level

Class #2 topics (full): Fault modeling

Class #3 topics (partial): Fault simulation, types of fault simulators, levelization, serial, parallel and deductive fault simulation

Class #4 topics (full): Testability measures, combinational and sequential SCOAP (the theory of sequential SCOAP is included!)

Class #5 topics (full): ATPG, combinational and sequential ATPG, search space abstractions, D-calculus and D-agorithm, concept of PODEM, time-frame expansion

Class #6 topics (full): Design for testability, scan-path design, JTAG boundary-scan

Class #7 topics (full): BIST I, LFSRs

Class #8 topics (full): BIST II, response/signature analysis, MISR, BILBO

Class #9 topics (full): memory faults, memory tests including march tests, Iddq.

Exercise #1, exercise #2, exercise #3, exercise #4, exercise #5, exercise#6, exercise#7.

Practical laboratory sessions are part of the written exam: be able to explain the concepts you have applied. Following topics are **not** part of the written examination

École

polytechnique

fédérale

de Lausanne

School of Engineering Institute of Electrical and Microengineering EPFL SCI-STI-AXS BNMS Station N° 11 CH - 1015 Lausanne

https://bnms.epfl.ch

Class #3 topics (partial): Concurrent fault simulation and fault sampling

Class #4 topics (partial): no exercise on sequential SCOAP will be proposed (the theory however, is in)

Class #9 topics (partial): slides 37-42 on delay-fault test generation.

(the class #, and exercise # refers to the number printed on the first page of the handout slides and exercises.)

### 3. EXAMINATION POLICIES

The final examination will be conducted as a closed-book examination. The examination will consist of theoretical questions to be answered (short and detailed), as well as exercises to be solved.

Student's ID card are controlled during the examination. Please place your student's ID on the forefront of the table

No question will be answered during the examination time. Should you be in situation of uncertainty, please carefully formulate all hypothesis or assumptions you are stating.

#### 4. DISTRIBUTED ITEMS

The examination documents including scratch paper (working sheets) will be distributed.

The formulary consisting of an arrangement of course transparencies, and provided with the Midterm Exam Policies document and the Midterm Exam will be distributed along with the examination documents.

### 5. RECOMMENDED ITEMS

Please make sure to bring pens, pencils.

### 6. FORBIDDEN ITEMS

No written document of any sort may be taken to the examination (no book, no transparencies, no handwritten notes, etc.). Blank paper will be provided.

Usage of information processing and telecommunication devices in a general sense is not permitted (no computer, no hand calculator, no electronic agenda, no cell phone, etc.).

### 7. GRADING

The final is graded, and accounts for 50% of the course grade.

### 8. COURSE WEB SITE

Please check the course web site on a regular basis.

URL: http://moodle.epfl.ch/course/view.php?id=293

# Test of VLSI Systems Final written examination

### Formulary

This document must be returned along with the examination documents

FF530 2024

Test of VLSI Systems - Class 2024 - BNMS/EPFL

Midterm/FinalFormulary 1

# Cost of production test

$$C_s = ((D_t + D_h) + M_t + O_t) \cdot (\frac{1}{T_{test,per}}) \cdot (\frac{T_{prod,per} + T_{down,per} + T_{idle,per}}{T_{prod,per}})$$

$$\uparrow \qquad \qquad \uparrow \qquad \qquad \uparrow$$

$$\uparrow \qquad \qquad \uparrow \qquad \qquad \uparrow$$

$$\downarrow \qquad \qquad \uparrow \qquad \qquad \uparrow$$

$$\downarrow \qquad \qquad \uparrow \qquad \qquad \uparrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \downarrow$$

$C_s$ = cost of testing per second

= depreciation of tester and handler over the period  $T_{test.per}$ :  $D_t$ ,  $D_h$

$D_t + D_h = C_t / (T_{test tot} / T_{test per})$  (linear depreciation)

C, = fixed cost of tester = maintenance cost

O<sub>t</sub> = operating cost and personnel (building, facilities, auxiliary equipment)

= total testing time (typically given in years

= testing time during period per (typically given in weeks) T<sub>test per</sub>

= usage time of tester during period per = down time of tester during period per T<sub>idle,per</sub> = idle time of tester during period per

# Cost of production test

Testing cost =

$$N_c \cdot C_s \cdot T_m$$

$N_c$  = total number of circuits

C<sub>s</sub> = cost of testing per second

$T_m$  = mean time of testing per circuit

$$T_{m} = \sum_{i=1}^{n} T_{i} (1 - P_{i-1})$$

= number of test vectors

= processing time for test number i

= probability of a defect to be detected during the application of tests prior to test i

FF530 2024

Test of VLSI Systems - Class 2024 - BNMS/EPFL

Midterm/FinalFormulary 2

## Fault list propagation rules

propagation rules for main Boolean gates in a deductive fault simulator

| Gate | Input |   | output | output fault list L <sub>7</sub>          |  |

|------|-------|---|--------|-------------------------------------------|--|

| Gate | a     | b | z      | output lault list Lz                      |  |

| AND  | 0     | 0 | 0      | $[L_a \cap L_b] \cup z_I$                 |  |

|      | 0     | 1 | 0      | $[L_a \cap \overline{L_b}] \cup z_l$      |  |

|      | 1     | 0 | 0      | $[\overline{L_a} \cap L_b] \cup z_I$      |  |

|      | 1     | 1 | 1      | $[L_a \cup L_b] \cup z_0$                 |  |

| OR   | 0     | 0 | 0      | $[L_a \cup L_b] \cup z_I$                 |  |

|      | 0     | 1 | 1      | $[\overline{L_a} \cap L_b] \cup z_\theta$ |  |

|      | 1     | 0 | 1      | $[L_a \cap \overline{L_b}] \cup z_0$      |  |

|      | 1     | 1 | 1      | $[L_a \cap L_b] \cup z_0$                 |  |

| NOT  | 0     |   | 1      | $L_a \cup z_0$                            |  |

|      | 1     |   | 0      | $L_a \cup z_1$                            |  |

U stands for union, ∩ represents intersection, and — complementation

Test of VLSI Systems - Class 2024 - BNMS/EPFL

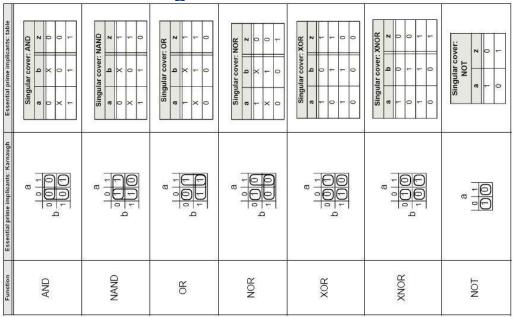

### Singular cover tables

EE530 2024

Test of VLSI Systems - Class 2024 - BNMS/EPFL

Midterm/FinalFormulary 5

## D-calculus (2)

$\phi$  empty,  $\Psi$  undefined:

- the cubes are incompatible

- meeting a  $\Psi$  and  $\phi$  during the progression of the algorithm means that the proposed solution is not viable → backtrack to another solution

example: intersection of cubes 0XX and 1XX  $0XX \cap 1XX = \phi XX$ these two cubes cannot coexist

$\lambda$  or  $\mu$  requires inversion of D and  $\overline{D}$ :

- if both  $\lambda$  and  $\mu$  occur during D-intersection, then the cubes are incompatible

- if only  $\mu$  occurs, then  $D \cap D = D$  and  $\overline{D} \cap \overline{D} = \overline{D}$

- if only  $\lambda$  occurs

- 1. transform the second cube as follows:  $D \rightarrow D$  and  $D \rightarrow D$

- 2. then, apply D-intersect again, considering the  $\mu$  rule described above

## D-calculus (1)

D-intersection defines how different D-cubes coexist for different gates in the circuit

This set of rules is applied in the propagation phase, where D must be propagated to a primary output, and justification phase

| $\cap$ | 0 | 1 | Х | D | D |

|--------|---|---|---|---|---|

| 0      | 0 | ф | 0 | Ψ | Ψ |

| 1      | ф | 1 | 1 | Ψ | Ψ |

| Х      | 0 | 1 | Х | D | D |

| D      | Ψ | Ψ | D | μ | λ |

| D      | Ψ | Ψ | D | λ | μ |

$\phi$  empty,  $\Psi$  undefined,  $\lambda$  or  $\mu$  requires inversion of D and  $\overline{D}$

FF530 2024

Test of VLSI Systems - Class 2024 - BNMS/EPFL

Midterm/FinalFormulary 6

## March test notation (1)

Following notation is standard in the description of memory testing protocols

| Notation     | Action                                                                |  |  |

|--------------|-----------------------------------------------------------------------|--|--|

| r            | read operation                                                        |  |  |

| W            | write operation                                                       |  |  |

| r0           | read a 0 from the memory location                                     |  |  |

| r1           | read a 1 from the memory location                                     |  |  |

| w0           | write a 0 to the memory location                                      |  |  |

| w1           | write a 1 to the memory location                                      |  |  |

| 1            | write a 1 to a cell containing a 0: the cell has a rising transition  |  |  |

| <b>\</b>     | write a 0 to a cell containing a 1: the cell has a falling transition |  |  |

| <b>\$</b>    | complement the cell contents                                          |  |  |

| $\forall$    | any memory write operation                                            |  |  |

| ↑ ↑          | increase memory address                                               |  |  |

| $\downarrow$ | decrease memory address                                               |  |  |

| <b>1</b>     | addressing order can be either increasing or decreasing               |  |  |