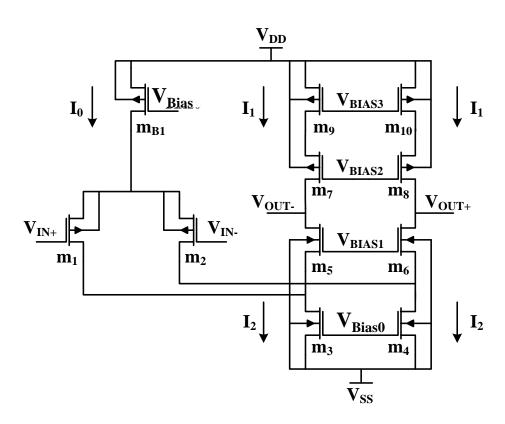

# 1. Fully differential folded cascode OTA: Procedural sizing

The purpose of this section is to provide the sizing procedure of the following OTA step-by-step. Starting by choosing circuit-level parameters (specifications) and propagating them to transistor level.

The technology used is CMOS 80nm 1.8V devices and their parameters are:

| Parameter  |             | Unit      |                        |  |

|------------|-------------|-----------|------------------------|--|

|            |             | Extracted |                        |  |

| PMOS       |             | 40        | . mr                   |  |

| Kp         | NMOS        | 208       | $\mu$ A/V <sup>2</sup> |  |

| <b>T</b> T | PMOS        | 16        | <b>T</b> 7/            |  |

| Ua         | NMOS        | 5         | V/µm                   |  |

|            | <b>PMOS</b> | 1.3       |                        |  |

| n          | NMOS        | 1.2       | -                      |  |

|            | Cox         | 8.3       | fF/μm²                 |  |

The OTA, have to meet the following specifications.

| Doromatar               | Value         | I Init |      |  |

|-------------------------|---------------|--------|------|--|

| Parameter               | Specification |        | Unit |  |

| Open-loop gain          | > 70          |        | dB   |  |

| GBW                     | 60            |        | MHz  |  |

| Slew rate [SR]          | 50            |        | V/µs |  |

| Load capacitors $[C_L]$ | 100           |        | fF   |  |

| Family Name: | First Name: |            |

|--------------|-------------|------------|

| Test         | 29/11/2019  | 8h15/10h45 |

#### 1.1. Bias currents

| _ |     | Parameter | Expression               | Value | Unit | Guideline |

|---|-----|-----------|--------------------------|-------|------|-----------|

|   | ias | $I_0$     | $I_0$                    |       | μΑ   |           |

|   | В   | $I_1$     | $1,2 	imes rac{I_o}{2}$ |       | μΑ   |           |

## 1.2. Differential pair

Determine the transconductance, inversion factor and W/L ratio of the differential pair.

|                   | Parameter                | Expression | Value | Unit | Guideline |

|-------------------|--------------------------|------------|-------|------|-----------|

| Differential pair | $g_{m1,2}$               |            |       | μS   |           |

|                   | $I_{f1,2}$               |            |       | -    |           |

| Diff              | $rac{W_{1,2}}{L_{1,2}}$ |            |       | -    |           |

### 1.3. Folded cascade load

The 8 transistors composing the folded cascode stage will now be sized.

Determine the inversion factor and W/L ratio of these transistors to:

- Keep all saturation voltages of m 9,10, m 7,8, m 5,6 small

- Minimize the noise and offset contribution of m<sub>3</sub> and m<sub>4</sub>

- For simplification, only two values will be chosen for the inversion factor:  $I_F = 10$  or  $I_F = 1$ .

|       | Parameter            | Expression | Value | Unit | Guideline |

|-------|----------------------|------------|-------|------|-----------|

| olded | $rac{W_{5}}{L_{5}}$ |            |       |      |           |

| Fol   | $rac{W_7}{L_7}$     |            |       |      |           |

| Family Name: | First Name: | <u>.</u>   |  |

|--------------|-------------|------------|--|

| Cest         | 29/11/2019  | 8h15/10h45 |  |

| $rac{W_9}{L_9}$ |  |  |

|------------------|--|--|

| $rac{W_3}{L_3}$ |  |  |

Calculate the output resistance necessary to meet the open-loop gain specification.

| -    | Parameter        | Expression | Value | Unit | Guideline |

|------|------------------|------------|-------|------|-----------|

| Rout | R <sub>out</sub> |            |       | ΜΩ   |           |

Neglecting the conductance of the differential pair (assume  $g_{ds1} \approx 0.5 g_{ds3}$ ), determine the conductance and length of all transistors so that:

- The specified open-loop gain is achieved

- The NMOS and PMOS resistances at the output node are balanced (  $R_{up} = R_{down}$  )

- The total area of the folded cascade stage is minimized (in the order of  $85 \mu m^2$ )

- m<sub>7</sub> and m<sub>9</sub> have the same length

- The length of  $m_3$  is two times the one of  $m_5$

|      | Parameter                 | Expression | Value | Unit            | Guideline   |

|------|---------------------------|------------|-------|-----------------|-------------|

|      | $n_{n,p} \times g_{m5,7}$ |            |       | μS              |             |

|      | $R_{up}$                  |            |       | МΩ              |             |

| Rout | $L_7 \times L_9$          |            |       | μm <sup>2</sup> |             |

| RC   | $L_9$                     |            |       | nm              | $L_7 = L_9$ |

|      | $L_7$                     |            |       | nm              | $L_7 = L_9$ |

|      | $R_{down}$                |            |       | ΜΩ              |             |

| $L_3 \times L_5$ |  | μm <sup>2</sup> |              |

|------------------|--|-----------------|--------------|

| $L_5$            |  | μm              | $L_3 = 2L_5$ |

| $L_3$            |  | μm              | $L_3 = 2L_5$ |

Calculate the width of all transistors.

|      | Parameter | Expression                   | Value | Unit | Guideline |

|------|-----------|------------------------------|-------|------|-----------|

|      | $W_3$     | $\frac{W_3}{L_3} \times L_3$ |       | μm   |           |

| Rout | $W_5$     | $\frac{W_5}{L_5} \times L_5$ |       | μm   |           |

| Rc   | $W_7$     | $\frac{W_7}{L_7} \times L_7$ |       | μm   |           |

|      | $W_9$     | $\frac{W_9}{L_9} \times L_9$ |       | μm   |           |

# 1.4. Differential pair finalization & Current source

Find the length and the width of the differential pair.

| Parameter | Expression | Value | Unit | Guideline                 |

|-----------|------------|-------|------|---------------------------|

| $L_1$     |            |       | nm   | $g_{ds1} \le 0.5 g_{ds3}$ |

| $W_1$     |            |       | μm   |                           |

| Parameter | Expression | Value | Unit | Guideline |

|-----------|------------|-------|------|-----------|

| $L_{B1}$  |            |       | nm   |           |

| $W_{B1}$  |            |       | μm   |           |

| Family Name: | First Name: | <u>.</u>   |

|--------------|-------------|------------|

| Test         | 29/11/2019  | 8h15/10h45 |

#### 1.5 Offset Estimation:

In case of the above folded cascade, give the expression of the input referred offset that include the contribution of Differential pair: m<sub>1,2</sub>; Folded cascode: m<sub>3,4</sub> and Active load: m<sub>9,10</sub>

$$\sigma_{Vos}^{2} =$$

$$\sigma_{I_{D}(\beta,V_{T0})}^{2} = \sigma_{\beta}^{2} \left(\frac{\partial I_{D}}{\partial \beta}\right)^{2} + \sigma_{V_{T0}}^{2} \left(\frac{\partial I_{D}}{\partial V_{T0}}\right)^{2}$$

$$= \sigma_{\beta}^{2} \left(\frac{I_{D}}{\beta}\right)^{2} + \sigma_{V_{T0}}^{2} \left(g_{m}\right)^{2}$$

$$= \sigma_{\beta}^{2} \left(\frac{I_{D}}{\beta}\right)^{2} + \sigma_{V_{T0}}^{2} \left(g_{m}\right)^{2}$$

### 1.6 Common-mode feedback CMFB

Propose a CMFB circuit that use two differential pairs to tune the gate voltage of MB1 and set the common-mode output voltage to  $V_{DD}/2$ . Show how this CMFB circuit is connected to the fully differential cascode OTA (i.e. give the name of its input and output nodes):

### **CMFB** schematic:

| Family Name: | First Name: | <u> </u>   |

|--------------|-------------|------------|

| Test         | 29/11/2019  | 8h15/10h45 |

1.7 Propose and size an optimal biasing circuit for V<sub>Bias0-3</sub>