## Fundamentals of Analog & Mixed Signal VLSI Design Exercise 5 (16.10.2024)

#### Christian Enz

Swiss Federal Institute of Technology (EPFL), Lausanne, Switzerland

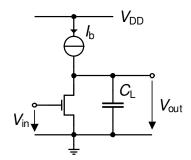

In this exercise we want to apply the  $G_m/I_D$  design methodology using the inversion coefficient IC to the simple common source amplifier shown in Fig. 1 for various specifications. For the design we assume a generic 180 nm CMOS process with the parameters given in Table 1.

Figure 1: Common source amplifier.

Table 1: Technology parameters of an n-channel transistor for a generic 180-nm CMOS process

| Parameter        | Value                                                 |

|------------------|-------------------------------------------------------|

| $V_{DD}$         | 1.8 <i>V</i>                                          |

| $C_{ox}$         | 8.443 $\frac{fF}{\mu m^2}$                            |

| $W_{min}$        | 200 <i>nm</i>                                         |

| $L_{min}$        | 180 <i>nm</i>                                         |

| $\Delta W$       | 54 <i>nm</i>                                          |

| $\Delta L$       | −76 <i>nm</i>                                         |

| $V_{T0}$         | 0.455 <i>V</i>                                        |

| n                | 1.27                                                  |

| $I_{spec}\Box$   | 715 <i>nA</i>                                         |

| L <sub>sat</sub> | 26 nm                                                 |

| $\lambda$        | $20 \frac{V}{\mu m}$                                  |

| $K_F$            | $8.1	imes10^{-24}$ $J$                                |

| ho               | $5.794 \times 10^{-2}  \frac{V \cdot m^2}{A \cdot s}$ |

| $C_J$            | $1 \frac{fF}{\mu m^2}$                                |

| $C_{JSW}$        | $0.2 \frac{fF}{\mu m}$                                |

| $C_{GSo}$        | $0.366  rac{\mathit{fF}}{\mu \mathit{m}}$            |

| $C_{GDo}$        | $0.366  rac{\mathit{fF}}{\mu \mathit{m}}$            |

| $C_{GBo}$        | 0 <u>fF</u>                                           |

Note that the effective channel width and length are defined as follows

$$W_{eff} \triangleq W + \Delta W, \tag{1}$$

$$L_{\text{eff}} \stackrel{\triangle}{=} L + \Delta L, \tag{2}$$

where W and L are drawn width and length.

### Problem 1 Imposing the gain bandwidth product (unity gain frequency)

Design the CS amplifier shown in Fig. 1, for the following specifications at room temperature ( $U_T = 25.9 \text{ mV}$ ):

$$f_u = 100 \; MHz, \quad C_L = 1 \; pF, \quad IC = 1, \quad L_{long} = 1 \; \mu m, \quad L_{short} = 180 \; nm.$$

Carry out the design procedure both for long- and short-channel devices in saturation, using the drawn lengths  $L_{long}$  and  $L_{short}$  respectively. Note that velocity saturation (VS) has to be accounted for in the short-channel case. We assume that the self-loading capacitance at the drain can be neglected (i.e. assume a constant load capacitance equal to  $C_L$ ).

- · Draw the equivalent small-signal schematic ignoring the transistor parasitic capacitances.

- Derive the transfer function  $A_v(s) \triangleq \Delta V_{out}/\Delta V_{in}$  and extract the expressions of the dc gain, cut-off frequency and gain-bandwidth product (unity gain frequency)  $f_u$ .

- Find the transistor transconductance value  $G_m$ .

- Find the normalized source transconductance  $g_{ms}(IC) \triangleq G_{ms}/G_{spec} = nG_m/G_{spec} = nU_T G_m/I_{spec}$  from the imposed inversion coefficient IC. Then, deduce the specific current  $I_{spec}$  and the bias current  $I_b$ . Calculate the power consumption.

- Find the  $W_{\it eff}/L_{\it eff}$  ratio and the effective width  $W_{\it eff}$  for both the long and short channel case using the given drawn length L. Derive the drawn width W.

- Deduce the output conductance value  $G_{ds}$  and then calculate the dc gain value assuming the bias current source is ideal.

- Simulate the circuit using the Smash simulator and compare the theoretical results with the simulations.

### Problem 2 Imposing the power consumption

Design the same CS amplifier shown in Fig. 1 for the following specifications at room temperature ( $U_T = 25.83 \text{ mV}$ ):

$$P_{max} = 100 \,\mu W$$

,  $C_L = 1 \,pF$ ,  $IC = 1$ ,  $L_{long} = 1 \,\mu m$ ,  $L_{short} = 180 \,nm$ .

Carry out the design procedure both for long- and short-channel devices in saturation, using the drawn lengths  $L_{long}$  and  $L_{short}$  respectively. Note that velocity saturation (VS) has to be accounted for in the short-channel case. We assume that the self-loading capacitance at the drain can be neglected (i.e. assume a constant load capacitance  $C_L$ ).

- Find the bias current  $I_b$  for the specified maximum power consumption.

- Find the transconductance value of the transistor for the given inversion coefficient *IC* by means of the current efficiency.

- Find the unity gain-bandwidth product using the specific current  $I_{spec}$ . Calculate the power consumption.

- Find the  $W_{eff}/L_{eff}$  ratio and the effective width  $W_{eff}$  for both the long and short channel case using the given drawn length L. Derive the drawn width W.

- Deduce the output conductance value  $G_{ds}$  and then calculate the dc gain value assuming the bias current source is ideal.

- Simulate the circuit using the Smash simulator and compare the theoretical results with the simulations.

### Problem 3 Imposing the gain bandwidth product and the current budget

Design the same CS amplifier shown in Fig. 1 imposing both the gain-bandwidth product and the current budget with the following specifications at room temperature ( $U_T = 25.83 \,\text{mV}$ ):

$$f_{u} = 9 \text{ MHz}, \quad I_{b} = 400 \text{ nA}, \quad C_{L} = 1 \text{ pF}, \quad L_{long} = 1 \text{ } \mu\text{m}.$$

Carry out the design procedure only for the long-channel case with  $L = L_{long}$ .

- · Find the transistor transconductance value.

- Find the inversion coefficient IC by means of the current efficiency and then the I<sub>spec</sub>.

- Find the W<sub>eff</sub>/L<sub>eff</sub> ratio and the effective width W<sub>eff</sub> for the long channel case only using the given drawn length L. Derive the drawn width W.

- Deduce the output conductance value  $G_{ds}$  and then calculate the dc gain value assuming the bias current source is ideal.

- Simulate the circuit using the Smash simulator and compare the theoretical results with the simulations.

#### Problem 4 Imposing the input-referred noise

In this problem we want to design the CS amplifier shown in Fig. 1 imposing the input-referred noise including both the thermal and flicker noise. The specifications at room temperature ( $U_T = 25.83 \,\text{mV}$ ) are given below:

$$f_k = 100 \text{ kHz}, \quad \sqrt{S_{nth}} = 30 \text{ nV} / \sqrt{Hz}, \quad C_L = 1 \text{ pF}, \quad IC = 1, \quad \gamma_n = 0.72$$

where  $f_k$  is the noise corner frequency and  $S_{nth}$  is the input-referred thermal noise power spectral density (PSD).

- Using  $S_{nth}$  determine the transconductance  $G_m$ .

- Find the normalized transconductance  $g_{ms}(IC)$ .

- Determine the specific current  $I_{spec}$ , the bias current  $I_b$  and the  $W_{eff}/L_{eff}$  ratio.

- Using the noise corner frequency  $f_k$ , determine the effective gate area  $W_{eff} \cdot L_{eff}$ .

- Finally, calculate the effective and drawn dimensions of the transistor.

- Simulate the circuit using the Smash simulator and compare the theoretical results with the simulations.

# Problem 5 Minimum current for a given gain-bandwidth product accounting for self-loading

In this problem we want to account for the self-loading effect which is particularly important when the transistor is getting wide which typically happens in weak inversion. The specifications at room temperature ( $U_T = 25.83 \,\text{mV}$ ) are given below:

$$f_u = 25 \; MHz, \quad C_{L0} = 20 \; fF, \quad C_W = 1.167 \; \frac{fF}{\mu m}, \quad L = 1 \; \mu m.$$

Follow the procedure illustrated in the lecture notes.

# Problem 6 Minimum current for a given gain-bandwidth product accounting for self-loading

In this problem we want to account for the self-loading effect but use the additional degree of freedom, namely the transistor gate length, to set the dc gain. The specifications at room temperature ( $U_T = 25.83 \,\text{mV}$ ) are given below:

$$f_u = 25 \; MHz, \quad A_{dc} = 40 \; dB, \quad C_{L0} = 20 \; fF, \quad C_W = 1.167 \; \frac{fF}{\mu m}.$$

Follow the procedure illustrated in the lecture notes.