### Fundamentals of Analog & Mixed Signal VLSI Design

### **Switched-capacitor Circuits and Filters**

#### Christian Enz

Institute of Electrical and Micro-engineering (IEM), School of Engineering (STI)

Swiss Federal Institute of Technology, Lausanne (EPFL), Switzerland

### **Outline**

- Introduction

- Basic principles

- Non-ideal effects in SC circuits

- The design of switched-capacitor filters (SCF)

# **History and Motivations**

- Idea initially originates from Maxwell in "A Treatise on Electricity and Magnetism" 1873

- Applied to IC for implementing sampled-data filters in 1972 by D. L. Fried, "Low-, High- and Band-pass SC Filters"

- Idea to use SC in analog-to-digital converters (ADCs) proposed in 1975 by Mc

Creary and P. Gray

- Basic principle: signal entered and read-out as voltages, but processed internally as charge packets sampled on capacitors

- Possible thanks to high quality integrated capacitors and controlled switches provided by CMOS technology

- Replaces absolute accuracy of RC time constants (10%-30%) by matching of capacitors (0.05%-0.2%)

### **Outline**

- Introduction

- Basic principles

- Non-ideal effects in SC circuits

- The design of switched-capacitor filters (SCF)

# **Basic Principle**

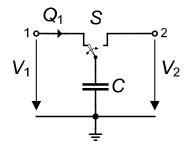

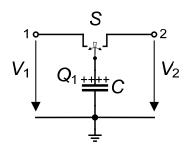

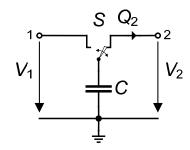

$$V_C(nT) = V_2 \quad V_C(t) = V_2$$

$$Q_1 = C \cdot (V_1 - V_2)$$

$$V_1$$

$V_c(nT) = V_1$   $V_c(t) = V_1$   $V_c(nT) = V_1$   $V_c(t) = Q_1 = C \cdot (V_1 - V_2)$   $Q_2 = C \cdot (V_1 - V_2)$

$$V_c(nT) = V_2$$

$V_c(t) = V_1$   $V_c(nT) = V_1$   $V_c(nT) = V_1$   $V_c(nT) = V_1$   $V_c(nT) = V_2$   $O_1 = C \cdot (V_1 - V_2)$   $O_2 = C \cdot (V_1 - V_2)$

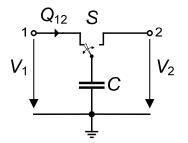

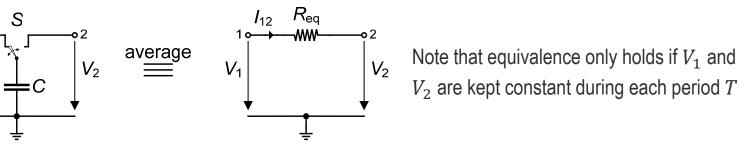

During each period T, a charge  $Q_1 = Q_2 = Q_{12} = C \cdot (V_1 - V_2)$  is transferred from node 1 to node 2, corresponding to an average current

$$\overline{I_{12}} = \frac{Q_{12}}{T} = \frac{C}{T} \cdot (V_1 - V_2) = f_S \cdot C \cdot (V_1 - V_2) = \frac{V_1 - V_2}{R_{eq}} \text{ with } R_{eq} = \frac{T}{C} = \frac{1}{f_S \cdot C}$$

•  $R_{eq}$  is inversely proportional to C and  $f_S$

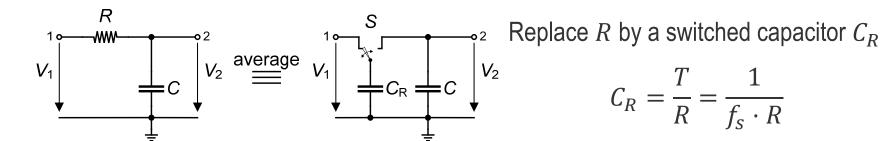

# 1<sup>st</sup>-order Low-pass Filter

The time constant and cut-off frequency of this simple 1<sup>st</sup>-order circuit are given by

$$au = RC = T \cdot \frac{C}{C_R}$$

and  $\omega_C = \frac{1}{RC} = f_S \cdot \frac{C_R}{C}$

- The cut-off frequency  $\omega_c$  of the 1<sup>st</sup>-order SCC is **proportional to the sampling** frequency and now depends only on the capacitor ratio  $C_R/C$

- This is the fundamental property of SC circuits that enables their integration in a CMOS process since the absolute values of capacitances are only controlled within 10% to 30% whereas their ratio are controlled with a much better accuracy of typically 0.1% to 2%

- The sampling frequency can be realized with a **high accuracy** (better than 0.1%)

- In addition the cut-off frequency can be tuned by changing the sampling frequency

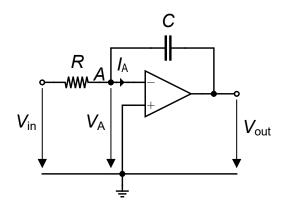

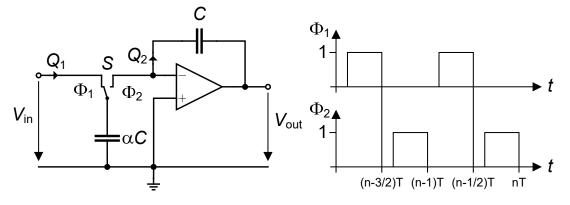

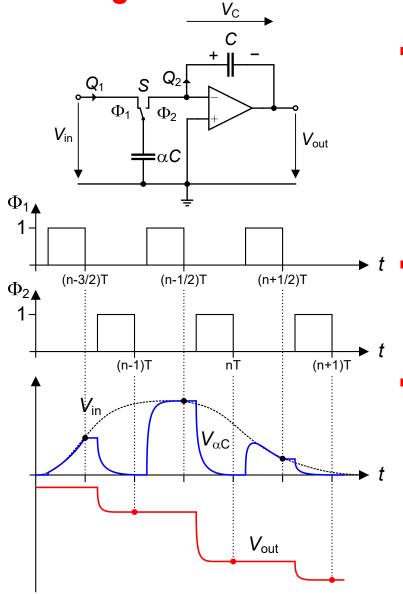

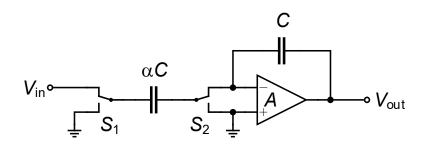

# **Basic SC Integrator**

$$V_{out}(t) = -\frac{1}{\tau} \cdot \int_{0}^{t} V_{in}(t')dt'$$

with  $\tau = RC$  and  $V_{in}(t = 0) = 0$

$$H_{RC}(s) = \frac{V_{out}(s)}{V_{in}(s)} = -\frac{1}{s \cdot \tau}$$

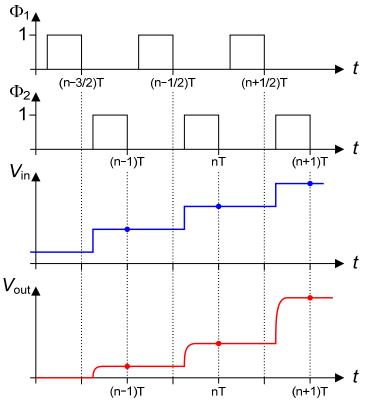

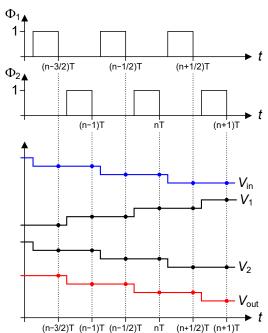

Two **non-overlapping** phases:

Phase  $\Phi_1$ : **precharge** of sampling capacitor  $\alpha C$  to the input voltage  $V_{in}(t)$  followed by

sampling and holding of  $V_{in}\left(\left(n-\frac{1}{2}\right)T\right)$

Phase  $\Phi_2$ : transfer of charge stored on  $\alpha C$  to integration capacitor CAccumulation of charges on C

# **SC Integrator Transfer Function**

• After charge  $Q_2$  is transferred, voltage  $V_C$  across the integrating capacitor C increases by  $\Delta V_C$

$$\Delta V_C(nT) = -\Delta V_{out}(nT) = \frac{Q_2}{C}$$

$$= \alpha \cdot \left[ V_{in} \left( \left( n - \frac{1}{2} \right) T \right) - 0 \right]$$

$$V_{out}(nT) - V_{out} \left( (n-1)T \right) = -\alpha \cdot V_{in} \left( \left( n - \frac{1}{2} \right) T \right)$$

which z-transform is given by

$$V_{out}(z) - z^{-1} \cdot V_{out}(z)$$

$$= -\alpha \cdot z^{-\frac{1}{2}} \cdot V_{in}(z)$$

The transfer function is then given by

$$H_{SC}(z) = \frac{V_{out}(z)}{V_{in}(z)} = -\alpha \cdot \frac{z^{-\frac{1}{2}}}{1 - z^{-1}}$$

$$= -\alpha \cdot \frac{z^{+\frac{1}{2}}}{z - 1}$$

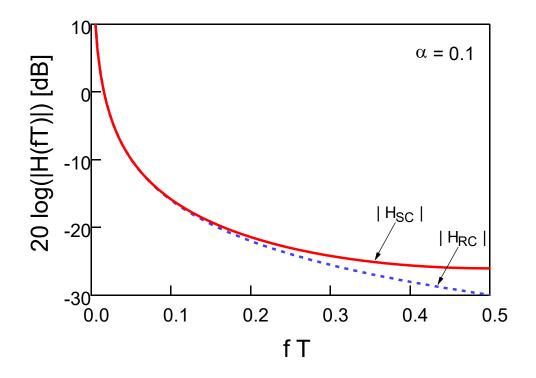

# **SC Integrator Transfer Function**

The transfer function (TF) of the SC integrator can be compared to that of the RC integrator having the following transfer function

$$H_{RC}(\omega) = -\frac{1}{j\omega\tau} = -\frac{1}{j\omega RC} = -\frac{\alpha}{j\omega T}$$

since  $\alpha = \frac{T}{RC} = \frac{T}{\tau}$

The TF of the SC integrator is obtained by replacing z by  $exp(j\omega T)$  resulting in

$$H_{SC}(\omega T) = -\alpha \cdot \frac{e^{+j\frac{\omega T}{2}}}{e^{j\omega T} - 1} = -\frac{\alpha}{e^{+j\frac{\omega T}{2}} - e^{-j\frac{\omega T}{2}}} = -\frac{\alpha}{j2 \sin(\omega T)}$$

• For  $\omega T\ll 1$ ,  $exp(j\omega T)\approx 1+j\omega T$  and the SC TF becomes identical to the TF of the RC integrator

$$H_{SC}(\omega T) \cong -\frac{\alpha}{j\omega T} = H_{RC}(\omega T) \text{ for } \omega T \ll 1$$

- The SC integrator is therefore equivalent to a continuous-time RC integrator only for frequencies much smaller than the sampling frequency (typically 100x smaller)

- This needs to be accounted for when synthesizing SC filters directly from RCactive continuous-time filters

# **SC Integrator Transfer Function**

$$H_{RC}(\omega) = -\frac{\alpha}{j\omega T}$$

$$H_{SC}(\omega T) = -\frac{\alpha}{j2\sin(\frac{\omega T}{2})} \cong -\frac{\alpha}{j\omega T} = H_{RC}(\omega T) \text{ for } \omega T \ll 1$$

Slide 10

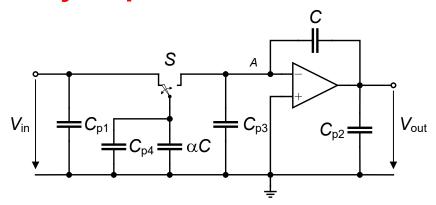

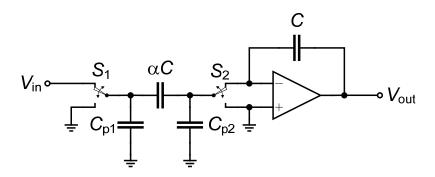

## **Sensitivity to Stray Capacitances**

- The charge transfer from the sampling capacitance  $\alpha C$  to the integration capacitance C may be affected by **parasitic capacitances**

- $C_{p1}$  and  $C_{p2}$  have **no effect** since they are connected to a **voltage source**

- $C_{p3}$  has **no effect** since it is connected to the **virtual ground** (as long as the amplifier has a sufficiently large gain and no offset)

- $C_{p4}$  is connected in parallel to the sampling capacitance  $\alpha C$  and induces an error on the capacitor ratio  $\alpha$ . To maintain an error on  $\alpha$  lower than 1% and assuming  $C_{p4} = 50 \mathrm{fF}$ ,  $\alpha C > 5 pF$  and typically C > 50 pF (assuming  $\alpha = 0.1$ ), which are very large values that result in large areas and prohibitive power consumption

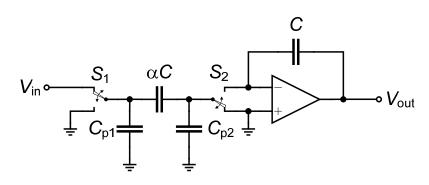

# **Stray-insensitive Integrators**

#### Inverting Integrator

$$H(z) = -\alpha \cdot \frac{1}{1 - z^{-1}}$$

#### Non-inverting Integrator

$$H(z) = \alpha \cdot \frac{z^{-\frac{1}{2}}}{1 - z^{-1}}$$

- To avoid the effect of parasitic capacitances, capacitances should not be switched between a voltage source and a virtual ground

- Capacitances should therefore be switched between two voltage sources or between a virtual ground and the ground

- $C_{p1}$  has no effect since it is charged during phase  $\Phi_1$  and discharged during  $\Phi_2$

- $C_{p2}$  has no effect neither since it is switched between virtual ground and ground

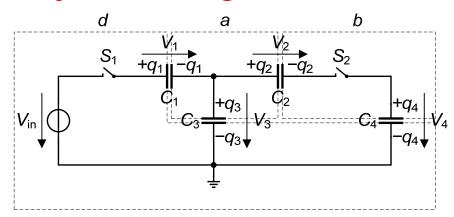

# SC Circuits Analysis – Charge Conservation

- Charges are stored on the capacitor electrodes

- These electrodes can be identified by the contours a, b and d in the above circuit

- The total charge within a contour is **conserved** between switching instants  $t_n$  and  $t_{n+1}$

- The charge distribution will change according to the initial and applied voltages

- Assuming linear capacitors, we then have

contour a:

$$-C_1V_1(t) + C_2V_2(t) + C_3V_3(t) = -C_1V_1(t_n^-) + C_2V_2(t_n^-) + C_3V_3(t_n^-)$$

contour b:  $-C_2V_2(t) + C_4V_4(t) = -C_2V_2(t_n^-) + C_4V_4(t_n^-)$

• where  $t_n^-$  denotes the instant before the switching instant  $t_n$

# SC Circuits Analysis – Charge Conservation

• Kirchhoff voltage laws give two additional equations that allow to write one of the voltages (say  $V_4$ ) as a function of the input voltage  $V_{in}(t)$  and the initial voltages

$$V_4(t) = \gamma \cdot V_{in}(t) + \beta_1 \cdot V_1(t_n^-) + \beta_2 \cdot V_2(t_n^-) + \beta_3 \cdot V_3(t_n^-) + \beta_4 \cdot V_4(t_n^-)$$

- where  $\gamma$  and  $\beta_i$  (i=1,2,3,4) are unitless coefficients that can be expressed in terms of  $C_i$

- Note that the charge conservation equations remain valid even in the presence of resistances as long as the voltage drop across those resistance (if any) are accounted for in the Kirchhoff voltage laws

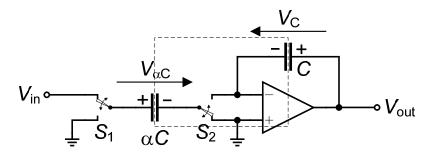

# **Integrator Analysis**

Positions of switches correspond to phase  $\Phi_1$

#### Basic assumptions for analysis:

- Ideal OPAMP (infinite gain and input impedance, no offset voltage)

- 2. Input comes from a similar integrator  $\rightarrow V_{in}(t)$  changes at the same instants than  $V_{out}(t)$  and is maintained constant during each period T

- 3. Transients during phase  $\Phi_2$  are much shorter than T

- 4. Capacitors are linear

# **Integrator Analysis**

- Apply charge conservation principle to the electrodes that are connected to the virtual ground of the OPAMP

- Total charge stored in the closed contour at the end of phase  $\Phi_2$  (instant nT) is equal to that at the end of phase  $\Phi_1$  (instant  $\left(n-\frac{1}{2}\right)T$ ) after all the transients have vanished

$$Q_A(nT) = Q_A\left(\left(n - \frac{1}{2}\right)T\right)$$

$$-\alpha C V_{\alpha C}(nT) - C V_C(nT) = -\alpha C V_{\alpha C}\left(\left(n - \frac{1}{2}\right)T\right) - C V_C\left(\left(n - \frac{1}{2}\right)T\right)$$

Infinite gain leads to

$$V_{\alpha C}(nT) = 0$$

and  $V_{C}(nT) = V_{out}(nT)$  and  $V_{C}\left(\left(n - \frac{1}{2}\right)T\right) = V_{out}\left(\left(n - \frac{1}{2}\right)T\right)$

• Voltages at instants  $(n - \frac{1}{2})T$  are equal to voltages at instant (n - 1)T

$$V_{\alpha C}\left(\left(n-\frac{1}{2}\right)T\right)=V_{in}\left(\left(n-\frac{1}{2}\right)T\right)=V_{in}\left(\left(n-1\right)T\right) \text{ and } V_{out}\left(\left(n-\frac{1}{2}\right)T\right)=V_{out}\left(\left(n-1\right)T\right)$$

- This leads to  $V_{out}(nT) = \alpha V_{in}((n-1)T) + V_{out}((n-1)T)$

- or in z-domain  $V_{out}(z) = \alpha z^{-1}V_{in}(z) + z^{-1}V_{out}(z)$

- and finally  $H(z) = \frac{V_{out}(z)}{V_{in}(z)} = \alpha \frac{z^{-1}}{1-z^{-1}} = \frac{\alpha}{z-1}$

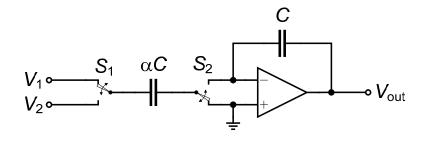

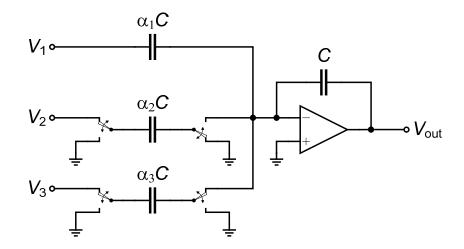

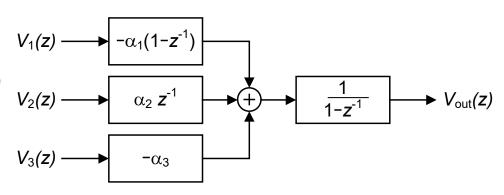

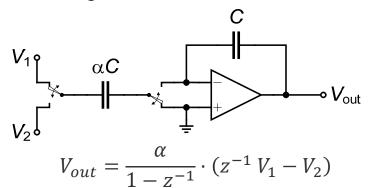

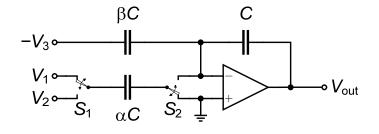

# **Summator-Integrator**

$$H(z) = \frac{\alpha}{1 - z^{-1}} \cdot \left[ z^{-\frac{1}{2}} \cdot V_1(z) - V_2(z) \right]$$

- The latter integrators can be combined to obtain a summator-integrators

- Those are the main building blocks used for building SC filters

$$V_{out}(z) = -\alpha_1 V_1(z) + \alpha_2 \frac{z^{-\frac{1}{2}}}{1 - z^{-1}} \cdot V_2(z) - \frac{\alpha_3}{1 - z^{-1}} \cdot V_3(z)$$

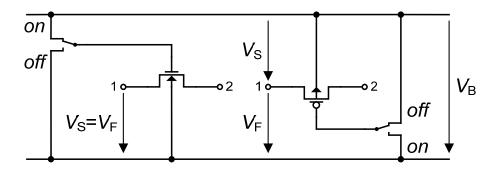

## **Switches Implementation**

- Switches are realized by MOS transistors: either N-channel or P-channel or both

- Switch conductance depends on the supply voltage  $V_B = V_{DD} V_{SS}$  and on floating voltage  $V_F$  (with  $V_F = V_S = V_D$  for n-channel)

- Switch conductance can be derived from the current expression in SI and linear region

$$I_D = \beta (V_D - V_S) [V_G - V_{T0} - \frac{n}{2} (V_D + V_S)]$$

• Hence

$$G_n = \frac{dI_D}{dV_{DS}}\Big|_{V_S = V_D = V_F} = \beta(V_G - V_{T0} - nV_F)$$

where  $\beta \triangleq \mu C_{ox} \frac{W}{L}$

Leading to

$$G_n = \beta_n (V_B - V_{T0n} - n_n V_F)$$

Similarly for p-channel

$$G_p = \beta_p \left( V_B - V_{T0p} - n_p (V_B - V_F) \right) = \beta_p \left( n_p V_F - (n_p - 1) V_B - V_{T0p} \right)$$

## **Conduction Gap at Low Supply Voltage**

$$G_n = \beta_n \cdot (V_B - V_{T0n} - n_n \cdot V_F)$$

$$G_p = \beta_p \cdot \left(n_p \cdot V_F - (n_p - 1)V_B - V_{T0p}\right)$$

$$G_n = \begin{cases} n_n \cdot \beta_n \cdot (V_{Fn} - V_F) & \text{for } V_F < V_{Fn} \\ 0 & \text{for } V_F \ge V_{Fn} \end{cases}$$

$$G_p = \begin{cases} n_p \cdot \beta_p \cdot \left(V_F - V_{Fp}\right) & \text{for } V_F > V_{Fp} \\ 0 & \text{for } V_F \le V_{Fp} \end{cases}$$

with  $V_{Fn} = \frac{V_B - V_{T0n}}{n_p}$  and  $V_{Fp} = \frac{(n_p - 1)V_B + V_{T0p}}{n_p}$

- If  $V_B$  becomes smaller than a critical value  $V_{Bcrit}$ , a conduction gap appears

- This critical value can be calculated by equating  $V_{Fn}$  and  $V_{Fp}$  resulting in

$$V_{Bcrit} = \frac{n_n V_{T0p} + n_p V_{T0n}}{n_n + n_p - n_n n_p} \cong \frac{V_{T0p} + V_{T0n}}{2 - n} \text{ for } n_n = n_p = n$$

• If  $V_B < V_{Bcrit}$  use other techniques such as on-chip clock voltage multiplier, low threshold voltages (watch leakage currents!), switched OPAMP or reset OTA

### **Outline**

- Introduction

- Basic principles

- Non-ideal effects in SC circuits

- The design of switched-capacitor filters (SCF)

### Non-ideal Effects in SC Circuits

- The operation of SC circuits are affected by several non-idealities

- Non-idealities coming from the OPAMPs or the OTAs

- Finite gain and/or bandwidth

- Slew-rate

- Offset and noise

- Non-idealities coming from the switches

- Finite on-resistance

- Charge-injection and clock feedthrough

- Noise

- Non-idealities coming from the capacitors

- Matching

- Non-linearity

Slide 21

### Non-ideal Effects – OPAMP Finite Gain

The transfer function of the integrator in the frequency domain is altered by the finite DC gain A of the OPAMP according to

$$H(\omega) \cong (1 + \varepsilon(\omega))e^{j\theta(\omega)} H_i(\omega) \text{ with } H_i(\omega) = -\alpha \frac{e^{j\frac{\omega T}{2}}}{j2\sin(\frac{\omega T}{2})}$$

• where  $H_i(\omega)$  is the ideal transfer function  $(A \to \infty)$  and the relative gain error  $\varepsilon(\omega)$  and relative phase error  $\theta(\omega)$  are given by

$$\varepsilon = -\frac{1+\alpha}{A}$$

and  $\theta(\omega) = \frac{\alpha}{2A \tan(\frac{\omega T}{2})} \cong \frac{\alpha}{A \omega T}$  for  $\omega T \ll 1$

### Non-ideal Effects – OPAMP Finite Gain

• It is useful to introduce the unity gain frequency  $\omega_u$  of the integrator defined as

$$|H_i(\omega_u)| = 1$$

We then have

$$\alpha = 2\sin\left(\frac{\omega_u T}{2}\right) \cong \omega_u T \ll 1$$

• The values of  $\varepsilon(\omega)$  and  $\theta(\omega)$  at  $\omega_u$  are then given by

$$\varepsilon(\omega_u) \cong -\frac{1}{A}$$

and  $\theta(\omega_u) \cong \frac{1}{A}$

- We see that the relative gain and phase error at the unity gain frequency are inversely proportional to the OPAMP dc gain

- It can be shown that the OPAMP finite dc gain introduces some losses

- The ideal integrator becomes a **lossy-integrator** with a pole given by  $\alpha/(A\ T)$  instead of 0

### Non-ideal Effects – OPAMP Finite Bandwidth

$$A(\omega) = \frac{A_0}{1 + \frac{j\omega}{\omega_p}} \cong \frac{\omega_t}{j\omega}$$

with  $\omega_t \triangleq A_0 \ \omega_p$

The transfer function of the integrator in the frequency domain is altered by the **finite gain-bandwidth**  $\omega_t$  of the OPAMP according to

$$\varepsilon(\omega) = -e^{k_1}(1 - k \cos(\omega T))$$

and  $\theta(\omega) = -e^{k_1} k \sin(\omega T)$

- with  $k = \frac{1}{1+\alpha} \cong 1$ ,  $k_1 = k \frac{\omega_t T}{2} \gg 1$

- Relative gain and phase error at the integrator unity gain  $\omega_u$ ,  $\varepsilon(\omega_u)$  and  $\theta(\omega_u)$  can then be approximated by

$$\varepsilon(\omega_u) \cong \theta(\omega_u) \cong -\omega_u T e^{-\frac{\omega_t T}{2}} \text{ for } \omega_u T \ll 1$$

- Error decreases exponentially with  $\omega_t T$  and is usually **negligible** for  $f_t T > 5$

- Same results apply for the non-inverting integrator

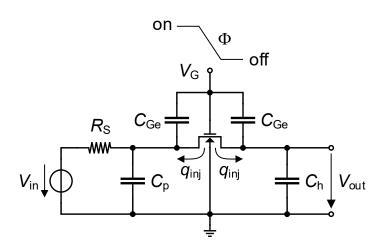

### Nonideal Effects in Switches

- The MOS switch nonidealities include a **nonzero** and **nonlinear** on-resistance

- However, the most important factors affecting residual offset are the following:

- clock feedthrough,

- channel charge injection,

- sampled noise and

- leakage current.

- The **total error** in the sampled voltage across the hold capacitor  $C_h$  due to clock feedthrough, charge injection, sampled noise and leakage current is given by

$$\Delta V = \alpha \cdot \frac{C_{Ge}}{C_{Ge} + C_h} \cdot V_{swing} + \frac{q_{inj}}{C_h} + \sqrt{\frac{kT}{C_h}} + \frac{I_{leak} \cdot T_h}{C_h}$$

- Where  $V_{swing}$  is the swing of the clock signal and  $I_{leak}$  the leakage current of the drain-to-bulk diodes at the operating temperature. The attenuation factor  $\alpha$  accounts for the part of the total charge  $C_{Ge} \cdot V_{swing}$  coming from the overlap and fringing capacitors and flowing to ground instead of the hold capacitor

- All contributions **decrease** if a **larger hold capacitor** is used

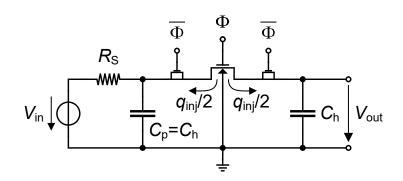

# **Techniques to Reduce Charge Injection**

- The simplest technique uses complementary switches in such a way that the charges released by one switch are absorbed by the complementary device building its channel. This technique is rather inefficient, since the matching between the channel charges of the n-MOS and the p-MOS devices is poor and signal dependent. This charge mismatch is further degraded by phase jitter between the two complementary clocks

- Other more efficient strategies are described below

- It should be noted that none of the techniques described below offers a perfect charge-injection cancellation

- The efficiency of the half-sized dummy transistor technique depends on a proper layout in order to insure a good matching and a first-order insensitivity to doping gradient

- The technique which usually offers the best results is a combination of a fully differential structure and the half-sized dummy transistor technique

E K V

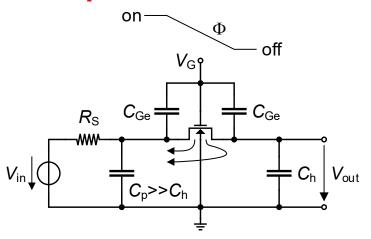

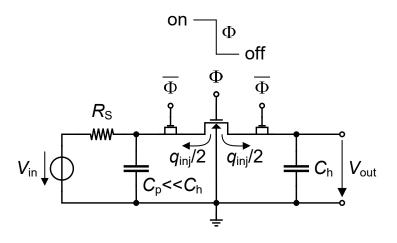

# **Techniques to Reduce Charge Injection**

- Making C<sub>p</sub> much larger than C<sub>h</sub> (by adding an extra capacitor) and choosing a slow clock transition in order to attract most of the channel charge to C<sub>p</sub>, reducing q<sub>inj</sub> almost to zero

- This technique of course sets a limit on the maximum clock frequency

- The charge flow due to the extrinsic capacitance  $C_{Ge}$  is still present

- Making  $C_p$  equal to  $C_h$  to force the channel charge to split equally between source and drain independently of the gate voltage switching rate.

- Then compensating the injected charge by adding half-size dummy switches controlled by opposite phase

Slide 27

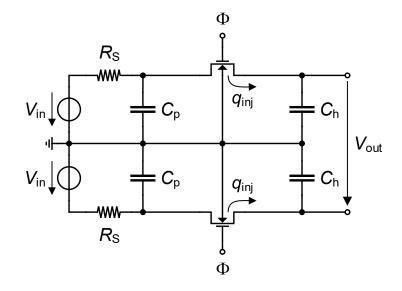

## **Techniques to Reduce Charge Injection**

- Using a very **short transition time** to force the channel charge to split equally between source and drain independently of the  $C_h/C_p$  ratio

- Then compensating the injected charge by half-sized dummy switches

- Using a fully differential structure, if the charges injected to the differential capacitors  $C_h$  are matched, the resulting voltage appears as a common-mode voltage and is therefore rejected

- This technique usually requires the generation of delayed-cutoff clock phases

### **Outline**

- Introduction

- Basic principles

- Non-ideal effects in SC circuits

- The design of switched-capacitor filters (SCF)

# **Design of Sampled-data Filters**

- For high selective filters usually IIR transfer functions are required in order to implement poles near the cut-off frequencies

- For IIR filter the z-domain transfer function H(z) is a rational function

$$H(z) = \frac{N(z)}{D(z)} = \frac{a_N z^N + a_{N-1} z^{N-1} + \dots + a_1 z + a_0}{b_M z^M + b_{M-1} z^{M-1} + \dots + b_1 z + b_0}$$

having some poles at finite and nonzero frequencies

- Usually H(z) is not found directly, but derived from **continuous-time transfer** functions  $H_a(s_a)$  using transformations or circuit equivalence (subscript "a" stands for analog actually meaning continuous-time)

- H(z) is obtained by replacing  $s_a$  by some transformation function F in  $H_a$

$$H(z) = H_a(s_a) \Big|_{s_a = F(z)} = H_a(F(z))$$

There are many continuous-time (CT) to discrete-time (DT) transformation rules, but the one that are the most often used in SCF designs are the bilinear and the lossless discrete integrator (LDI) transforms

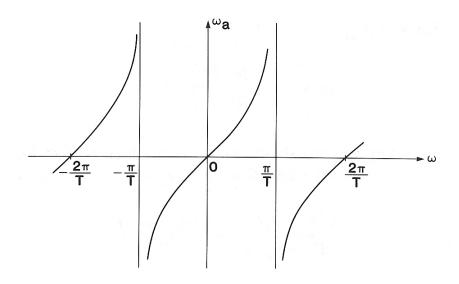

### CT to DT Transformations – The Bilinear Transform

The bilinear transform is defined by

$$s_a = F(z) = \frac{2}{T} \frac{z-1}{z+1} \text{ or } z = F^{-1}(s_a) = \frac{1 + \frac{S_a T}{2}}{1 - \frac{S_a T}{2}}$$

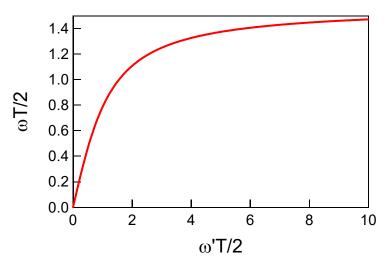

• Replacing  $z=e^{j\omega T}$  and  $s_a=j\omega_a$  leads to

$$\frac{\omega_a T}{2} = \tan\left(\frac{\omega T}{2}\right) \text{ or } \frac{\omega T}{2} = \tan^{-1}\left(\frac{\omega_a T}{2}\right)$$

# **Exact Design of SC Filters**

All exact design methods are based on the bilinear transformation

$$s \iff \frac{2}{T} \cdot \frac{z-1}{z+1} \text{ or } z \iff \frac{1+\frac{ST}{2}}{1-\frac{ST}{2}}$$

■ Maps ωT = 0 to ω'T = 0 and ωT = π (half the clock frequency) to +∞

$$\Omega = \frac{\omega' T}{2} \iff \tan\left(\frac{\omega T}{2}\right) \text{ or } \frac{\omega T}{2} \iff \arctan\left(\frac{\omega' T}{2}\right)$$

- Attenuation specifications versus  $\omega$  are prewarped versus  $\omega'$

- Results in modifying the critical frequencies along the horizontal axis without affecting the attenuation on the vertical axis

- Synthesis is done in the normalized frequency  $\Omega = \omega' T/2$  using conventional methods

### CT to DT Transformations – The Bilinear Transform

- 1. Specifications of sampled-data filter established

- passband and stopband limits ( $\omega_p$  and  $\omega_s$ )

- $|H(e^{j\omega T})|$  passband ripple in dB  $(A_p)$

- $|H(e^{j\omega T})|$  stopband minimum loss in dB  $(A_s)$

- eventual phase, delay or transient response requirements

- **2. Frequency pre-warping** by replacing  $\omega_p$  and  $\omega_s$  by  $\omega_{ap}$  and  $\omega_{as}$  in the prototype filter keeping the same loss limits  $A_p$  and  $A_s$

$$\omega_{ap} = \frac{2}{T} \tan\left(\frac{\omega_p T}{2}\right)$$

and  $\omega_{as} = \frac{2}{T} \tan\left(\frac{\omega_s T}{2}\right)$

- 3. Find suitable CT transfer function  $H_a(\omega_a)$  such that the pre-warped specs  $\omega_{ap}$ ,  $\omega_{as}$ ,  $A_p$  and  $A_s$  are satisfied using conventional methods

- 4. Calculate H(z) by replacing variable  $s_a$  in  $H_a(s_a)$  by

$$s_a = F(z) = \frac{2}{T} \frac{z - 1}{z + 1}$$

# Main SC Filter Synthesis Approaches – Cascade Design

- Objective: synthesize a SC filter that has the desired continuous-time transfer function  $H_a(s)$

- Cascade Design requires biquadratic and first-order sections

- Resistance substitution method

- Start directly from the continuous-time transfer function and derive an RC-active implementation

- Replace resistors by switched-capacitors (approximate design)

- Exact design method

- Derive the exact transfer function directly in the z-domain by using a proper transformation (for example bilinear transform)

- Start by pairing poles and zeroes which will affect both noise performance and total capacitance

- Order sections

- Scale for optimum dynamic range

# **Biquadratic Cell**

The continuous-time biquad transfer function is given by

$$H_a(s) = K \frac{s^2 + \omega_z^2}{s^2 + \frac{\omega_p}{Q_p} s + \omega_p^2}$$

- which has **4 parameters**, namely K,  $\omega_p$ ,  $Q_p$  and  $\omega_z$

- The sampled-data biquad transfer can be obtained from the bilinear transform  $s \leftrightarrow \frac{2}{T} \frac{z-1}{z+1}$  results in

$$H(z) = K' \frac{z^2 - 2\cos\theta_z \ z + 1}{z^2 - 2R_p \cos\theta_p \ z + R_p^2}$$

The poles and zeroes of H(z) are given by

$$p_0, p_0^* = R_p e^{\pm j\theta_p}$$

and  $z_0, z_0^* = e^{\pm j\theta_z}$

By identification we have

$$K' = K \frac{1 + \Omega_z^2}{1 + \Omega_p/Q_p + \Omega_p^2}, \cos \theta_z = \frac{1 - \Omega_z^2}{1 + \Omega_z^2}, R_p \cos \theta_p = \frac{1 - \Omega_p^2}{1 + \Omega_p/Q_p + \Omega_p^2}, R_p^2 = \frac{1 - \Omega_p/Q_p + \Omega_p^2}{1 + \Omega_p/Q_p + \Omega_p^2}$$

• with  $\Omega_z = \frac{\omega_z T}{2}$  and  $\Omega_p = \frac{\omega_p T}{2}$

© C. Enz | 2024

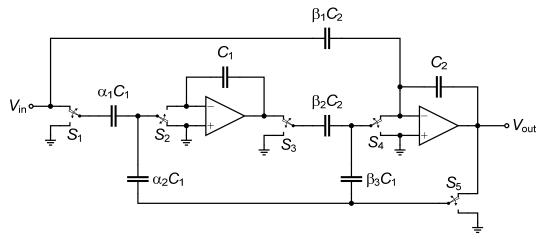

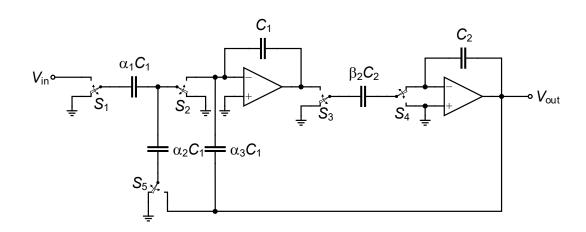

## Biquadratic Cell for Low to Medium Q

Transfer function given by

$$H(z) = -\beta_1 \frac{z^2 - \left(2 - \frac{\alpha_1 \beta_2}{\beta_1}\right)z + 1}{(1 + \beta_3)z^2 - (2 - \alpha_2 \beta_2 + \beta_3)z + 1}$$

• Approximate design equations valid for  $\omega_z T \ll 1$  and  $\omega_p T \ll 1$

$$\alpha_1 \cong K \frac{\omega_z^2 T}{\omega_p}, \beta_1 \cong K, \alpha_2 = \beta_2 \cong \omega_p T, \beta_3 \cong \frac{\omega_p T}{Q_p}$$

• For  $Q_p>1$  the capacitance spread increases proportionally to  $Q_p$ , hence this biquad is better suited to low-Q designs  $(Q_p<1)$

F. Krummenacher, "Micropower Switched Capacitor Biquadratic Cell," JSSC, June 1982.

#### **Case without Finite Transmission Zeros**

■ In the case of LP filters without finite transmission zero, the 2<sup>nd</sup>-order continuoustime function becomes

$$H_a(s) = K' \frac{\omega_0^2}{s^2 + \frac{\omega_0}{Q}s + \omega_0^2}$$

- We can obtain an approximation of CT equivalent transfer function from the z-transfer by replacing z by 1+sT

- The design equations are then obtained by mapping the coefficients

# Biquadratic Cell for Low Q (no finite transmission zeros)

• For LP design without finite transmission zeros, capacitance  $\beta_1 C_2$  can be removed ( $\beta_1 = 0$ ) (the transmission zero is then at infinite frequency) and the transfer function then becomes

$$H(z) = -\frac{\alpha_1 \beta_2 z}{(1 + \beta_3)z^2 - (2 - \alpha_2 \beta_2 + \beta_3)z + 1}$$

- Approximate design equations valid for  $\omega_p T \ll 1$  then become

$$\alpha_1 \cong K' \omega_0 T$$

,  $\alpha_2 = \beta_2 \cong \omega_0 T$  and  $\beta_3 \cong \frac{\omega_0 T}{Q}$

• For a unity dc gain K'=1 then  $\alpha_1=\alpha_2=\beta_2\cong\omega_0T$

F. Krummenacher, "Micropower Switched Capacitor Biquadratic Cell," JSSC, June 1982.

© C. Enz | 2022

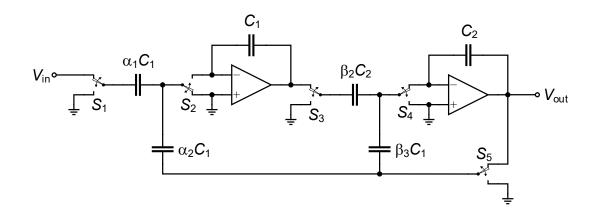

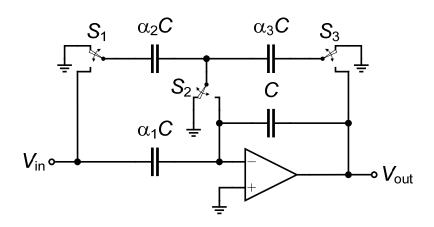

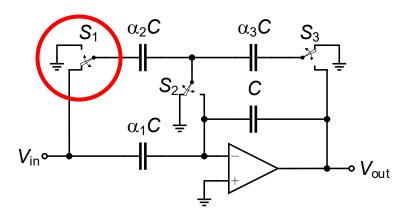

# Biquadratic Cell for High Q

Transfer function given by

$$H(z) = -\beta_1 \frac{z^2 - \left(2 - \frac{\alpha_1 \beta_2}{\beta_1}\right)z + 1}{z^2 - \left(2 - (\alpha_2 + \alpha_3)\beta_2\right)z + 1 - \alpha_3 \beta_2}$$

- Approximate design equations valid for  $\omega_z T \ll 1$  and  $\omega_p T \ll 1$

$$\alpha_1 \cong K \frac{\omega_z^2 T}{\omega_p}, \, \alpha_2 \cong \omega_p T, \, \alpha_3 \cong \frac{1}{Q_p}, \, \beta_1 \cong -K, \, \beta_2 \cong \omega_p T$$

• For  $Q_p \ge 1$  the capacitance spread is bounded by  $1/(\omega_p T)$ , hence this biquad is better suited to high-Q designs  $(Q_p \ge 1)$

F. Krummenacher, "Micropower Switched Capacitor Biquadratic Cell," JSSC, June 1982.

## Biquadratic Cell for High Q (no finite transmission zeros)

• Similarly, for designs without finite transmission zeros, capacitance  $\beta_1 C_2$  can be removed ( $\beta_1 = 0$ ) (the transmission zero is then at infinite frequency) and the transfer function then becomes

$$H(z) = -\frac{\alpha_1 \beta_2 z}{z^2 - (2 - (\alpha_2 + \alpha_3)\beta_2)z + 1 - \alpha_3 \beta_2}$$

• The approximate design equations valid for  $\omega_0 T \ll 1$  simplify to

$$\alpha_1 \cong K' \omega_0 T$$

,  $\alpha_2 \cong \omega_0 T$ ,  $\alpha_3 \cong \frac{1}{Q}$ ,  $\beta_2 \cong \omega_0 T$

• For a unity dc gain K'=1 then  $\alpha_1=\alpha_2=\beta_2\cong\omega_0T$

F. Krummenacher, "Micropower Switched Capacitor Biquadratic Cell," JSSC, June 1982.

### First-order Section (zero inside the unit circle)

The z-transfer function is given by

$$H(z) = -\frac{(\alpha_1 + \alpha_2)z - \alpha_1}{(1 + \alpha_3)z - 1}$$

• Approximate CT transfer function  $z \cong 1 + sT$

$$H_a(s) = -K \cdot \frac{1 + s/\omega_z}{1 + s/\omega_p}$$

• Approximate synthesis equations valid for  $\omega_z T \ll 1$  and  $\omega_p T \ll 1$

$$\alpha_1 \cong K$$

,  $\alpha_2 \cong K\omega_z T$ ,  $\alpha_3 \cong \omega_p T$

### First-order Section (zero outside the unit circle)

The z-transfer function is given by

$$H(z) = -\frac{\alpha_1 z - (\alpha_1 + \alpha_2)}{(1 + \alpha_3)z - 1}$$

• Approximate CT transfer function  $z \cong 1 + sT$

$$H_a(s) = K \cdot \frac{1 - s/\omega_z}{1 + s/\omega_p}$$

- Approximate synthesis equations valid for  $\omega_z T \ll 1$  and  $\omega_p T \ll 1$

$$\alpha_1 \cong K \frac{\omega_p T}{\omega_z T}, \, \alpha_2 \cong K \omega_p T, \, \alpha_3 \cong \omega_p T$$

© C. Enz | 2022

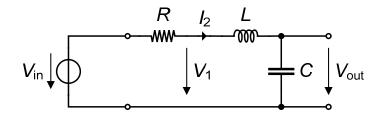

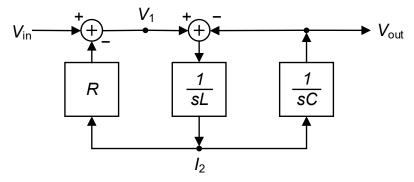

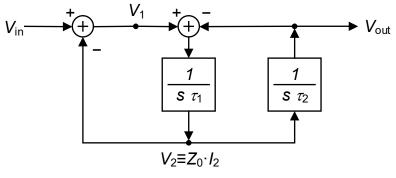

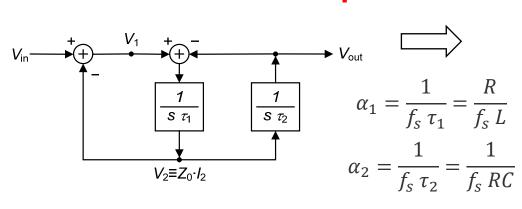

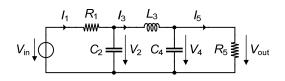

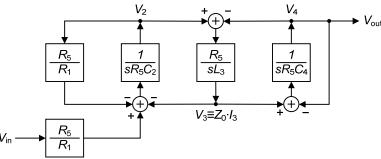

# Main SC Filter Synthesis Approaches – Ladder Filters

- Starting from LC ladder prototype taking advantage of their low sensitivity to component variation in the passband

- Direct simulation of LC ladders (impedance simulation method)

- Derive an active RC implementation and replace resistors with switched capacitors

- Not widely used due to sensitivity to parasitic capacitances

- Indirect simulation of LC ladders (operational simulation method, leapfrog filters)

- Approximate design by deriving the signal-flow graph and replacing integrators with SC integrators

- Can make an exact design by using the bilinear transform

Normalization with  $Z_0 = R$

$$au_1 = rac{L}{R}$$

and  $au_2 = RC$

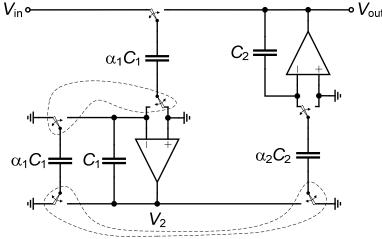

SC integrator-summator:

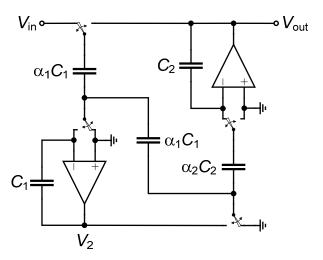

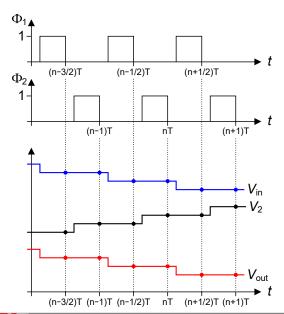

To minimize the effect of delays, phasing of the switches have to be alternated as shown: charge transfer into  $C_2$  occurs during phase 1 (sketched position of switches) and charge transfer into  $C_1$  occurs at the end of phase  $\Phi_2$

This also minimizes the OPAMP speed requirement since the OPAMP output is not loaded by the sampled capacitor of the other integrator during charge transfer (if not alternated the two integrator are connected in a loop)

regroup switches to obtain a structure with minimum number of switches

Positions of switches correspond to phase  $\Phi_1$

Writing the charge conservation equations for both integrators leads to

$$\begin{split} &-C_1 V_2(n) - \alpha_1 C_1 V_{out}(n) - \alpha_1 C_1 V_2(n) = -C_1 V_2(n - \frac{1}{2}) - \alpha_1 C_1 V_{in}(n - \frac{1}{2}) \\ &- C_2 V_{out}(n + \frac{1}{2}) = -C_2 V_{out}(n) - \alpha_2 C_2 V_2(n) \end{split}$$

with

$$V_2(n-\frac{1}{2}) = V_2(n-1)$$

$V_{in}(n-\frac{1}{2}) = V_{in}(n)$   $V_{out}(n+\frac{1}{2}) = V_{out}(n+1)$

reduces to

$$V_2(n) + \alpha_1 V_{out}(n) + \alpha_1 V_2(n) = V_2(n-1) + \alpha_1 V_{in}(n)$$

$$V_{out}(n+1) = V_{out}(n) + \alpha_2 V_2(n)$$

and after z - transform

$$(1 + \alpha_1)V_2(z) + \alpha_1 V_{out}(z) = z^{-1}V_2(z) + \alpha_1 V_{in}(z)$$

$$zV_{out}(z) = V_{out}(z) + \alpha_2 V_2(z)$$

Gives the following z-transfer function:

$$H(z) = \frac{a_1 z}{b_2 z^2 + b_1 z + b_0}$$

$$a_1 = \alpha_1 \alpha_2$$

$$b_0 = 1$$

$$b_1 = \alpha_1 \alpha_2 - \alpha_1 - 2$$

$$b_2 = \alpha_1 + 1$$

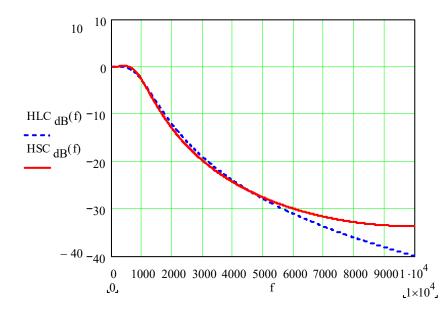

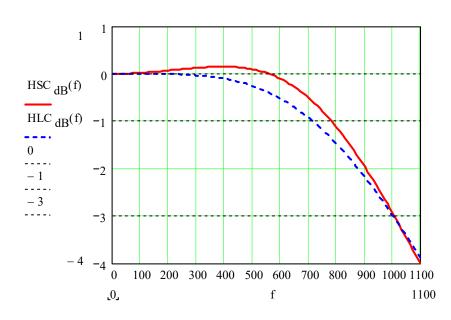

- Butterworth approximation for -3dB  $f_c$ =1kHz gives R=1 $\Omega$ , L=112.4 $\mu$ H, C=224.8 $\mu$ F

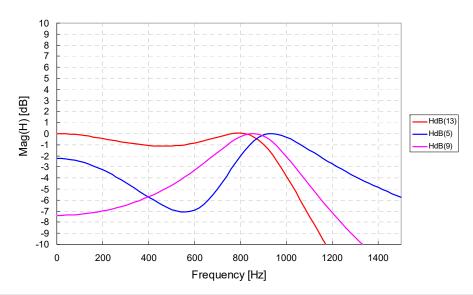

- $\tau_1$ =112.4µs and  $\tau_2$ =224.8µs

- $f_s$ =20kHz gives  $\alpha_1$ =0.445 and  $\alpha_2$ =0.222

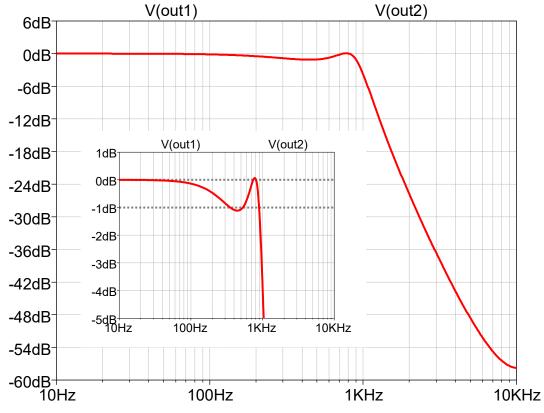

- Comparison with continuous-time LC transfer function (dashed line)

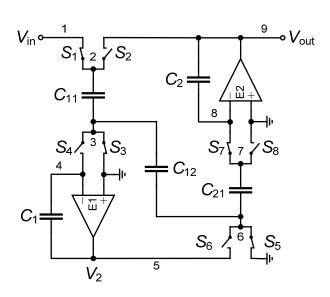

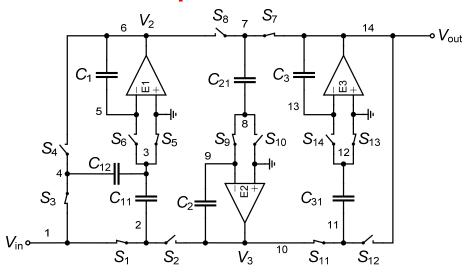

#### **Ladder Filters – Example: 2<sup>nd</sup>-order Low-Pass Switcap Simulations**

#### **SWITCAP NETLIST**

TITLE: 2ND ORDER LP BUTTERWORTH FILTER

OPTIONS; CHKCLK;

REPORT:

END;

TIMING: PERIOD 50E-6;

CLOCK CLK 1 (0 3/8);

END:

CIRCUIT;

S1 (1 2) CLK;

S2 (2 9) #CLK; S3 (3 0) CLK;

S4 (3 4) #CLK;

S5 (6 0) CLK;

S6 (6 5) #CLK;

S7 (7 8) CLK;

S8 (7 0) #CLK;

C11 (2 3) 0.445;

C12 (3 6) 0.445;

C1 (4 5) 1;

C21 (6 7) 0.222; C2 (8 9) 1;

E1 (5 0 0 4) 10000;

E2 (9 0 0 8) 10000;

V1 (1 0);

END:

ANALYZE SSS:

INFREQ 0 10000 LIN 501;

SET V1 AC 1.0 0.0; PRINT VDB(9) VP(9);

PLOT VDB(9);

END;

END;

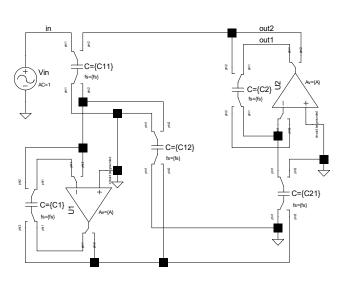

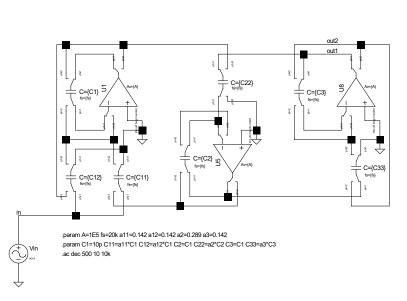

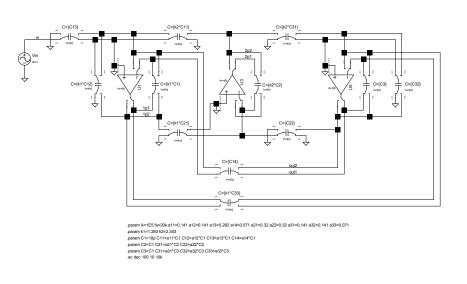

#### **Ladder Filters – Example: 2<sup>nd</sup>-order LP LTSpice Simulations**

- Despite being a linear time-variant circuit, this two-phases SC filter can be simulated by LTSpice using the special components shown in the schematic below

- The simulation basically simulates the two different circuits of phase  $\Phi_1$  and  $\Phi_2$  concurrently and ensures the charge conservation between the two phases

.param A=1E5\_fs=20k a1=0.445 a2=0.222 C1=10p C2=C1 C11=a1\*C1 C12=a1\*C1 C21=a2\*C1

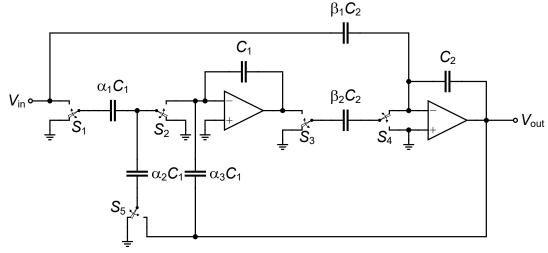

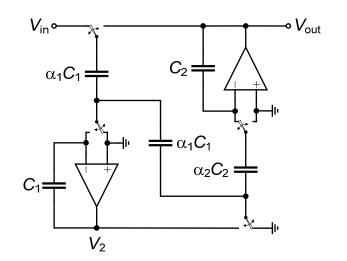

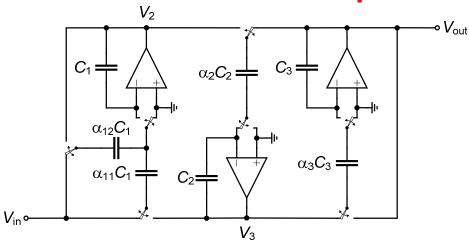

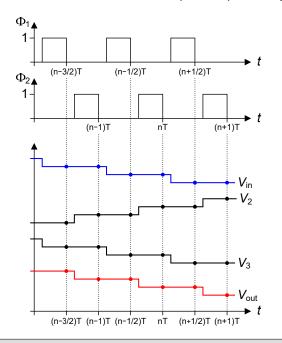

### **Ladder Filters – Example: 3<sup>rd</sup>-order Low-Pass**

To minimize the effect of delays, phasing of the switches have to be alternated as shown: charge transfer into  $C_2$  occurs during phase  $\Phi_1$  (sketched position of switches) and charge transfer into  $C_1$  occurs at the end of phase  $\Phi_2$

This also minimizes the OPAMP speed requirement since the OPAMP output is not loaded by the sampled capacitor of the other integrator during charge transfer (if not alternated the two integrator are connected in a loop)

Positions of switches correspond to phase  $\Phi_1$

Positions of switches correspond to phase  $\Phi_1$

$$1 - C_1 V_2(n) - \alpha_{11} C_1 V_3(n) - \alpha_{12} C_1 V_2(n) = -C_1 V_2(n - \frac{1}{2}) - \alpha_{11} C_1 V_{in}(n - \frac{1}{2}) - \alpha_{12} C_1 V_{in}(n - \frac{1}{2})$$

2

$$-C_2V_3(n+\frac{1}{2}) - \alpha_2C_2V_{out}(n+\frac{1}{2}) = -C_2V_3(n) - \alpha_2C_2V_2(n)$$

$$3 - C_3 V_{out}(n) - \alpha_3 C_3 V_{out}(n) = -C_3 V_{out}(n - \frac{1}{2}) - \alpha_3 C_3 V_3(n - \frac{1}{2})$$

$$\begin{split} &V_2(n-\frac{1}{2})=V_2(n-1) & V_{in}(n-\frac{1}{2})=V_{in}(n) \\ &V_3(n+\frac{1}{2})=V_3(n+1) & V_{out}(n+\frac{1}{2})=V_{out}(n) \\ &V_{out}(n-\frac{1}{2})=V_{out}(n-1) & V_3(n-\frac{1}{2})=V_3(n) \end{split}$$

1

$$V_2(n) + \alpha_{11}V_3(n) + \alpha_{12}V_2(n) = V_2(n-1) + (\alpha_{11} + \alpha_{12})V_{in}(n)$$

2

$$V_3(n+1) + \alpha_2 V_{out}(n) = V_3(n) + \alpha_2 V_2(n)$$

3

$$(1+\alpha_3)V_{out}(n) = V_{out}(n-1) + \alpha_3V_3(n)$$

1

$$V_2(z) + \alpha_{11}V_3(z) + \alpha_{12}V_2(z) = z^{-1}V_2(z) + (\alpha_{11} + \alpha_{12})V_{in}(z)$$

2

$$zV_3(z) + \alpha_2 V_{out}(z) = V_3(z) + \alpha_2 V_2(z)$$

3

$$(1+\alpha_3)V_{out}(z) = z^{-1}V_{out}(z) + \alpha_3V_3(z)$$

$$H(z) = \frac{a_2 z^2}{b_3 z^3 + b_2 z^2 + b_1 z + b_0}$$

$$a_2 = (\alpha_{11} + \alpha_{12})\alpha_2 \alpha_3$$

$$b_0 = -1$$

$$b_1 = 3 + \alpha_{12} - \alpha_{11}\alpha_2 + \alpha_3 - \alpha_2 \alpha_3$$

$$b_2 = -3 - 2\alpha_{12} + \alpha_{11}\alpha_2 - 2\alpha_3 - \alpha_{12}\alpha_3 + \alpha_2 \alpha_3 + \alpha_{11}\alpha_2 \alpha_3 + \alpha_{12}\alpha_2 \alpha_3$$

$$b_3 = (1 + \alpha_{12})(1 + \alpha_3)$$

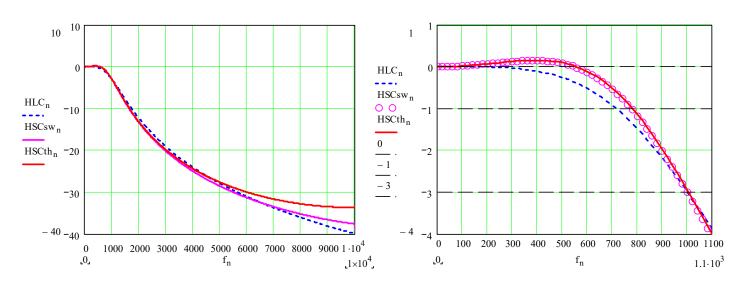

# **Ladder Filters – Example: 3<sup>rd</sup>-order Low-Pass**

1dB ripple Chebyshev approximation with f<sub>c</sub>=1kHz

$$f_S := 20kHz$$

$T := \frac{1}{f_-}$

$T = 50 \mu s$

$$f_c := 1 \cdot kHz$$

$$\tau_{11} := R_5 \cdot C_2$$

$$\tau_{11} = 352.5 \mu s$$

$$R_1 := 1 \cdot \Omega$$

$$\tau_{12} := R_1 \cdot C_2$$

$$\tau_{12} = 352.5 \mu s$$

$$C_2 := 352.5 \,\mu\text{F}$$

$$L_3 := 173.2 \,\mu\text{H}$$

$$\tau_2 := \frac{L_3}{R_5}$$

$$\tau_2 = 173.2 \mu s$$

$$C_4 := 352.5 \,\mu\text{F}$$

$$\tau_3 := R_5 \cdot C_4$$

$$\tau_3 = 352.5 \mu s$$

$$\tau_3 = 352.$$

$$\alpha_{11} \coloneqq \frac{1}{f_s \cdot \tau_{11}}$$

$$\alpha_{11} = 0.142$$

$$\alpha_{12} \coloneqq \frac{1}{f_s \cdot \tau_{12}}$$

$$\alpha_{12} = 0.142$$

$$\alpha_2 := \frac{1}{f_s \cdot \tau_2}$$

$$\alpha_2 = 0.289$$

$$R_5 := 1{\cdot}\Omega$$

$$\alpha_3 := \frac{1}{f_s \cdot \tau_3}$$

$$\alpha_3 = 0.142$$

#### **Ladder Filters – Example: 3rd-order LP Switcap Simulations**

#### **SWITCAP NETLIST**

TITLE: 3RD ORDER LP CHEBYSCHEV FILTER

OPTIONS; CHKCLK;

REPORT; END;

TIMING;

PERIOD 50E-6; CLOCK CLK 1 (0 3/8);

END;

CIRCUIT;

S1 (1 2) CLK; S2 (2 10) #CLK;

S3 (1 4) CLK;

S4 (4 6) #CLK;

S5 (3 0) CLK;

S6 (3 5) #CLK; S7 (7 14) CLK;

S8 (6 7) #CLK;

S9 (8 9) CLK;

S10 (8 0) #CLK;

10 (0 0) #CLN,

S11 (10 11) CLK;

S12 (11 14) #CLK;

S13 (12 0) CLK;

S14 (12 13) #CLK;

C11 (23) 0.142;

C12 (3 4) 0.142;

C1 (5 6) 1;

C21 (7 8) 0.289;

521 (1 0) 0.200

C2 (9 10) 1;

C31 (11 12) 0.142;

C3 (13 14) 1;

E1 (6 0 0 5) 10000;

E2 (10 0 0 9) 10000;

E3 (14 0 0 13) 10000;

44 (4 0)

V1 (1 0);

END;

ANALYZE SSS; INFREQ 0 10000 LIN 501;

SET V1 AC 1.0 0.0;

PRINT VDB(14) VP(14);

PLOT VDB(14); END;

END;

E K V

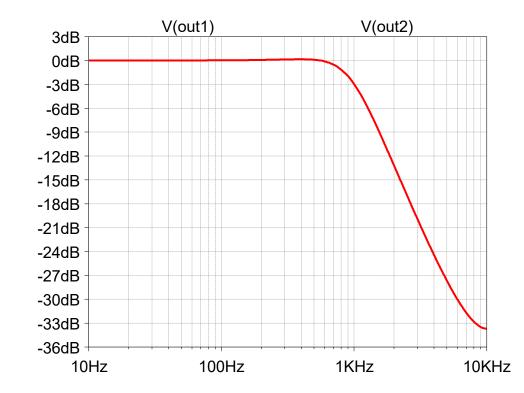

#### **Ladder Filters – Example: 3rd-order LP LTSpice Simulations**

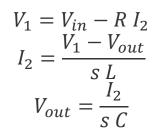

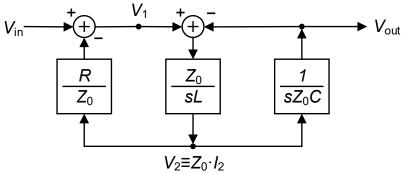

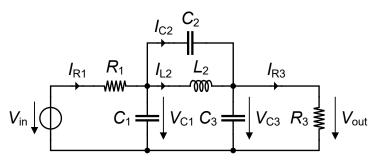

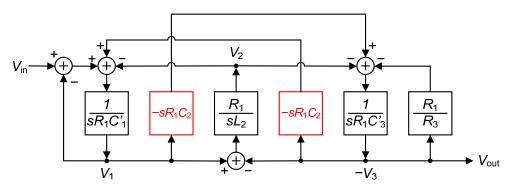

# Ladder Filters – Implementing Transmission Zeroes

$$I_{R1} = \frac{V_{in} - V_{C1}}{R_1}$$

Let

$$V_1 \square V_{C1}$$

$$V_{C1} = \frac{I_{R1} - I_{L2} - I_{C2}}{sC_1}$$

$$V_2 \square R_1 \cdot I_{L2}$$

$$V_3 \square V_{C3} = V_3$$

$$I_{C2} = (V_{C1} - V_{C3}) \cdot sC_2$$

$$I_{L2} = \frac{V_{C1} - V_{C3}}{sL_2}$$

$$V_{C3} = \frac{I_{L2} + I_{C2} - I_{R3}}{sC_3}$$

$$I_{R3} = \frac{V_{C3}}{R_2}$$

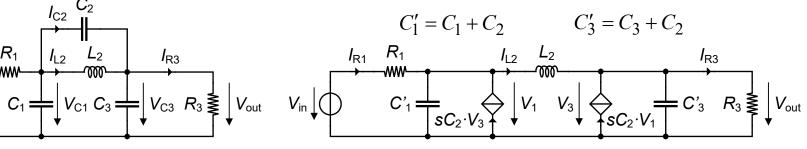

Let

$$V_1 \square V_{C1}$$

$$V_2 \square R_1 \cdot I_{L2}$$

$$V_3 \square V_{C3} = V_{out}$$

$$V_{1} = \frac{1}{sR_{1}C_{1}'} (V_{in} - V_{1} - V_{2}) + \frac{C_{2}}{C_{1}'} V_{3} = \frac{1}{sR_{1}C_{1}'} (V_{in} - V_{1} - V_{2} + sR_{1}C_{2}V_{3})$$

$$V_{2} = \frac{R_{1}}{sL_{2}} (V_{1} - V_{3})$$

$$V_3 = \frac{1}{sR_1C_3'} \left( V_2 - \frac{R_1}{R_3} V_3 \right) + \frac{C_2}{C_3'} V_1 = \frac{1}{sR_1C_3'} \left( V_2 - \frac{R_1}{R_3} V_3 + sR_1C_2 V_1 \right)$$

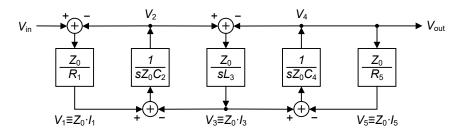

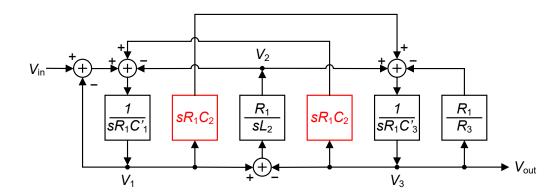

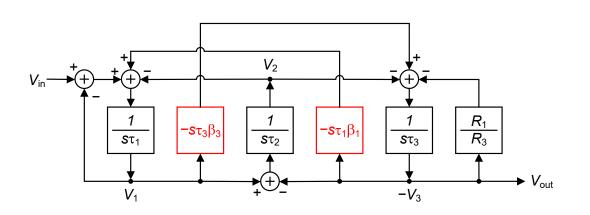

# **Ladder Filters – Implementing Transmission Zeroes**

$$V_{out} = \frac{\alpha}{1 - z^{-1}} (z^{-1} V_1 - V_2) + \beta V_3$$

$$\tau_1 = R_1 C_1'$$

$$\tau_2 = \frac{L_2}{R_1}$$

$$\tau_3 = R_1 C_3'$$

$$\beta_1 = \frac{C_2}{C_1'}$$

$$\beta_3 = \frac{C_2}{C_2'}$$

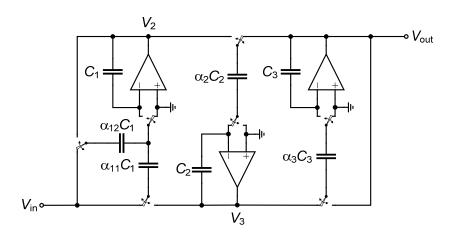

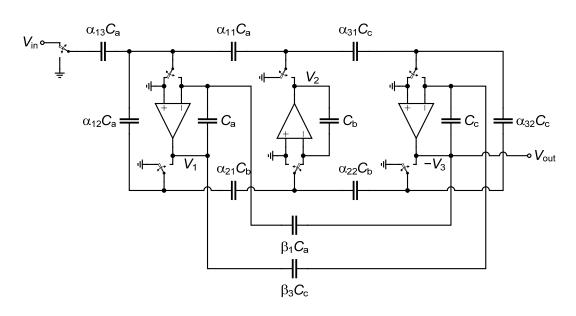

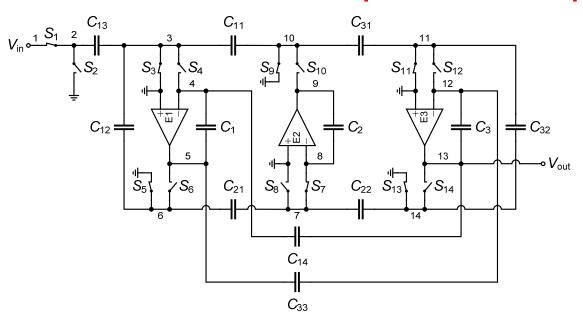

# **Ladder Filters – 3<sup>rd</sup>-order Elliptic Filter**

$$\alpha_{11} = \frac{1}{f_c \tau_1} = \frac{1}{f_c R_1 C_1'} = \frac{1}{f_c R_1 (C_1 + C_2)}$$

$$\alpha_{12} = \alpha_{11}$$

$$\alpha_{13} = 2\alpha_{11}$$

$$\alpha_{21} = \alpha_{22} = \frac{1}{f_c \tau_2} = \frac{L_2}{f_c R_1}$$

$$\alpha_{31} = \frac{1}{f_c \tau_3} = \frac{1}{f_c R_1 C_3'} = \frac{1}{f_c R_1 (C_3 + C_2)}$$

$$\alpha_{32} = \frac{R_1}{R_3} \alpha_{31}$$

$$\beta_1 = \frac{C_2}{C_1'} = \frac{C_2}{C_1 + C_2}$$

$$\beta_3 = \frac{C_2}{C_3'} = \frac{C_2}{C_3 + C_2}$$

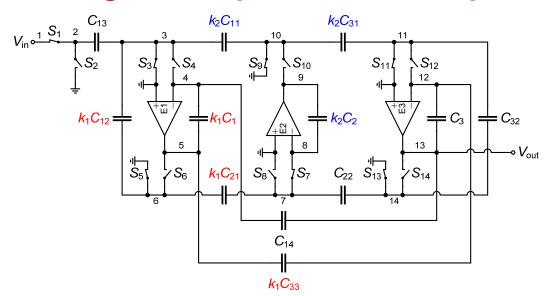

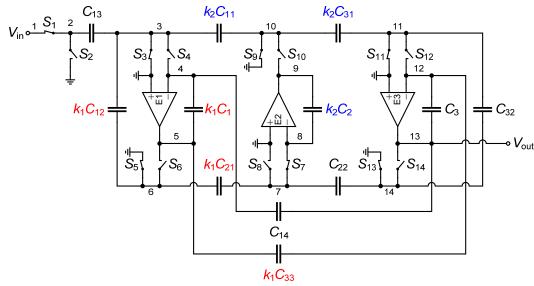

#### **Ladder Filters – 3<sup>rd</sup>-order Elliptic Filter Switcap Simulations**

#### SWITCAP NETLIST

TITLE: 3RD ORDER LP ELLIPTIC FILTER

OPTIONS; CHKCLK; REPORT; END; TIMING: PERIOD 50E-6; CLOCK CLK 1 (0 3/8); END; CIRCUIT; S1 (2 1) CLK; S2 (2 0) #CLK; S3 (3 0) CLK; S4 (3 4) #CLK; S5 (6 0) CLK; S6 (6 5) #CLK; S7 (7 8) CLK: S8 (7 0) #CLK; S9 (10 0) CLK; S10 (10 9) #CLK; S11 (11 0) CLK; S12 (11 12) #CLK; S13 (14 0) CLK; S14 (14 13) #CLK; C11 (3 10) 0.141; C12 (3 6) 0.141; C13 (3 2) 0.282; C14 (4 13) 0.071; C1 (4 5) 1; C21 (7 6) 0.32;

C22 (7 14) 0.32; C2 (8 9) 1; C31 (11 10) 0.141; C32 (11 14) 0.141;

C33 (5 12) 0.071; C3 (12 13) 1; E1 (5 0 0 4) 10000;

E2 (9 0 0 8) 10000; E3 (13 0 0 12) 10000; V1 (1 0);

V1 (1 0); END; ANALYZE SSS;

INFREQ 0 10000 LIN 501; SET V1 AC 1.0 0.0;

PRINT VDB(13) VP(13); PLOT VDB(13);

END; END;

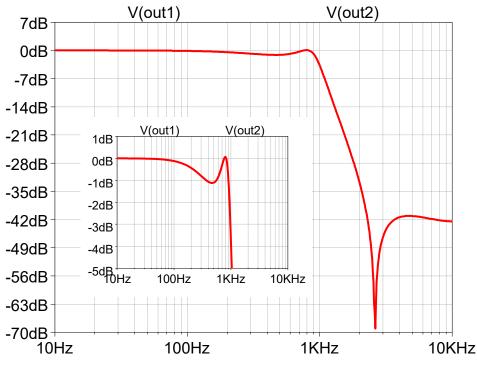

#### **Ladder Filters – 3<sup>rd</sup>-order Elliptic Filter LTSpice Simulations**

# Scaling of SCF

- Actual performance of SCF can be improved to

- Maximize dynamic range

- Minimize capacitance spread and total capacitance

- Minimize sensitivity to OPAMP dc gain effects

- Maximize for dynamic range in order for the OPAMPs not to saturate

- ▶ Transfer functions from input to each OPAMP output might have overshoots (close to the cut-off frequency) and hence make the OPAMPs saturate

- ▶ To impose that all OPAMPs saturate at about the same input voltage, the capacitances connected or switched to each OPAMP output can be scaled without changing the overall transfer function to reduce its output voltage

- Scaling for maximum dynamic range therefore means adjusting the capacitances such that the OPAMP output voltages  $V_k$  remain smaller than the input voltage  $V_{in}$

$$\left| \frac{V_k(\omega)}{V_{in}} \right| \le 1 \text{ for any } \omega$$

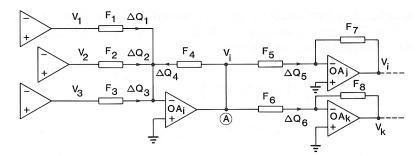

# Scaling of SCF

Transfer function of branch between OA<sub>i</sub> output an virtual ground

$$F_4(z) = \frac{\Delta Q_4(z)}{V_i(z)}$$

• Multiply all capacitances in branches  $F_4$ ,  $F_5$  and  $F_6$  connected to the output of  $OA_i$  by  $k_i$ . Since input branches remain unchanged,  $\Delta Q_4$  remains unchanged as well. The output voltage of  $OA_i$  thus becomes

$$V_i'(z) = \frac{\Delta Q_4(z)}{k_i F_4(z)} = \frac{V_i(z)}{k_i}$$

- Thus, multiplying all capacitors connected (or switched) to the output of  $OA_i$  decreases its voltage by  $V_i(z)/k_i$

- This scaling procedure can be used to improve the dynamic range of SCF

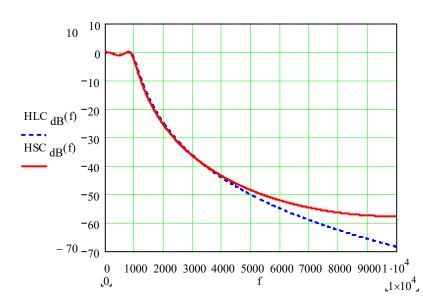

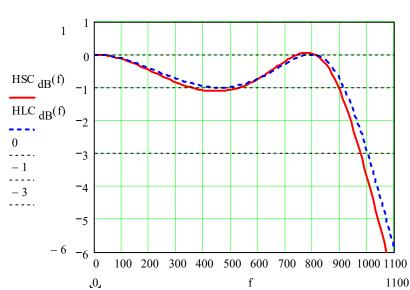

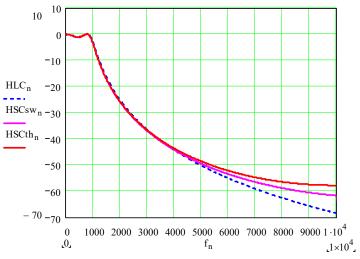

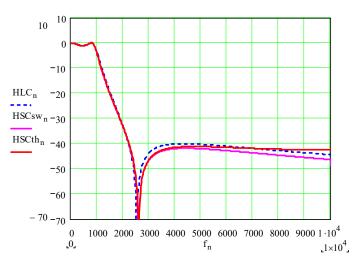

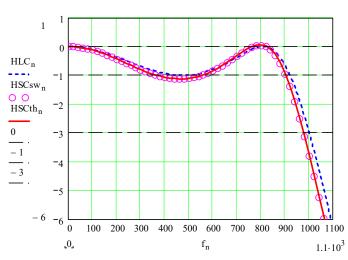

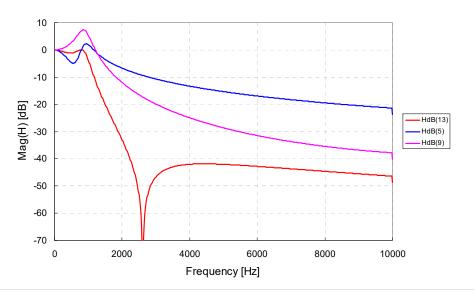

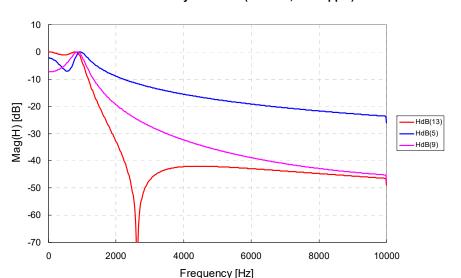

# Scaling – Example 3<sup>rd</sup>-order Elliptic LP SCF (before scaling)

Max. values of transfer functions between input and nodes (5), (9) and (13) prior to scaling

$$H_{dB,max}(5) = 2.229 dB$$

$$H_{dB,max}(9) = 7.397 dB$$

Corresponding scaling factors

$$k_1 = 1.293$$

$$k_2 = 2.343$$

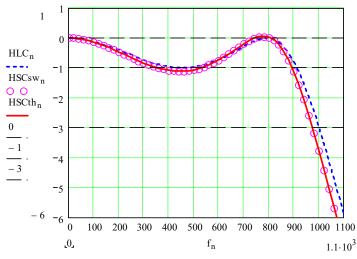

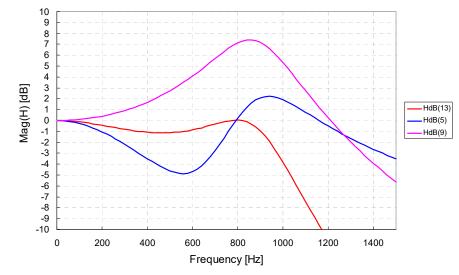

3rd-Order Chebyshev SCF (fc=1kHz, 1dB ripple)

3rd-Order Chebyshev SCF (fc=1kHz, 1dB ripple)

# Scaling – Example 3<sup>rd</sup>-order Elliptic LP SCF (after scaling)

With scaling factors

$$k_1 = 1.293$$

$$k_2 = 2.343$$

3rd-Order Chebyshev SCF (fc=1kHz, 1dB ripple)

3rd-Order Chebyshev SCF (fc=1kHz, 1dB ripple)