# Boucles à verrouillage de phase ou "Phase-Locked Loop" (PLL)

A lonescu

## Applications: SYNTHESE DE FREQUENCES à PLL

#### SYNTHESE DE FREQUENCES A PLL

- 1. Principes de base d'un synthétiseur à PLL

- 2. PLL à diviseur programmable simple

- 3. PLL à *pré-diviseur fixe*

- 4. PLL à pré-diviseur à double modulo P / P+1

- 5. PLL à division fractionnaire

- 6. Caractéristiques principales des synthétiseurs

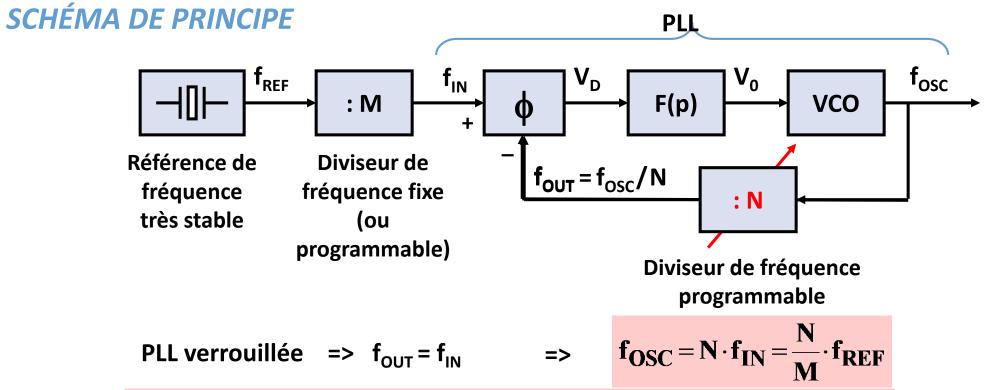

#### 1. PRINCIPES DE BASE D'UN SYNTHÉTISEUR À PLL

La résolution sur la fréquence synthétisée:  $\Delta f_{OSC} = f_{IN} = f_{REF}/M$

(car N est variable par pas de 1)

À noter que la <u>multiplication</u>  $f_{OSC}=N \cdot f_{IN}$  est rendue possible à l'aide d'un <u>diviseur</u> dans la boucle, grâce à la <u>réaction</u> <u>négative</u> et au <u>phénomène de verrouillage de phase</u>, qui impose  $f_{IN}=f_{OUT}$ .

Il est également important de noter que, dans le cas du synthétiseur,  $f_{IN}$  est générée à partir d'une référence fixe. Ainsi, pendant la phase de capture et de verrouillage, c'est principalement  $f_{OUT}$  qui varie lorsque le facteur N est changé (compteur programmable).

#### 1. PRINCIPES DE BASE D'UN SYNTHÉTISEUR À PLL

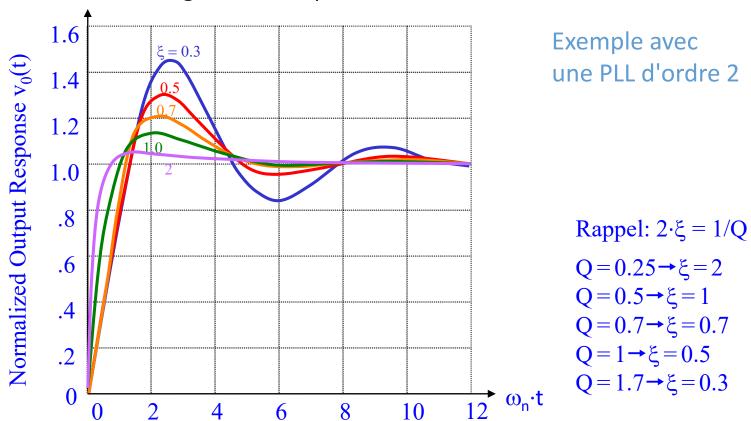

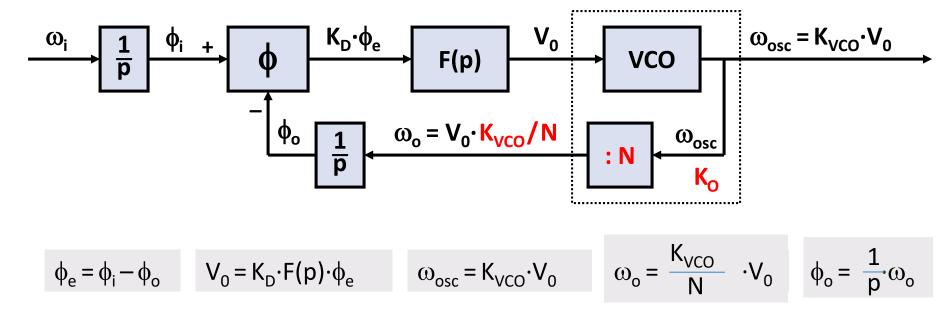

#### FONCTION DE TRANSFERT DE LA PLL

Le diviseur a pour effet de réduire d'un facteur N le "gain" K<sub>VCO</sub> du VCO, et donc celui de la boucle ouverte

$$\frac{\phi_e}{\phi_i} = \frac{p}{p + \frac{K_D \cdot F(p) \cdot K_{VCO}}{N}} \qquad \frac{\omega_{osc}}{\omega_i} = \frac{N}{1 + p \cdot \frac{N}{K_D \cdot F(p) \cdot K_{VCO}}}$$

Une variation trop importante de N (par exemple de Nmin à Nmax) peut provoquer des problèmes de stabilité de la boucle, car correspond une sollicitation 'saut de fréquence' pour f<sub>OUT</sub>

#### 1. PRINCIPES DE BASE D'UN SYNTHÉTISEUR À PLL

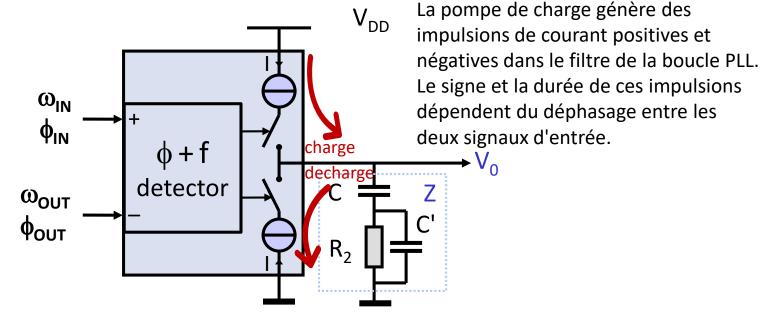

#### DÉTECTEUR DE PHASE-FRÉQUENCE ET FILTRE INTÉGRATEUR

Pour la synthèse de fréquence, le détecteur de phase est généralement de type phase-fréquence séquentiel, couplé à un filtre intégrateur "charge pump" de degré 2 ou plus.

La PLL sera donc de degré 3 ou plus élevé.

Grâce au détecteur phase-fréquence associé au filtre intégrateur, les domaines de capture et de verrouillage sont identiques et limités par la dynamique du signal  $V_0$  ou celle du VCO.

Le filtre de degré 2, voir plus, permet de réduire les perturbations à  $f_{\rm IN}$ , créées par le détecteur de phase, dont les résidus qui parviennent à l'entrée du VCO provoquent une modulation indésirable de la fréquence  $f_{\rm OSC}$ .

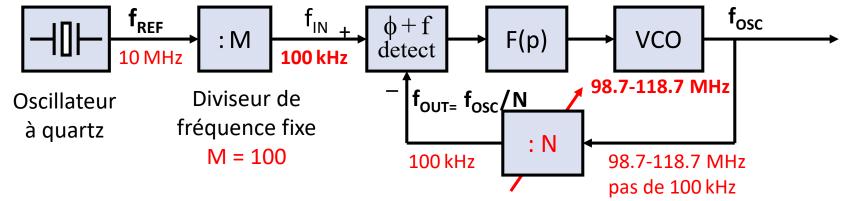

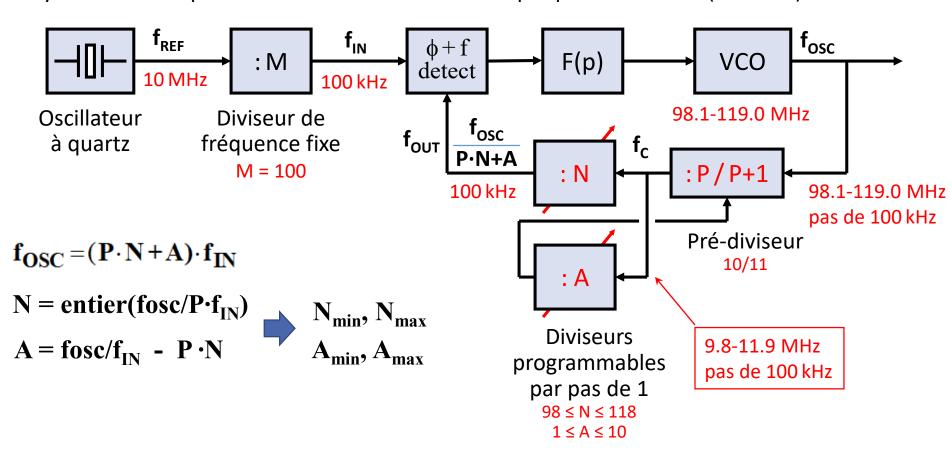

#### 2. PLL À DIVISEUR PROGRAMMABLE SIMPLE

#### SCHÉMA DE BASE - EXEMPLE DE DIMENSIONNEMENT

Oscillateur local d'un récepteur FM:

Synthèse de fréquence de 98.7 MHz à 118.7 MHz par pas de 100 kHz.

Diviseur programmable par pas de 1

$987 \le N \le 1187$  (compteur avec 11 bits)

PLL verrouillée =>

$$f_{OUT} = f_{IN}$$

=>  $f_{OSC} = N \cdot f_{IN} = \frac{N}{M} \cdot f_{REF}$

$$\Delta f_{OSC} = f_{IN} = f_{REF}/M$$

Le diviseur programmable doit supporter un fréquence maximum de Clock de 120 MHz. Solution peu économique car N doit être réalisé dans une technologie très performante (rapide)!

#### 2. PLL À DIVISEUR PROGRAMMABLE SIMPLE

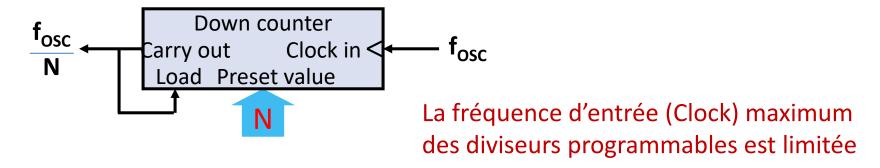

#### LIMITATION EN FRÉQUENCE DU DIVISEUR PROGRAMMABLE

Le diviseur programmable est généralement un <u>décompteur</u> réinitialisé à la valeur N après passage par 1 (ou réinitialisé à N-1 après passage par 0)

#### **Exemple de diviseurs programmables**

74 HC 192 40 MHz 74 AC 11192 125 MHz

#### **Exemple de PLL complètes**

MC 145106 20 MHz MC 145167 60 MHz

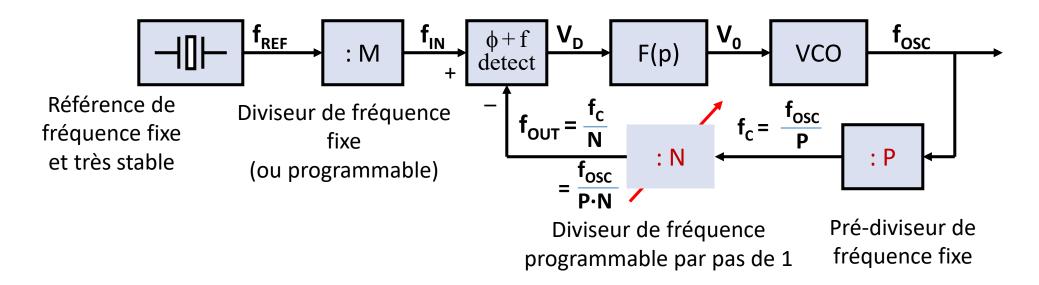

#### 3. PLL À PRÉ-DIVISEUR FIXE

#### SCHÉMA DE PRINCIPE

PLL verrouillée =>

$$f_{OUT} = f_{IN}$$

=>  $f_{OSC} = P \cdot N \cdot f_{IN} = \frac{P \cdot N}{M} \cdot f_{REF}$

La résolution sur la fréquence synthétisée:  $\Delta f_{OSC} = P \cdot f_{IN} = P \cdot f_{REF}/M$

On remarque que si l'on veut une résolution fine, étant donné que P est fixe, la seule option est de réduire f<sub>IN</sub> mais cela peut affecter les performances de la PLL (bande passante réduite, temps de verrouillage augmente, bruit de phase plus important)

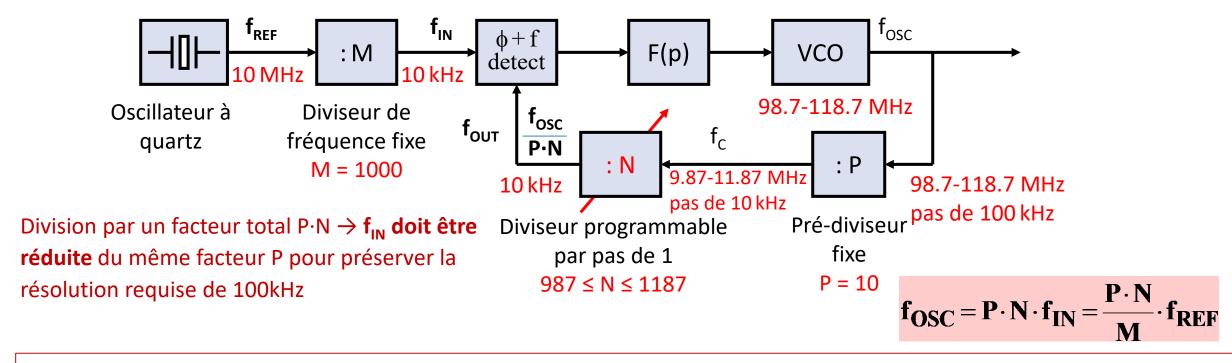

#### 3. PLL À PRÉ-DIVISEUR FIXE

#### EXEMPLE DE DIMENSIONNEMENT

Oscillateur local d'un récepteur FM:

Synthèse de fréquence de 98.7 MHz à 118.7 MHz par pas de 100 kHz (0.1 MHz)

#### Cette solution engendre d'autres inconvénients :

- La fréquence de coupure du filtre passe-bas F(p) diminue avec f<sub>IN</sub> → le temps de réponse de la PLL augmente

- le facteur de division total est plus élevé, le bruit de phase augmente

## 2. & 3. SYNTHÉTISEUR À PLL AVEC DIVISEUR PROGRAMMABLE SIMPLE OU PRÉ-DIVISEUR FIXE

#### RÉSUMÉ DES LIMITATIONS

- Fréquence d'entrée limitée du diviseur programmable.

- Comportement dynamique de la boucle dégradé pour des gammes importantes du rapport de division N.

- Temps de réponse important lorsque le pas des fréquences à synthétiser est petit (f<sub>IN</sub> basse).

- Bruit de phase plus important à la sortie lorsque le facteur de division total est élevé.

- Avec pré-diviseur fixe, la résolution étant de P·f<sub>IN</sub>, il faut diminuer f<sub>IN</sub> pour conserver la résolution; le facteur de division total est augmenté d'autant (mais affecte la stabilité et bruit de phase important).

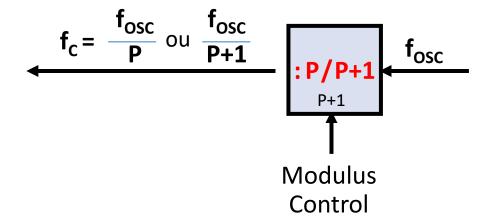

#### 4. PLL À PRÉ-DIVISEUR P/P+1

#### PRINCIPE DU PRÉ-DIVISEUR A DOUBLE MODULO

Un pré-diviseur à double modulo (Dual Modulus Prescaler) est un diviseur de fréquence dont le facteur de division est de P ou de P+1 en fonction de l'état d'une entrée binaire de commande.

Les pré-diviseurs à double modulo ont une structure interne optimisée pour accepter une fréquence d'entrée élevée.

Le facteur de division de base P est souvent une puissance de 2.

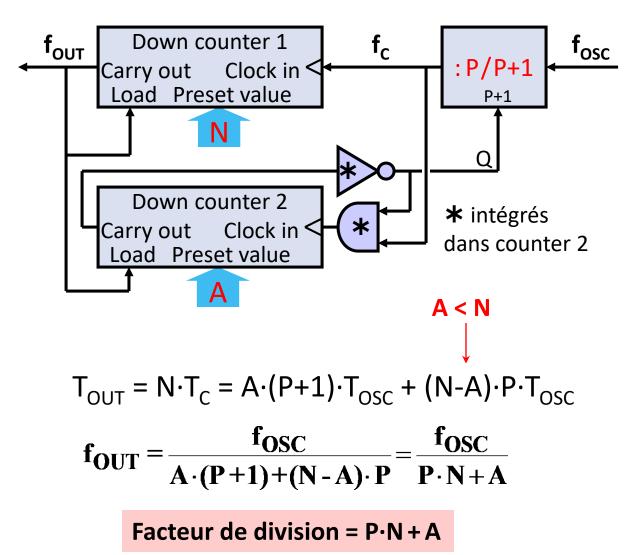

#### 4. PLL À PRÉ-DIVISEUR P / P+1

#### PRINCIPE DU DIVISEUR A PRÉ-DIVISEUR P/P+1

#### 4. PLL À PRÉ-DIVISEUR P / P+1

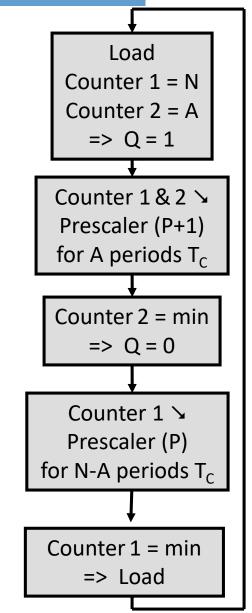

#### SYNTHÉTISEUR À PRÉ-DIVISEUR P/P+1

La résolution sur la fréquence synthétisée:  $\Delta f_{OSC} = f_{IN}$

#### 4. PLL À PRÉ-DIVISEUR P / P+1

#### **EXEMPLE DE DIMENSIONNEMENT**

Oscillateur local d'un récepteur FM:

Synthèse de fréquence de 98.7 MHz à 118.7 MHz par pas de 100 kHz (0.1 MHz)

#### 4. SYNTHÉTISEUR À PLL AVEC PRÉ-DIVISEUR P / P+1

#### **CARACTÉRISTIQUES**

- La division se fait à nouveau par pas unitaire => résolution:  $\Delta f_{OSC} = f_{IN}$

- Par comparaison, avec un pré-diviseur fixe: résolution  $\Delta f_{OSC} = P \cdot f_{IN}$

- La fréquence d'entrée du pré-diviseur P/P+1 peut être élevée car ces diviseurs dits "dual modulus" ont une structure optimisée pour la vitesse

Exemple de diviseur : LMX 2305 (National)

pré-division par 64/65 ou par 128/129

fréquence max. 550 MHz

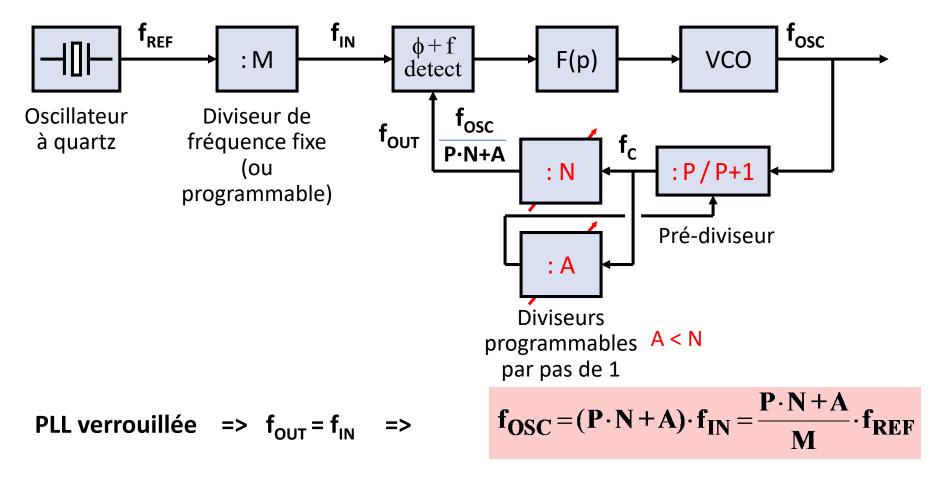

#### SCHÉMA DE PRINCIPE GLOBAL

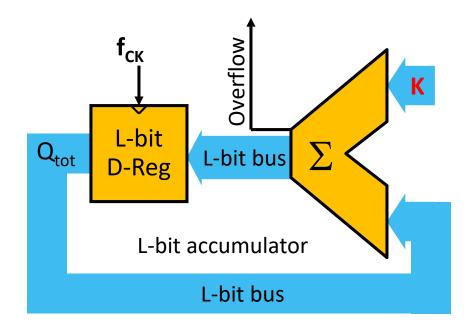

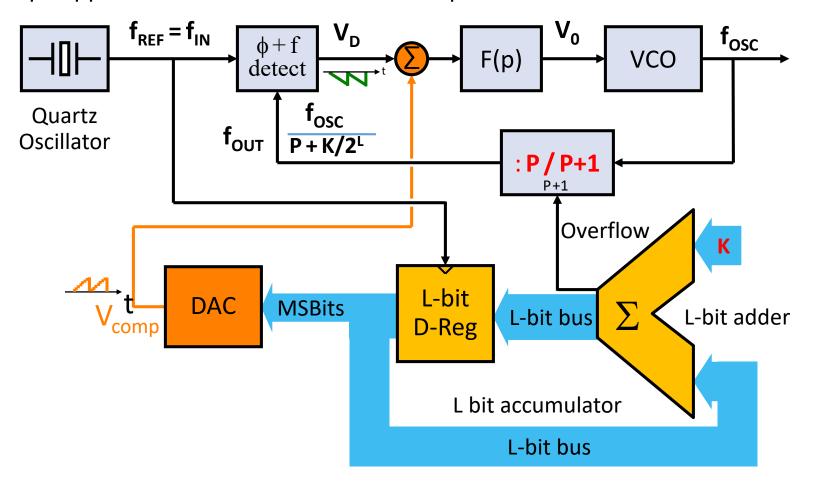

#### FONCTIONNEMENT DE L'ACCUMULATEUR

- L'accumulateur est un système séquentiel sur L bits qui, à chaque coup d'horloge, ajoute K à son état Q<sub>tot</sub> précédant: (Q<sub>tot</sub>+K)→Q<sub>tot</sub>

- K est un nombre codé en binaire sur L bits ou moins.

- Chaque fois que  $(Q_{tot}+K)$  dépasse  $2^L$ , l'accumulateur oublie  $2^L$ :  $(Q_{tot}+K-2^L) \rightarrow Q_{tot}$  (registre 'vide') et un signal "Overflow" est généré

Si l'accumulateur avait une capacité illimitée, en une seconde (unité standard du temps), il aurait accumulé:

$$Q_{tot} = f_{CK} \cdot K$$

Avec une capacité limitée à  $2^L$ , l'accumulateur va faire  $f_{OFL}$  Overflows par seconde:

$$f_{OFI} = f_{CK} \cdot K/2^L$$

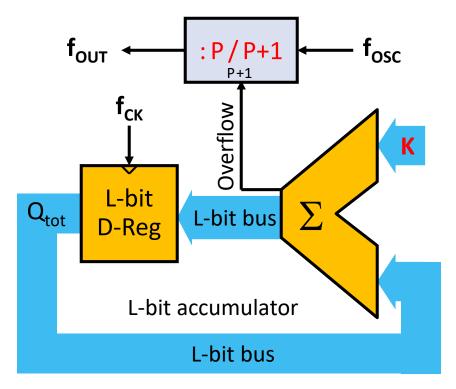

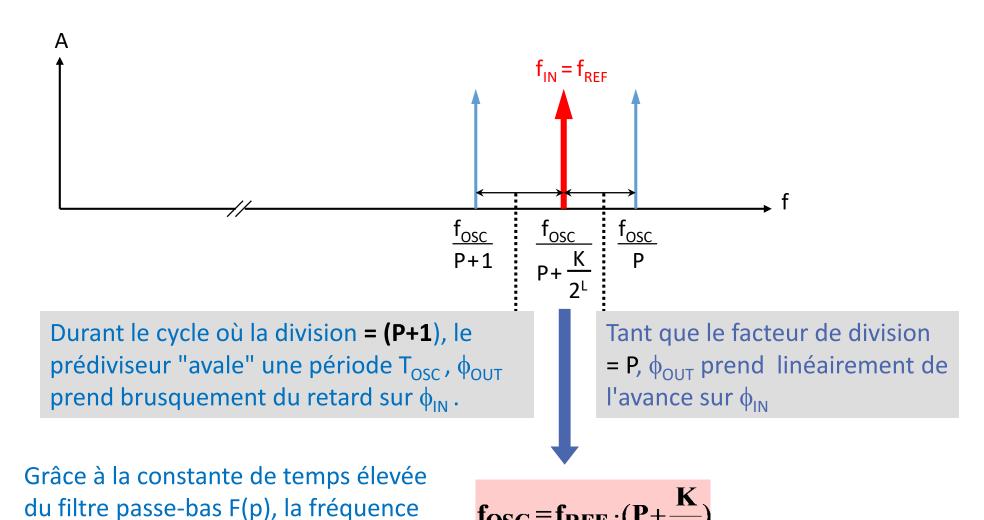

#### CALCUL DU FACTEUR DE DIVISION

Le facteur de division normal est de **P**, sauf à chaque "Overflow" où il est <u>une seule fois</u> de **(P+1)**.

On peut aussi considérer qu'à chaque "Overflow" une période T<sub>OSC</sub> est ignorée ou "avalée" (Pulse Swallow).

Durant chaque seconde, le diviseur reçoit  $f_{OSC}$  périodes en entrée, il en ignore autant qu'il y a d'Overflows, donc  $f_{OFL}$ , et il divise le reste par P.

$$f_{OUT} = \frac{f_{OSC} - f_{OFL}}{P} = \frac{f_{OSC} - f_{CK} \cdot K/2^{L}}{P}$$

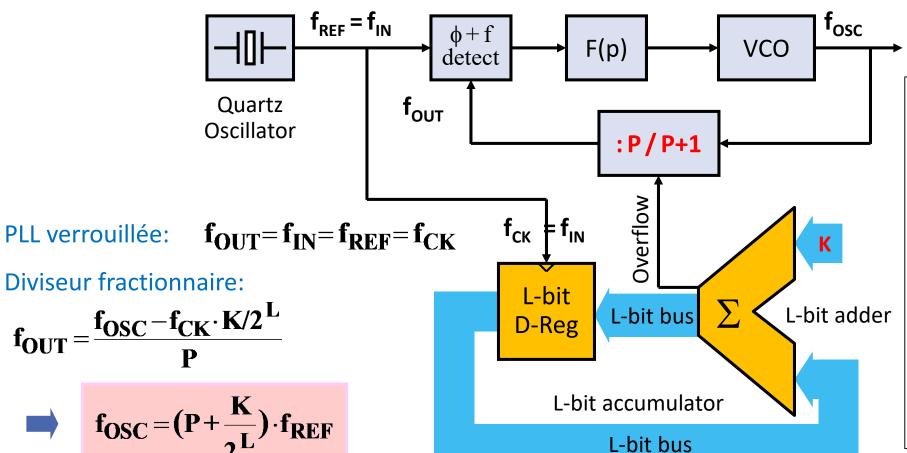

#### SYNTHÉTISEUR À DIVISEUR FRACTIONNAIRE

Notez que ce diviseur ne divise pas directement la fréquence de sortie par une valeur fractionnaire à chaque cycle.

Au lieu de cela, à chaque cycle, il effectue une division entière (soit P ou P+1, selon l'état de l'accumulateur).

La division par une valeur fractionnaire se fait en réalité de manière statistique, c'est-à-dire que la moyenne des valeurs sur une période de temps donne l'effet d'un diviseur fractionnaire.

Donc  $\mathbf{f_{OSC}}$  change de  $\mathbf{f_{REF}}/2^{L}$  par pas de  $\mathbf{K}$

$\rightarrow$  La résolution sur la fréquence synthétisée :  $\Delta f_{OSC} = f_{REF} \cdot (K/2^L) = f_{IN} \cdot (K/2^L)$ ,  $K < 2^L$

#### EXEMPLE DE DIMENSIONNEMENT

On veut synthétiser des porteuses,  $f_{OSC}$  dans la bande des 433 MHz, avec une résolution de  $f_{REF}$ =1 kHz ou plus fine.

A ces fréquences, on trouve des pré-diviseurs 'Pulse Swallow' (: P/P+1) du type 64/65

Il faudra une fréquence de référence *autour* de:  $f_{REF} = 433 \,\text{MHz} / 64.5 \approx 6.71 \,\text{MHz}$

Supposons une fréquence de référence  $f_{RFF} = f_{IN} = 6.7 \text{ MHz}$

Avec  $f_{REF}$  choisi on pourra couvrir la gamme de fréq. instantanées à la sortie:  $f_{OSC,min} = 64 \cdot 6.7 = 428.8 \text{ MHz}$  à  $f_{OSC,max} = 65 \cdot 6.7 = 435.5 \text{ MHz}$

Pour obtenir une résolution de 1 kHz, il faut :  $\Delta f_{OSC} = f_{REF}(K/2^L) = 6.7 \text{ MHz}(K/2^L) \le 1 \text{ kHz} => \text{ on choisi } L_{min} = 13, K=1$

Mais  $\Delta f_{OSC} = 6.7 \, \text{MHz} / 2^{13} = 818 \, \text{Hz} => erreur possible de 409 Hz sur freq synthétisée, soit environ 0.5 <math>\times$  résolution désirée de 1KHz !

Pour réduire cette erreurs, supposons qu'on choisi un accumulateur à L=20 bits

La résolution réelle sera de  $\Delta f_{OSC} = 6.7 \text{ MHz} / 2^{20} = 6.4 \text{ Hz}$  => erreur possible 3.2 Hz, donc meilleur solution!

$f_{OUT} = f_{IN} = f_{REF} = f_{CK}$   $f_{OUT} = \frac{f_{OSC} - f_{CK} \cdot K/2^{L}}{P}$   $f_{OSC} = (P + \frac{K}{2^{L}}) \cdot f_{REF}$

$\Delta f_{OSC} = f_{REF} \cdot (K/2^L)$

Voir explication slide

suivant

Pour comprendre l'affirmation « erreur possible de 409Hz sur fréq. synthétisée, soit environ 0.5 × résolution désirée (1KHz ou sous-multiples)! » il faut penser au fait que :

- (1) la division fractionnaire est obtenue par un moyennage statistique des divisions entières ;

- (2) le calcul arithmétique se fait en général avec des arrondis.

Si on considère un l'exemple : 4 < 4.3 < 5 et 4 < 4.7 < 5. Si on considère une résolution unitaire, l'arrondi à l'unité de 4.3 est 4. L'arrondi à l'unité de 4.7 est 5. L'erreur d'arrondi (approximation) maximum est la moitié de la résolution sur l'échelle unitaire, donc ½\*1 (par exemple quand il y a arrondi de 4.49 à 4 ou de 4.5 à 5)

Bien sûr, si on choisit une résolution plus fine, 1/10 par exemple, et on fait l'arrondi à la décimale, l'erreur diminue (par exemple 4,75 arrondit à 4,8 au lieu de 5).

du VCO se situe à:

#### SIGNAUX AUX ENTRÉES DU DÉTECTEUR DE PHASE

23

#### COMPENSATION DE L'ERREUR DE PHASE

Dans les systèmes les plus sophistiqués, on peut obtenir une extrême stabilité de la fréquence de sortie en compensant, par un circuit mixte analogique et numérique, l'erreur de phase en dents de scie qui apparaît à la sortie du détecteur de phase.

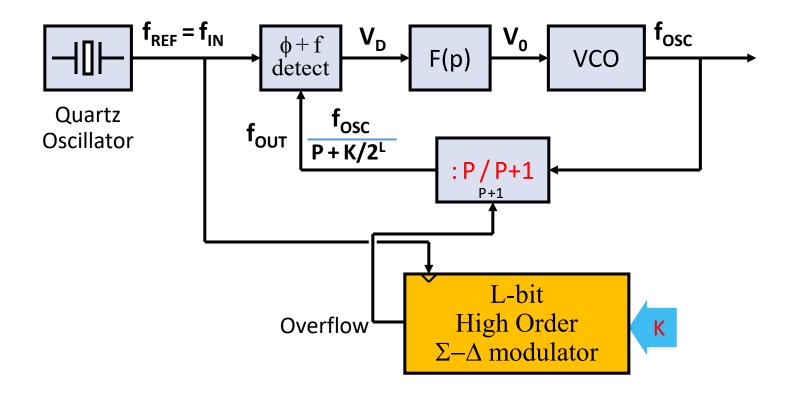

#### COMPENSATION DE L'ERREUR DE PHASE

Une solution plus économique, car entièrement numérique, consiste à remplacer l'accumulateur par un modulateur  $\Sigma-\Delta$  d'ordre élevé, dont l'effet de "Noise Shapping", atténue les composantes basses fréquences de l'erreur de phase et donc leur effet sur  $V_0$  et sur la fréquence  $f_{OSC}$  du VCO.

#### 5. SYNTHÉTISEUR À PLL AVEC DIVISION FRACTIONNAIRE

#### **CARACTÉRISTIQUES**

Possibilité de résolution très fine

pourtant

- Fréquence de travail de la PLL f<sub>IN</sub> élevée, d'où une rapidité de réaction élevée de la boucle PLL ('frequency agile')

- Bruit de phase faible à très faible

par contre

Rapport max/min de la fréquence synthétisée limité à (1 + 1/P)

## 6. PRINCIPALES CARACTERISTIQUES DES SYNTHETISEURS DE FREQUENCES

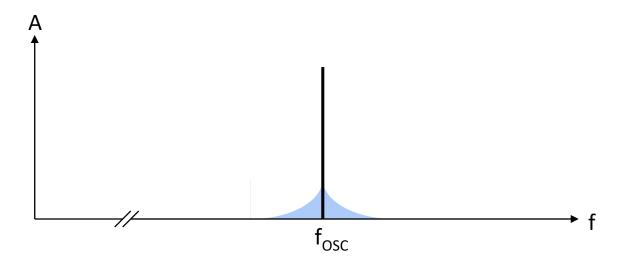

#### BRUIT DE PHASE (PHASE NOISE)

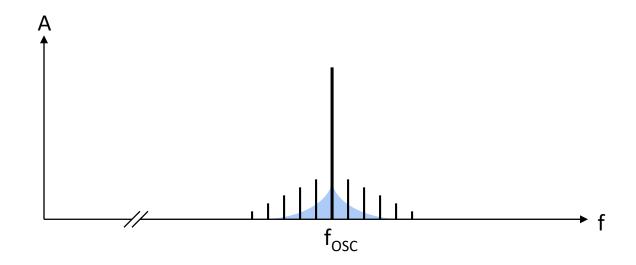

- Variations aléatoires de la phase instantannée du signal généré par le VCO. Une partie est due au VCO lui-même, une partie est provoquée par du bruit à l'entrée du VCO.

- Le bruit de phase est d'autant plus important que le rapport de division total de fréquence dans la boucle de phase est élevé.

## 6. PRINCIPALES CARACTERISTIQUES DES SYNTHETISEURS DE FREQUENCES

#### PARASITES (SPURS)

Modulation de fréquence provoquée par les "restes" sur  $V_0$ , de composantes alternatives de  $V_D$ , insuffisamment atténuées par le filtre passe-bas.

### 6. PRINCIPALES CARACTERISTIQUES DES SYNTHETISEURS DE FREQUENCES

#### TEMPS D'ETABLISSEMENT (SETTLING TIME)

Temps nécessaire pour que f<sub>OSC</sub> atteigne la valeur désirée avec une tolérance donnée à partir de l'instant de changement de la consigne numérique