## Boucles à verrouillage de phase "Phase-Locked Loops" - PLL

Introduction et notions de base Etude générale Modèle linéaire et fonction de transfert Comportement dynamique

Etude des blocs fonctionnels: Détecteurs de Phase VOC

Applications

## DÉTECTEURS DE PHASE

## DÉTECTEURS DE PHASE

- Introduction

- Détecteurs de phase analogiques

- Détecteur de phase numérique XOR

- Détecteur de phase-fréquence numérique

#### **INTRODUCTION**

#### DÉTECTEURS DE PHASE ANALOGIQUES

Multiplieur analogique à cellule de Gilbert "balanced mixer" Signaux impairs, typiquement sinusoïdaux et/ou carrés

#### DÉTECTEUR DE PHASE NUMÉRIQUE XOR

Signaux logiques, avec un rapport cyclique de 50%

#### DÉTECTEURS DE PHASE-FRÉQUENCE NUMÉRIQUES

Logique séquentielle n'admettant que des signaux logiques Indépendants du rapport cyclique des signaux

#### PRINCIPE: MULTIPLIEUR ANALOGIQUE

$$V_{IN} = A_{IN} \cdot \sin(\omega t) \longrightarrow V_{D} = \frac{A_{IN} \cdot A_{OUT}}{Z} \cdot \frac{1}{2} \cdot [\cos(2\omega t - \phi_{E}) - \cos(\phi_{E})]$$

$$PLL \text{ verrouill\'ee}$$

$$\omega_{IN} = \omega_{OUT} = \omega$$

$$V_{OUT} = A_{OUT} \cdot \sin(\omega t - \phi_{E}) \text{ issus du VCO}$$

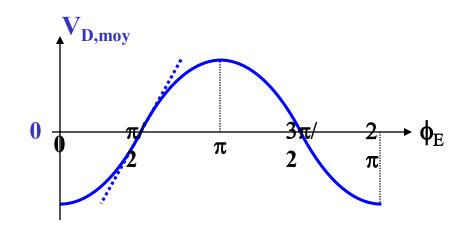

$$V_{D,moy} = \frac{1}{T} \cdot \int_{0}^{T} v_{D}(t) \cdot dt = -\frac{A_{IN} \cdot A_{OUT}}{2 \cdot Z} \cdot \cos(\phi_{E})$$

$$\mathbf{K_D} = \frac{\mathbf{A_{IN} \cdot A_{OUT}}}{2 \cdot \mathbf{Z}}$$

**8** K<sub>D</sub> dépendant de A<sub>IN</sub> et A<sub>OUT</sub>

**8** non-linéaire

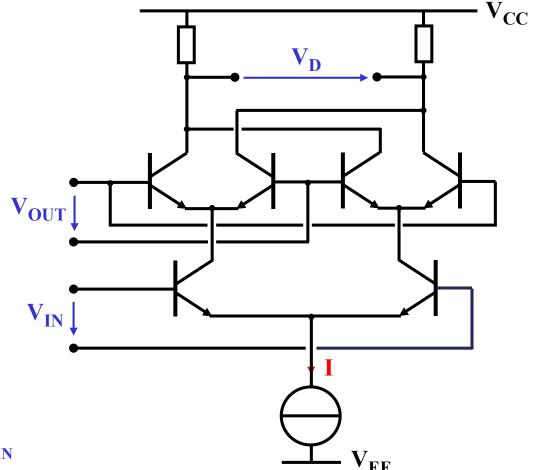

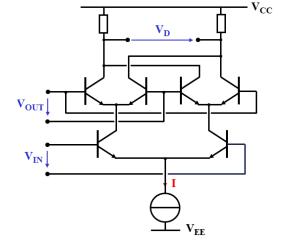

## MODULATEUR ÉQUILIBRÉ OU "MULTIPLIEUR DE GILBERT"

Sinus, triangle ou carré à  $\omega_{OUT}$  issus du VCO (ou d'un diviseur), amplitude > 200 mV<sub>p-p</sub>

Signal d'entrée sinus à  $\omega_{IN}$

Si la PLL est verrouillée,  $\omega_{OUT} = \omega_{IN} \, ,$  retard de phase  $\phi_E$  de  $V_{OUT}$  sur  $V_{IN}$

#### MODULATEUR ÉQUILIBRÉ OU "MULTIPLIEUR DE GILBERT"

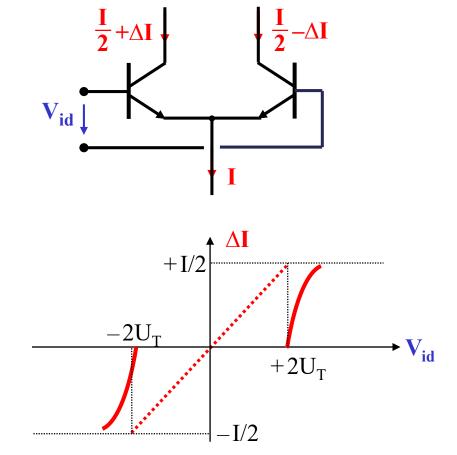

#### Rappels sur la paire différentielle

#### **Relation exacte**

$$\Delta I = \frac{I}{2} \cdot tanh \frac{V_{id}}{2 \cdot U_{T}}$$

#### Signaux $\leq 50 \text{ mV}_{p-p}$

$$\Delta I = \frac{I}{2} \cdot \frac{V_{id}}{2 \cdot U_{T}}$$

#### Carré, triangle ou sinus $\geq 200 \text{ mV}_{p-p}$

$$\Delta I = \frac{I}{2} \cdot signe(V_{id})$$

#### MODULATEUR BALANCÉ OU "MULTIPLIEUR DE GILBERT"

# V<sub>OUT</sub> V<sub>D</sub> V<sub>EE</sub>

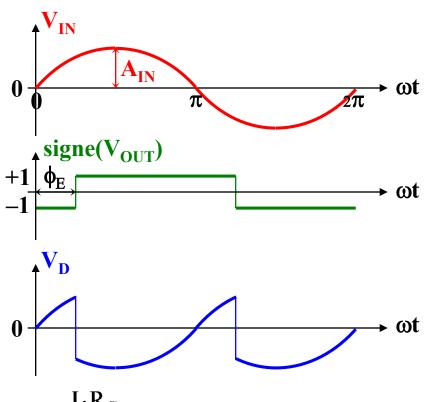

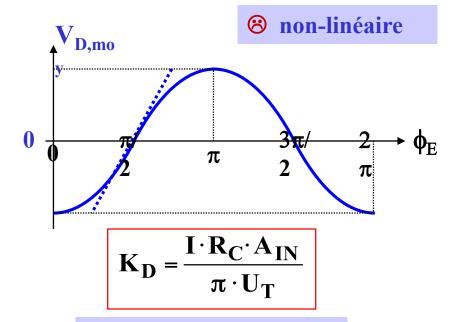

#### PLL verrouillée sur un signal d'entrée $A_{IN}$ ·sin( $\omega_{IN}$ t) "petit" ( $A_{IN}$ < 25 mV)

$$v_{D}(t) = -\frac{I \cdot R_{C}}{2 \cdot U_{T}} \cdot signe(sin(\omega_{IN}t - \phi_{E})) \cdot A_{IN} \cdot sin(\omega_{IN}t)$$

$$V_{D,moy} = \frac{1}{T} \cdot \int_{0}^{T} v_{D}(t) \cdot dt = -\frac{I \cdot R_{C}}{\pi \cdot U_{T}} \cdot A_{IN} \cdot \cos \phi_{E}$$

**8** K<sub>D</sub> dépendant de A<sub>IN</sub>

#### MODULATEUR BALANCÉ OU "MULTIPLIEUR DE GILBERT"

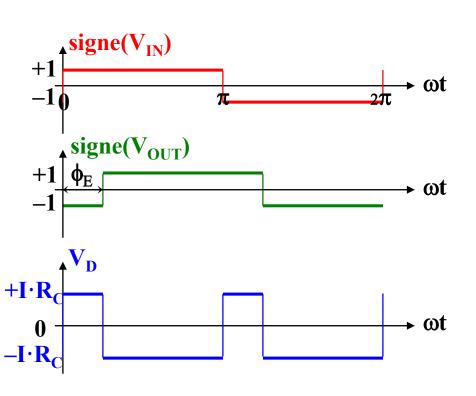

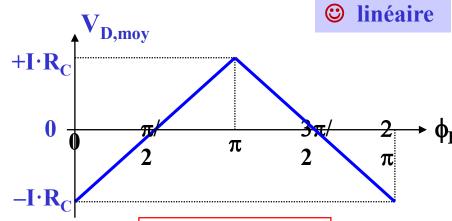

#### PLL verrouillée sur un signal d'entrée $A_{IN} \cdot \sin(\omega_{IN}t)$ "grand" $(A_{IN} > 100 \text{ mV})$

$$V_D = \frac{1}{T} \cdot \int_0^T v_D(t) \cdot dt = \frac{2 \cdot I \cdot R_C}{\pi} \cdot (\phi_E - \frac{\pi}{2})$$

$$\mathbf{K_D} = \frac{2 \cdot \mathbf{I} \cdot \mathbf{R_C}}{\pi}$$

$$v_D(t) = -I \cdot R_C \cdot signe(sin(\omega_{IN}t - \phi_E)) \cdot signe(sin(\omega_{IN}t))$$

**©** K<sub>D</sub> constant

#### MODULATEUR BALANCÉ OU "MULTIPLIEUR DE GILBERT"

#### PLL non-verrouillée: $\omega_{IN} \neq \omega_{OUT}$

signal d'entrée  $A_{IN}$ ·sin( $\omega_{IN}$ t) "petit" ( $A_{IN}$  < 25 mV)

$$V_{D}(t) = -\frac{I \cdot R_{C}}{2 \cdot U_{T}} \cdot signe(sin(\omega_{OUT}t)) \cdot A_{IN} \cdot sin(\omega_{IN}t)$$

$$V_{D,moy} = 0$$

$$V_{D,\text{moy}} = 0 \qquad V_{D,\text{battement, fondamentale}}(t) = \frac{I \cdot R_C}{2 \cdot U_T} \cdot \frac{1}{2} \cdot \frac{4}{\pi} \cdot A_{IN} \cdot \cos(|\omega_{IN} - \omega_{OUT}|t)$$

signal d'entrée  $A_{IN}$ ·sin( $\omega_{IN}$ t) "grand" ( $A_{IN} > 100 \text{ mV}$ )

$$V_D(t) = -I \cdot R_C \cdot signe(sin(\omega_{OUT}t)) \cdot signe(sin(\omega_{IN}t))$$

$$V_{D,moy} = 0$$

$$V_{D,battement}(t) = I \cdot R_C \cdot triangle(|\omega_{IN} - \omega_{OUT}|t)$$

$$V_{D,moy} = 0$$

$$V_{D,battement}(t) = I \cdot R_{C} \cdot triangle(|\omega_{IN} - \omega_{OUT}|t)$$

$$V_{D,battement,fondamentale}(t) = I \cdot R_{C} \cdot \frac{8}{\pi^{2}} \cdot cos(|\omega_{IN} - \omega_{OUT}|t)$$

→ pas de comparaison de fréquence

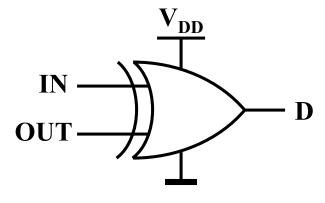

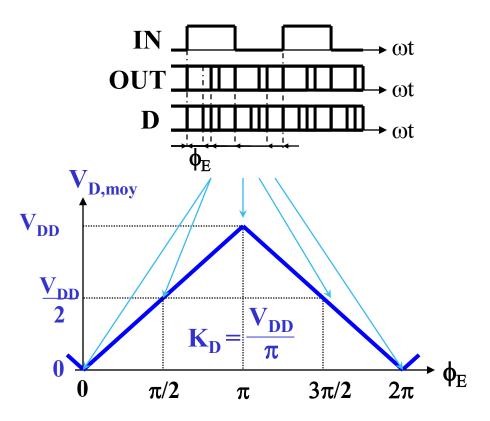

## 2. DÉTECTEUR DE PHASE NUMÉRIQUE XOR

#### **PRINCIPE**

| IN | OUT | D |

|----|-----|---|

| 0  | 0   | 0 |

| 0  | 1   | 1 |

| 1  | 0   | 1 |

| 1  | 1   | 0 |

$$\mathbf{V}_{\mathbf{D}} = \mathbf{V}_{\mathbf{DD}} \cdot \mathbf{D}$$

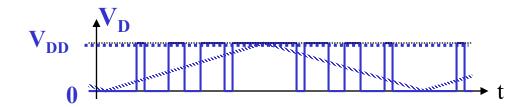

#### PLL verrouillée

## 2. DÉTECTEUR DE PHASE NUMÉRIQUE XOR

#### **PRINCIPE**

| IN | OUT | D |

|----|-----|---|

| 0  | 0   | 0 |

| 0  | 1   | 1 |

| 1  | 0   | 1 |

| 1  | 1   | 0 |

$$\mathbf{V}_{\mathbf{D}} = \mathbf{V}_{\mathbf{DD}} \cdot \mathbf{D}$$

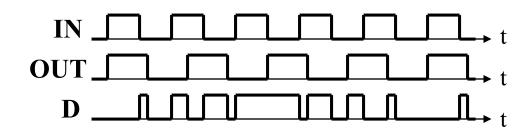

#### PLL non verrouillée

$$V_{D,moy} = V_{DD}/2$$

pas de comparaison de fréquence

$$V_{D,battement}(t) = \frac{V_{DD}}{2} \cdot (1 + triangle(|\omega_{IN} - \omega_{OUT}|t))$$

$$\approx K_{\rm D} \frac{\pi}{2} (1 + \cos(|\omega_{\rm IN} - \omega_{\rm OUT}|t))$$

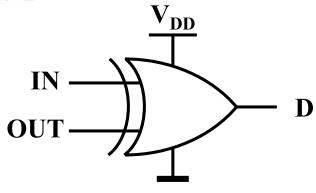

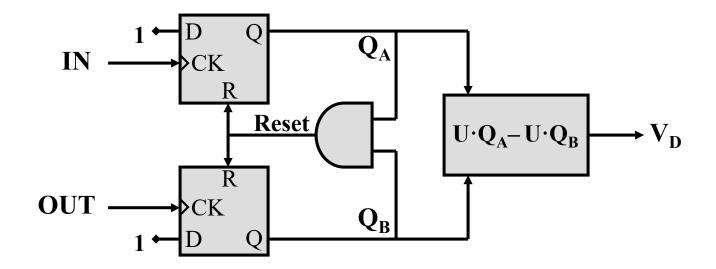

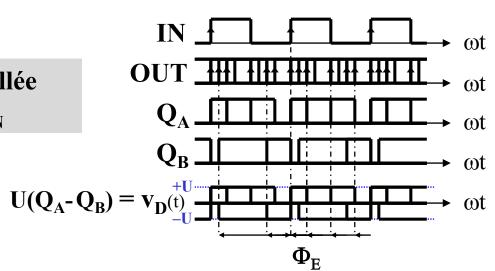

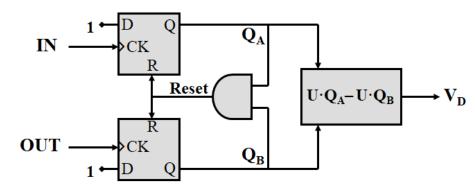

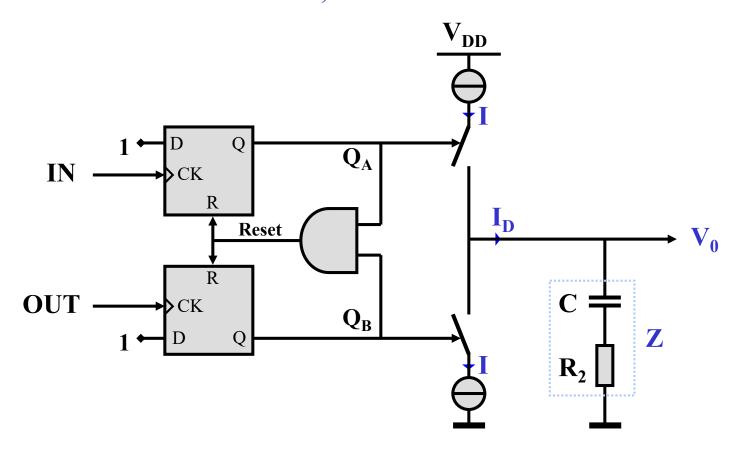

#### **PRINCIPE**

SCHÉMA DE PRINCIPE

**DIAGRAMME DES ÉTATS**

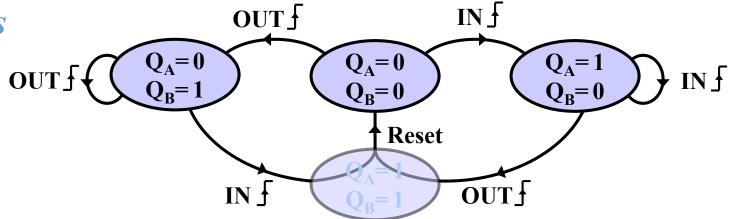

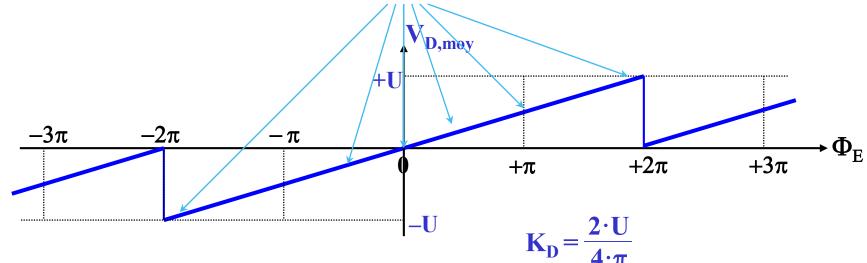

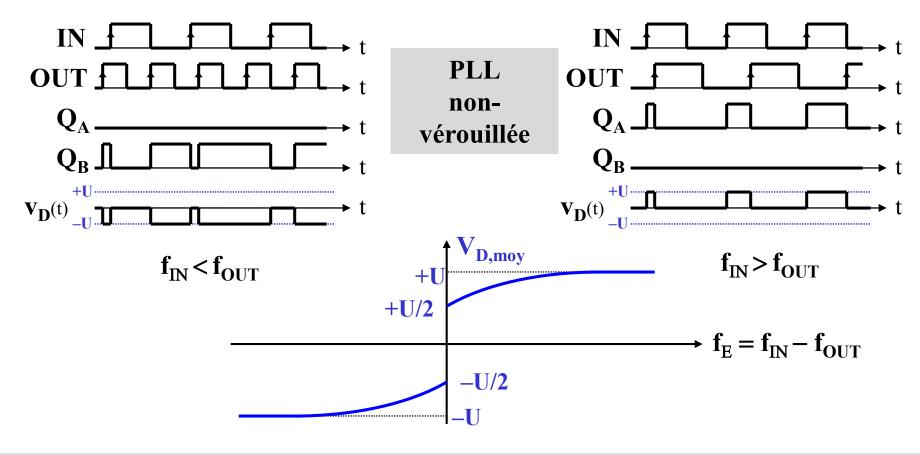

#### **PRINCIPE**

PLL vérouillée  $f_{OUT} = f_{IN}$

#### **PRINCIPE**

En cas d'écart de fréquence (PLL déverrouillée), la sortie du détecteur est unipolaire, et sa polarité indique le signe de cet écart. En connectant cette sortie à un filtre intégrateur,  $V_0$  sera une fonction croissante ou décroissante qui va provoquer le balayage de la bande de fréquences en vue de capturer le synchronism $\mathbf{e}_5$

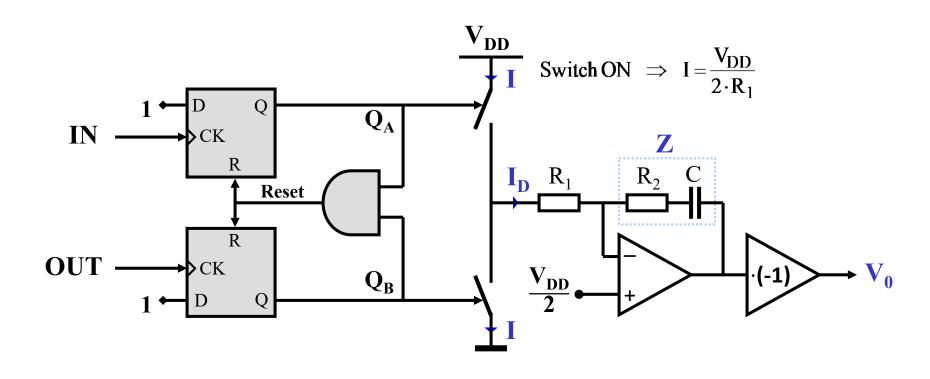

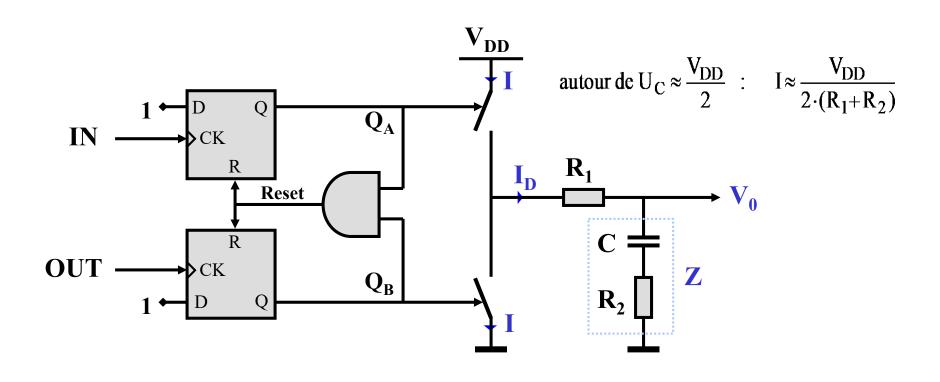

#### DÉTECTEUR Φ-F ET FILTRE ACTIF INTÉGRATEUR SÉPARÉ

$$K_{D} \cdot F(p) = \frac{\overline{I}_{D}}{\phi_{E}} \cdot Z(p) = \frac{I}{2\pi} \cdot \frac{1 + pCR_{2}}{pC} = \frac{V_{DD}}{4\pi} \cdot \frac{1 + pCR_{2}}{pCR_{1}}$$

DÉTECTEUR Φ-F ET FILTRE PASSIF, INTÉGRATEUR PAR "CHARGE PUMP"

$$K_{D} \cdot F(p) = \frac{\overline{I}_{D}}{\phi_{E}} \cdot Z(p) = \frac{I}{2\pi} \cdot \frac{1 + pR_{2}C}{pC} = \frac{V_{DD}}{4\pi} \cdot \frac{1 + pCR_{2}}{pCR_{1}} \underbrace{V_{DD}}_{avec R_{1}} = \frac{V_{DD}}{2I} \text{ fictive}$$

#### DÉTECTEUR Φ-F ET FILTRE PASSIF, PSEUDO-INTÉGRATEUR PAR "CHARGE PUMP"

$$K_{D} \cdot F(p) = \frac{\overline{I}_{D}}{\phi_{E}} \cdot Z(p) = \frac{I}{2\pi} \cdot \frac{1 + pCR_{2}}{pC} \cong \frac{V_{DD}}{4\pi} \cdot \frac{1 + pCR_{2}}{pC(R_{1} + R_{2})}$$

## **DÉTECTEURS DE PHASE : RESUME**

#### DÉTECTEURS DE PHASE ANALOGIQUES "BALANCED MIXER"

Signaux impairs, typiquement sinusoïdaux et/ou carrés Gamme de phase de  $\pm \pi/2$  autour de  $\pi/2$ Linéarité fonction de l'amplitude et de la forme des signaux Admettent les signaux bruités (télécom)

### DÉTECTEUR DE PHASE NUMÉRIQUE XOR

Signaux logiques (ampli limiteur ou comparateur parfois inclus)

Gamme de phase  $\pm \pi/2$  autour de  $\pi/2$ , réduite si le rapport cyclique  $\neq 50\%$ Admet les signaux binaires avec impulsions parasites

#### DÉTECTEURS DE PHASE-FRÉQUENCE NUMÉRIQUES

Logique séquentielle n'admettant que des signaux logiques Gamme de phase de  $\pm 2\pi$  centrée sur 0 Indépendants du rapport cyclique des signaux N'admettent pas les impulsions manquantes ou parasites

# OSCILLATEURS CONTROLES EN TENSION VOLTAGE-CONTROLLED OSCILLATORS (VCO)

## OSCILLATEURS CONTROLES EN TENSION VOLTAGE-CONTROLLED OSCILLATORS (VCO)

• Introduction: définition, classification et caractéristiques

- VCO à Oscillateurs en anneau

- CMOS

- Structure différentielle

#### **INTRODUCTION**

#### **DEFINITION**

Oscillateur est un terme général pour des circuits électroniques qui produisent par eux-même un signal périodique à une fréquence donnée. Dans un VCO, ou"<u>V</u>oltage-<u>C</u>ontrolled <u>O</u>scillator", celle-ci est variable, commandée par une tension de contrôle.

#### Signaux de sortie

- Sinusoïdaux

- Non-sinusoïdaux

Rectangulaires

Impulsions

Dents de scie

#### **INTRODUCTION**

#### **PARAMETRES CARACTERISTIQUES**

- La linéarité de la relation tension → fréquence

- Le "Gain"  $K_0 = \Delta \omega_{OSC} / \Delta V_0$

- La fréquence limite maximum d'oscillation

- La dynamique de fréquence absolue  $f_{\rm OSC,max}-f_{\rm OSC,min}$  et relative  $f_{\rm OSC,max}/f_{\rm OSC,min}$ , en fonction de  $V_0$

- La forme du signal de sortie, sinusoïdale ou autre

- Taux de distorsion pour les oscillateurs sinusoïdaux

- Bruit de phase

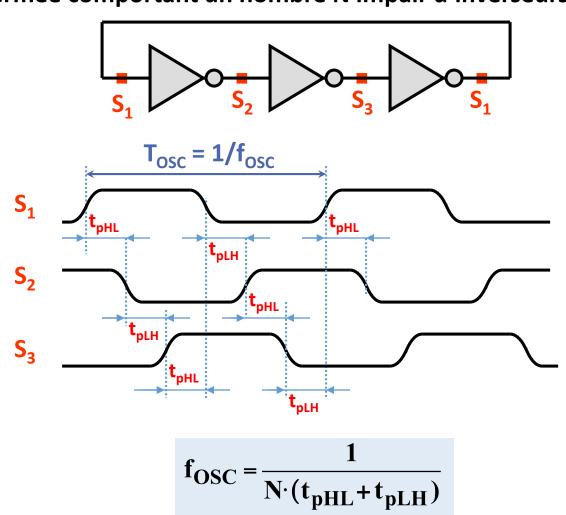

#### 1. VCO A OSCILLATEUR EN ANNEAU CMOS

#### **PRINCIPE**

Chaine fermée comportant un nombre N impair d'inverseurs logiques

#### 1. VCO A OSCILLATEUR EN ANNEAU CMOS

#### **PRINCIPE**

Les temps de propagation  $t_{phl}$  et  $t_{phl}$  sont liés au temps de charge et de décharge, au travers des transistors NMOS ou PMOS, de la capacité de charge totale de la sortie de chaque étage.

$$f_{OSC} = \frac{1}{N \cdot (t_{pHL} + t_{pLH})}$$

Les oscillateurs en anneau sont utilisés comme:

- oscillateurs / VCOs

- circuits de caractérisation de la vitesse d'une technologie (mesure du temps de propagation moyen)

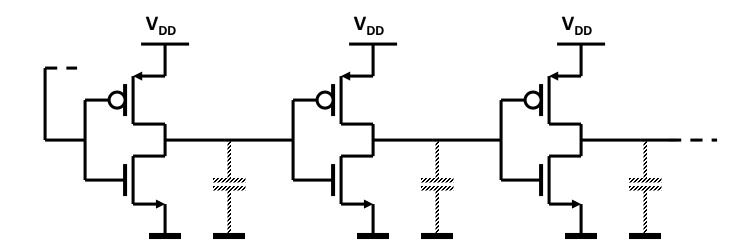

#### **VCO A OSCILLATEUR EN ANNEAU CMOS**

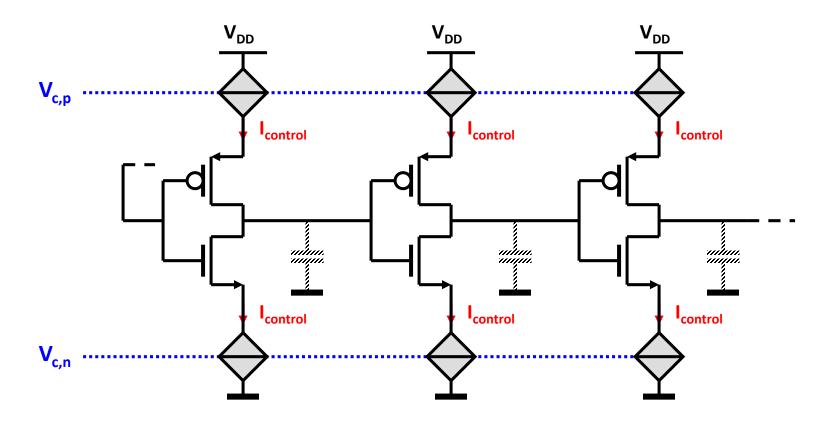

## TRANSFORMATION DE L'OSCILLATEUR EN ANNEAU CMOS EN VCO PAR "CURRENT STARVING"

Les inverseurs CMOS servent de commutateurs pour les sources de courant contrôlées

#### 1. VCO A OSCILLATEUR EN ANNEAU CMOS

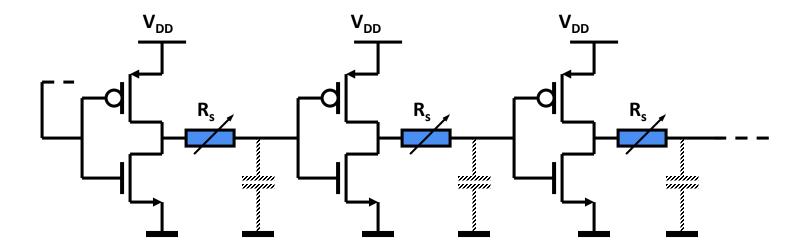

#### TRANSFORMATION DE L'OSCILLATEUR EN ANNEAU CMOS EN VCO PAR RESISTANCE SERIE VARIABLE

Une résistance variable contrôlée est mise en série à la sortie de chaque étage inverseur.

#### 1. VCO A OSCILLATEUR EN ANNEAU CMOS

#### **CARECTERISTIQUES GENERALES**

- Totalement intégrable en technologies CMOS numériques avancées

- Grande souplesse dans le choix de la gamme de fréquence par simple changement du nombre d'étages

- Amplitude de sortie (sur les drains) constante en fonction de la fréquence

- Relation plus ou moins linéaire entre la tension de contrôle et la fréquence

- En pratique, rapport de plus de 2 décades entre f<sub>min</sub> et f<sub>max</sub>

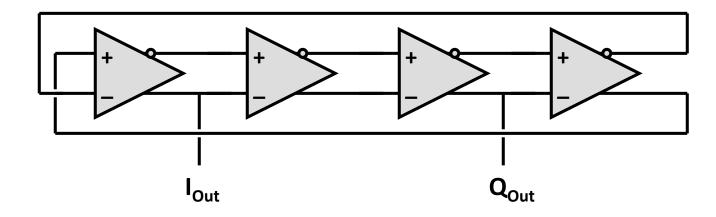

#### 2. VCO A OSCILLATEUR EN ANNEAU A STRUCTURE DIFFERENTIELLE

#### **PRINCIPE**

$$\mathbf{f_{OSC}} = \frac{1}{2 \cdot \mathbf{N} \cdot \mathbf{t_p}}$$

Possibilité d'avoir un nombre N pair de portes logiques, en particulier N = 4, ce qui permet d'avoir des signaux de sortie en quadrature (I - Q).

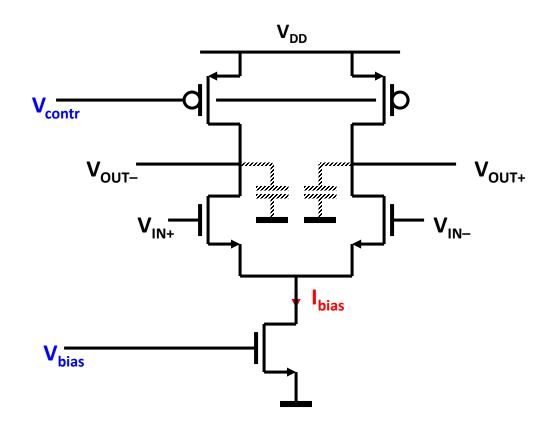

#### 2. VCO A OSCILLATEUR EN ANNEAU A STRUCTURE DIFFERENTIELLE

#### SCHEMA DE PRINCIPE D'UN ETAGE

$$t_{p} = r_{on,p} \cdot C \cdot \ln 2$$

$$t_{p} = \frac{C \cdot \ln 2}{\beta_{p} \cdot (V_{DD} - V_{contr} - V_{Tp})}$$

V<sub>bias</sub> et donc I<sub>bias</sub> sont asservis à V<sub>contr</sub> pour obtenir une amplitude donnée des oscillations.

#### 2. VCO A OSCILLATEUR EN ANNEAU A STRUCTURE DIFFERENTIELLE

#### CARECTERISTIQUES GENERALES

- Totalement intégrable en technologies CMOS numériques avancées

- Nombreuses structures possibles

- Grande souplesse dans le choix de la gamme de fréquence par simple changement du nombre d'étages

- Possibilité d'un nombre paire d'étages, en particulier 4 pour obtenir des signaux de sortie en quadrature

- Bonne immunité aux bruits de mode commun, en particulier ceux d'alimentation et de couplage par le substrat