# Analog IC design (EE-320), Lecture 6

Prof. Mahsa Shoaran

Institute of Electrical and Micro Engineering, School of Engineering, EPFL

#### Homework 1, TP Schedule

- Homework 1 assignment will be posted this week

- EDADK document to be signed and uploaded via moodle, please complete the assignment <u>by Nov 6</u>

- First TP session on Nov 11 in BC07-08 from 3:15pm to 6pm

| Week                          | Subject by week – EE-320: Analog IC design – Fall 2024                    | Suggested Chapters                 |

|-------------------------------|---------------------------------------------------------------------------|------------------------------------|

| Week 1: <b>09/09</b> – 15/09  | Introduction, organization, review of BJT and MOS transistors + Exercise1 | Ch 1, Ch 2.1-2.4, Slides on Moodle |

| Week 2: <b>16/09</b> – 22/09  | Holiday - No class                                                        |                                    |

| Week 3: <b>23/09</b> – 29/09  | MOS large and small-signal models, regimes of operations + Exercise2      | Ch 2.1-2.4                         |

| Week 4: <b>30/09</b> – 06/10  | MOS parasitic effects, layout basic, single-stage amplifiers + Exercise3  | Ch 2.1-2.4, Ch 3.1                 |

| Week 5: <b>07/10</b> – 13/10  | Single-stage amplifiers + Exercise4                                       | Ch 3.1-3.7                         |

| Week 6: <b>14/10</b> – 20/10  | Single-stage amplifiers + Exercise5                                       | Ch 3.1-3.7                         |

| Week 7: <b>21/10</b> – 27/10  | Holiday – No class                                                        |                                    |

| Week 8: <b>28/10</b> – 03/11  | Single-stage amplifiers + Cascode + Exercise6 + Homework1                 | Ch 4.1-4.4                         |

| Week 9: <b>04/11</b> – 10/11  | Differential amplifiers + Exercise7                                       | Ch 4.1-4.4                         |

| Week 10: <b>11/11</b> – 17/11 | TP1 Practical exercise session on Cadence                                 | Tutorial on Moodle                 |

| Week 11: <b>18/11</b> – 24/11 | TP2 Practical exercise session on Cadence                                 | Tutorial on Moodle                 |

| Week 12: <b>25/11</b> – 01/12 | TP3 Practical exercise session on Cadence + Homework2                     | Tutorial on Moodle                 |

| Week 13: <b>02/12</b> – 08/12 | TP4 Practical exercise session on Cadence                                 | Tutorial on Moodle                 |

| Week 14: <b>09/12</b> – 15/12 | Differential amplifiers, current mirrors + Exercise8                      | Ch 4.1-4.4, Ch 5.1-5.3             |

| Week 15: <b>16/12</b> – 22/12 | Current mirrors + Exercise9                                               | Ch 5.1-5.3                         |

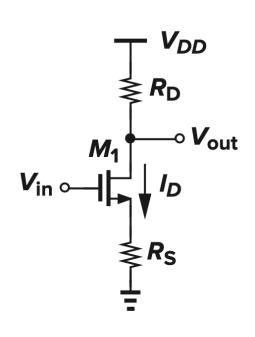

#### Review: Common-Source

#### Review: Common-Source, Source-Follower

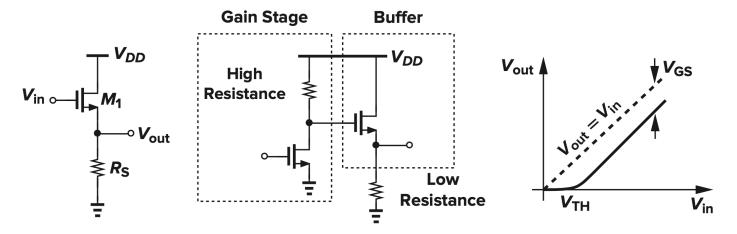

#### Source follower: common-drain or voltage buffer

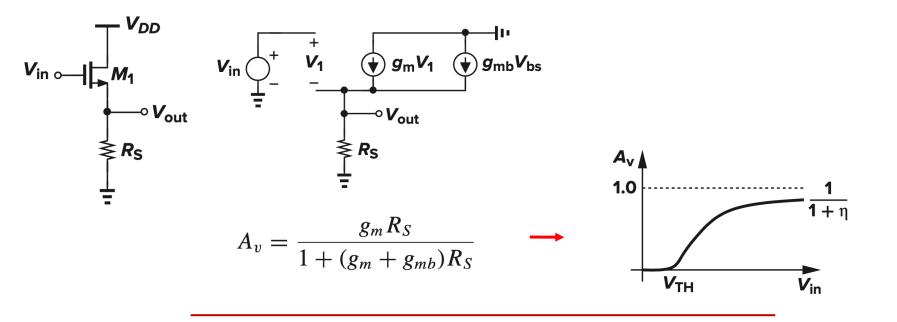

#### Review: Source-Follower

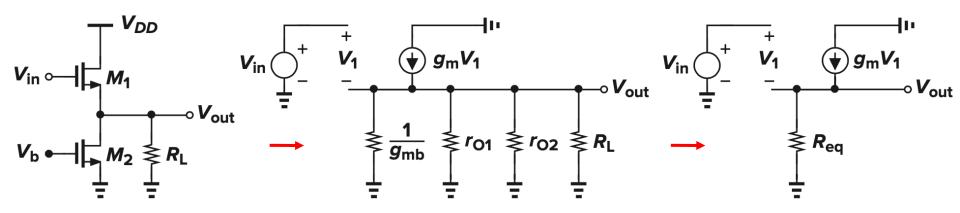

#### Review: Source Follower with a finite load resistance

$$A_v = \frac{R_{eq}}{R_{eq} + \frac{1}{g_m}}$$

$R_{eq} = (1/g_{mb})||r_{O1}||r_{O2}||R_L$

$$R_{eq} = (1/g_{mb})||r_{O1}||r_{O2}||R_L$$

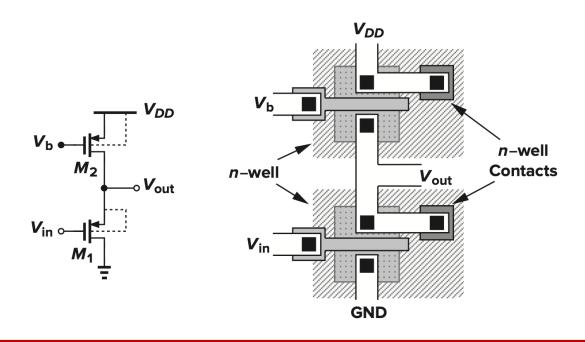

### Example: Calculate the voltage gain

# Example: Calculate the voltage gain

$$A_{v} = \frac{\frac{1}{g_{m2} + g_{mb2}} ||r_{O2}||r_{O1}|| \frac{1}{g_{mb1}}}{\frac{1}{g_{mb2} + g_{mb2}} ||r_{O2}||r_{O1}|| \frac{1}{g_{mb1}} + \frac{1}{g_{m1}}}$$

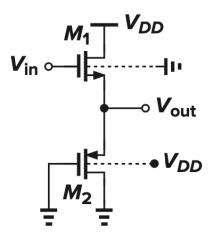

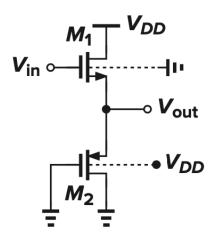

#### PMOS Source Follower with no body effect

- Source follower drawbacks:

- nonlinearity

- voltage headroom limitation

- Even if biased by an ideal current source, some nonlinearity exists due to the **nonlinear** dependence of  $V_{TH}$  upon the **source** potential

MS EE 320

### PMOS Source Follower with no body effect

- Source follower drawbacks:

- nonlinearity

- voltage headroom limitation

- Even if biased by an ideal current source, some nonlinearity exists due to the **nonlinear** dependence of  $V_{TH}$  upon the **source** potential

- The nonlinearity due to body effect can be eliminated if the bulk is tied to source

#### Source Follower: a level shifter

$$V_{GS1} - V_{TH1} \longrightarrow V_{GS2} + (V_{GS3} - V_{TH3})$$

- Source followers shift the dc level by V<sub>GS</sub>, thereby consuming voltage headroom and limiting the swings

- One application of source followers is in performing voltage-level shift

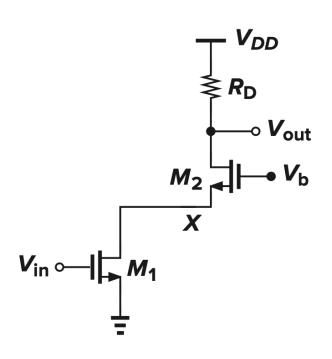

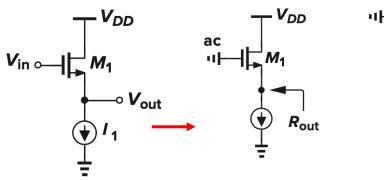

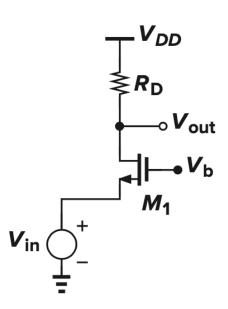

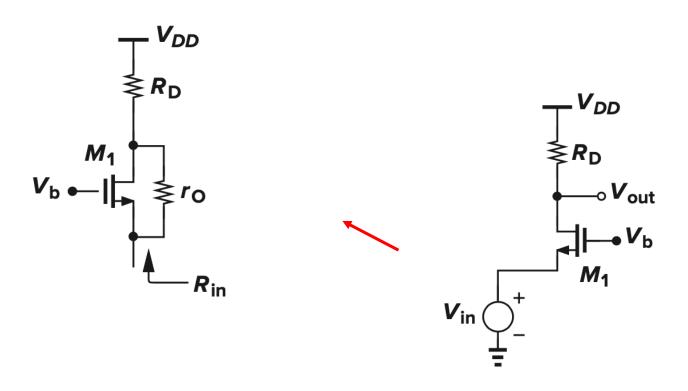

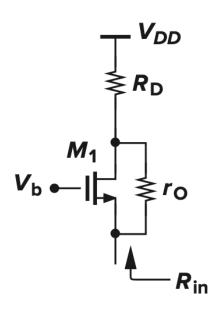

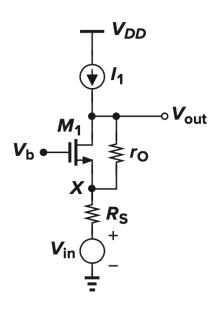

### Common-Gate Stage

A common-gate (CG) stage senses the input at the source and produces the output at the drain

# Common-Gate Stage

A common-gate (CG) stage senses the input at the source and produces the output at the drain

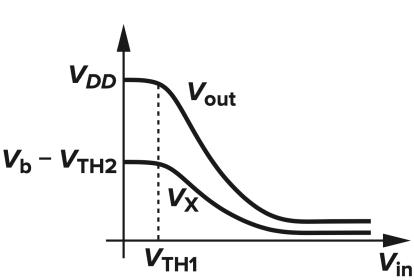

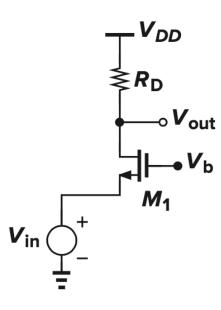

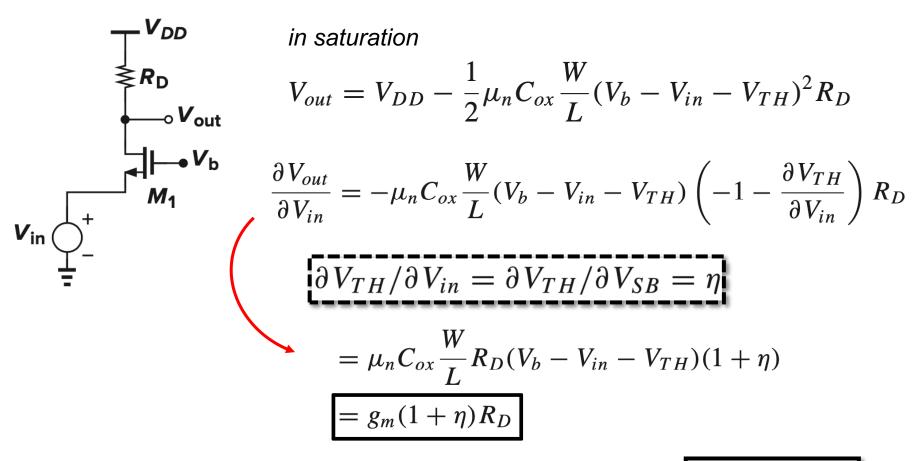

### Common-Gate Stage: large signal analysis

in saturation

$$V_{\text{out}} \qquad I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_b - V_{in} - V_{TH})^2$$

$$V_{out} = V_{DD} - \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_b - V_{in} - V_{TH})^2 R_D$$

driving  $M_1$  into the triode region if:

$$V_{DD} - \frac{1}{2}\mu_n C_{ox} \frac{W}{L} (V_b - V_{in} - V_{TH})^2 R_D = V_b - V_{TH}$$

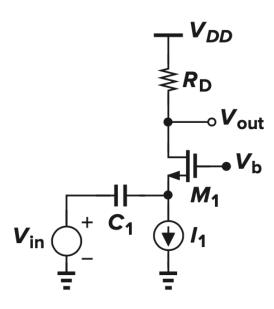

# Common-Gate Stage: large signal analysis

in saturation

$$\frac{\partial V_{b}}{\partial I_{1}} = -\mu_{n} C_{ox} \frac{W}{L} (V_{b} - V_{in} - V_{TH}) \left(-1 - \frac{\partial V_{TH}}{\partial V_{in}}\right) R_{D}$$

$$\partial V_{TH}/\partial V_{in} = \partial V_{TH}/\partial V_{SB} = \eta$$

$$= \mu_n C_{ox} \frac{W}{L} R_D (V_b - V_{in} - V_{TH}) (1 + \eta)$$

$$=g_m(1+\eta)R_D$$

# Common-Gate Stage: large signal analysis

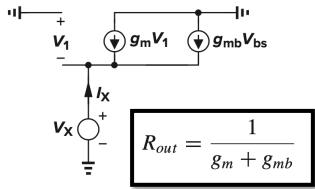

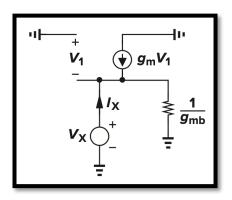

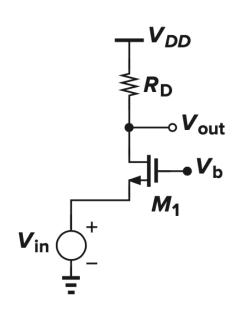

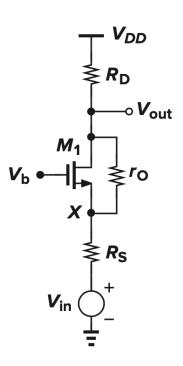

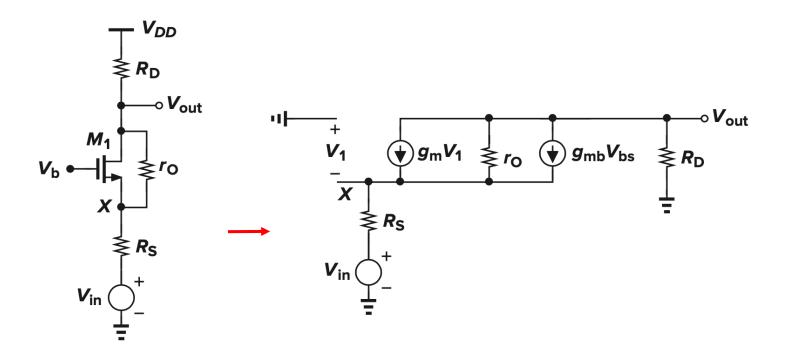

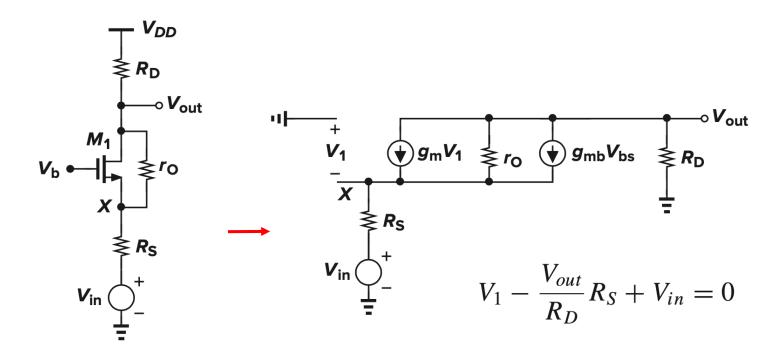

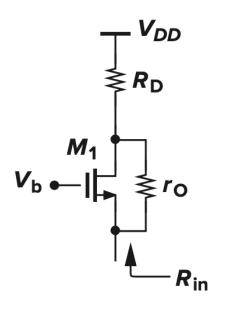

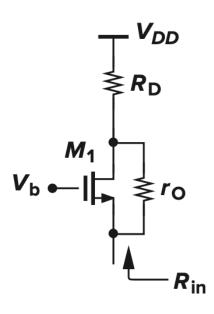

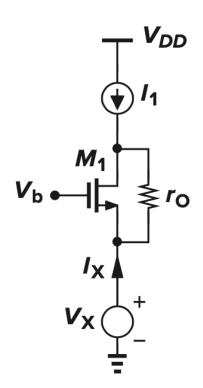

• for  $\underline{\lambda = 0}$ , the **input impedance** (seen at the source of  $M_1$ ):  $1/(g_m + g_{mb})$

$1/[g_m(1+\eta)]$

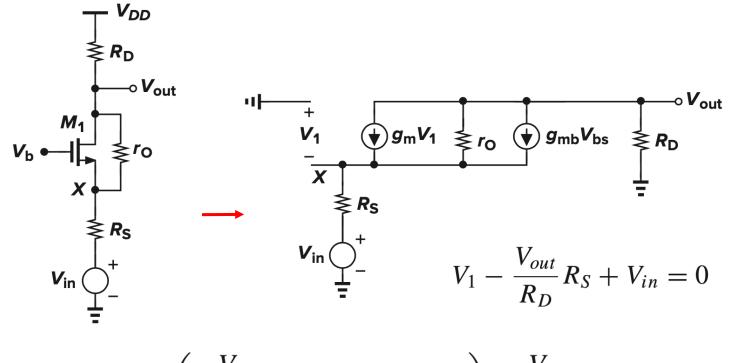

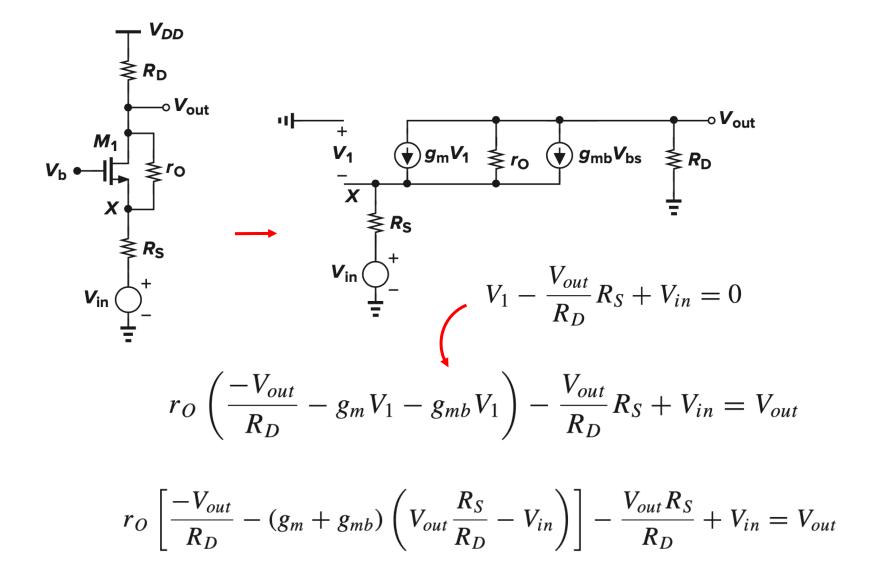

$$r_O\left(\frac{-V_{out}}{R_D} - g_m V_1 - g_{mb} V_1\right) - \frac{V_{out}}{R_D} R_S + V_{in} = V_{out}$$

$$R_D I_X + r_O [I_X - (g_m + g_{mb})V_X] = V_X$$

$$\frac{V_X}{I_X} = \frac{R_D + r_O}{1 + (g_m + g_{mb})r_O}$$

$$\approx \frac{R_D}{(g_m + g_{mb})r_O} + \frac{1}{g_m + g_{mb}}$$

$$\frac{V_X}{I_X} = \frac{R_D + r_O}{1 + (g_m + g_{mb})r_O}$$

$$\approx \frac{R_D}{(g_m + g_{mb})r_O} + \frac{1}{g_m + g_{mb}}$$

✓ the **drain impedance** is **divided** by  $(g_m + g_{mb})r_O$  when seen at the **source**

$$\frac{V_X}{I_X} = \frac{R_D + r_O}{1 + (g_m + g_{mb})r_O}$$

$$\approx \frac{R_D}{(g_m + g_{mb})r_O} + \frac{1}{g_m + g_{mb}}$$

✓ the **drain impedance** is **divided** by  $(g_m + g_{mb})r_O$  when seen at the **source**

$$R_D = 0 \qquad \frac{V_X}{I_X} = \frac{r_O}{1 + (g_m + g_{mb})r_O}$$

$$= \frac{1}{\frac{1}{r_O} + g_m + g_{mb}}$$

$$\frac{V_X}{I_X} = \frac{R_D + r_O}{1 + (g_m + g_{mb})r_O}$$

$$\approx \frac{R_D}{(g_m + g_{mb})r_O} + \frac{1}{g_m + g_{mb}}$$

the input impedance approaches infinity

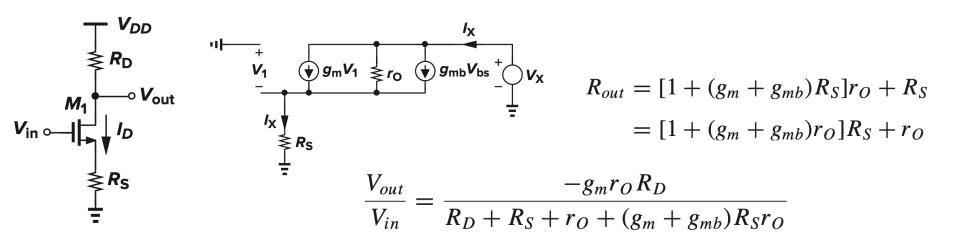

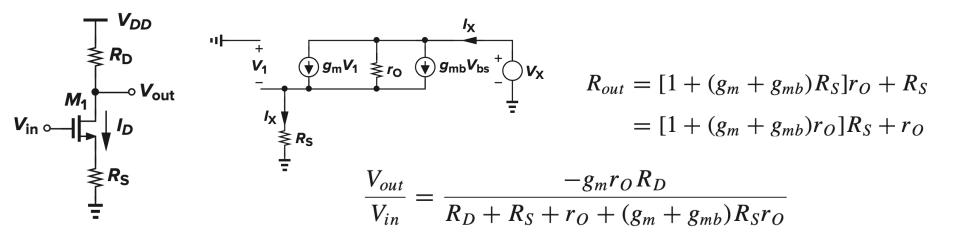

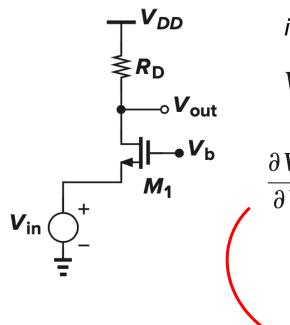

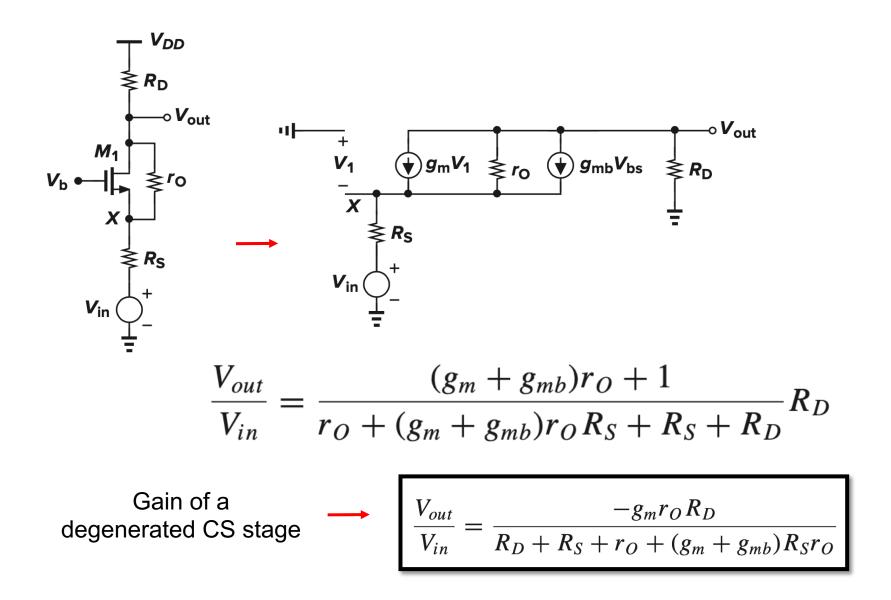

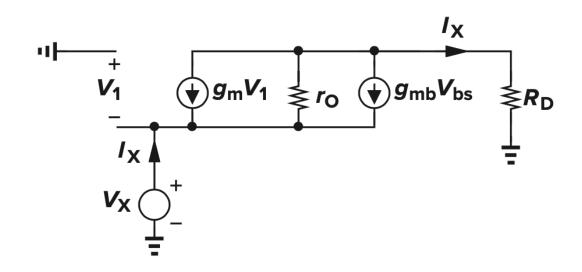

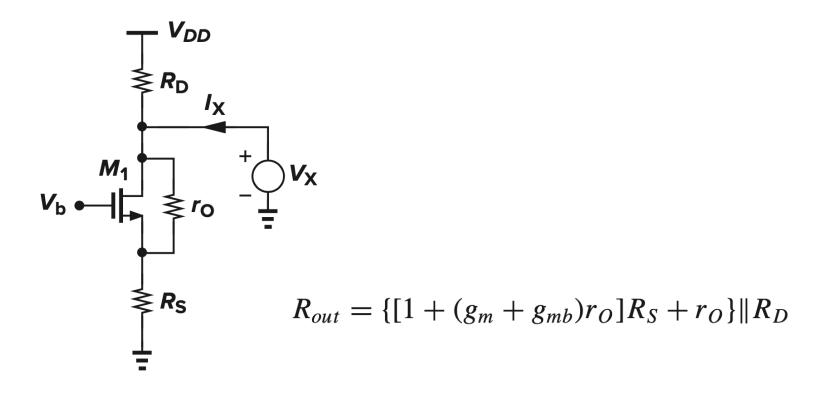

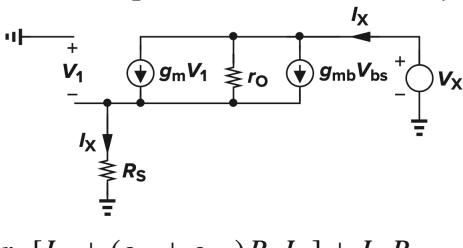

# Recall: Output resistance of a degenerated CS

Source degeneration increases the output resistance

$$r_O[I_X + (g_m + g_{mb})R_SI_X] + I_XR_S = V_X$$

$$R_{out} = [1 + (g_m + g_{mb})R_S]r_O + R_S$$

$$= [1 + (g_m + g_{mb})r_O]R_S + r_O$$

$$\approx (g_m + g_{mb})r_OR_S + r_O$$

$$= [1 + (g_m + g_{mb})R_S]r_O$$

• The overall output resistance is the parallel combination of  $R_{out}$  and  $R_D$

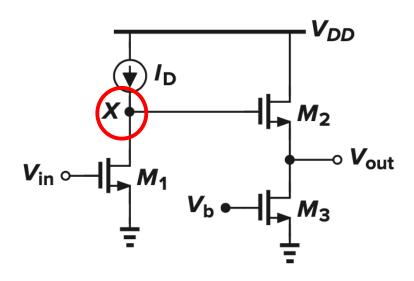

# Example: Calculate the voltage gain

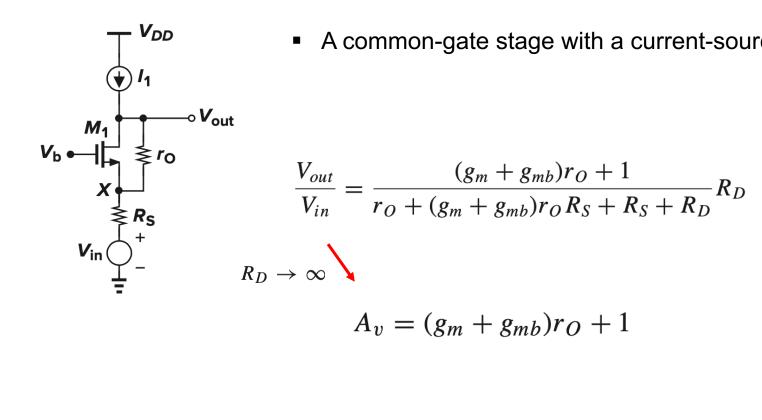

A common-gate stage with a current-source load

# Example: Calculate the voltage gain

A common-gate stage with a current-source load

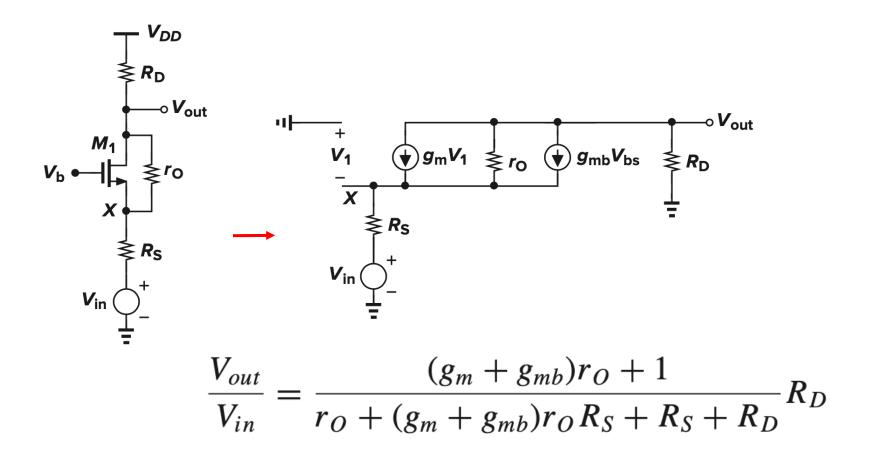

$$\frac{V_{out}}{V_{in}} = \frac{(g_m + g_{mb})r_O + 1}{r_O + (g_m + g_{mb})r_O R_S + R_S + R_D} R_D$$

$$A_v = (g_m + g_{mb})r_O + 1$$

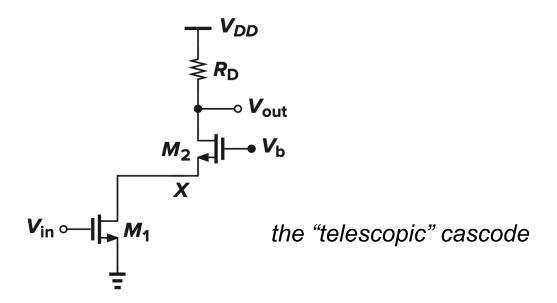

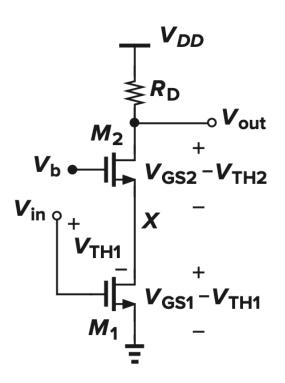

#### Cascode stage

The cascade of a CS stage and a CG stage is called a "cascode" topology, providing many useful properties.

#### Cascode: bias condition

$$V_{b} - V_{GS2} \ge V_{in} - V_{TH1}$$

$V_{out} \ge V_{b} - V_{TH2}$

$\downarrow$

$V_{out} \ge V_{in} - V_{TH1} + V_{GS2} - V_{TH2}$

$= (V_{GS1} - V_{TH1}) + (V_{GS2} - V_{TH2})$

✓ the minimum output level for both transistors to operate in saturation is

equal to the overdrive voltage of M₁ plus that of M₂

# Cascode: large-signal behavior