## Analog IC design (EE-320), Lecture 2

#### Prof. Mahsa Shoaran

Institute of Electrical and Micro Engineering, School of Engineering, EPFL

## Review: CMOS Analog Design

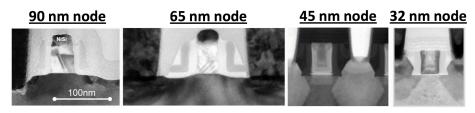

courtesy V. Moroz, IEDM

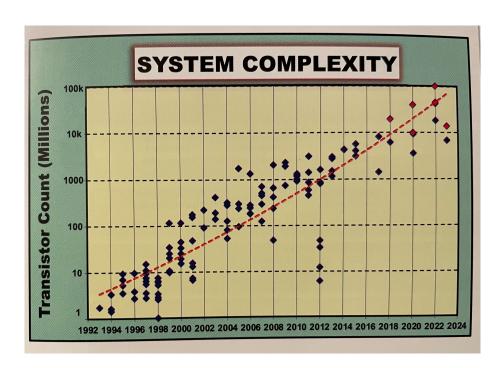

#### Microprocessor Transistor Count, Moore's Law

R. Wu et al., JSSC 2017 U. Shin et al., JSSC 2022

## Review: MOS threshold voltage

$$V_{TH} = \Phi_{MS} + 2\Phi_F + \frac{Q_{dep}}{C_{ox}}$$

$$\Phi_F = (kT/q) \ln(N_{sub}/n_i)$$

$$Q_{dep} = \sqrt{4q\epsilon_{si}|\Phi_F|N_{sub}}$$

$Q_{dep}$ : charge in the depletion region

*N<sub>sub</sub>*: doping density of the substrate

$C_{ox}$ : the gate-oxide capacitance per unit area

$n_i$ : density of electrons in undoped silicon

$\varepsilon_{si}$ : the dielectric constant of silicon

$\Phi_{MS}$ : the difference between the work functions of the poly (gate) and substrate

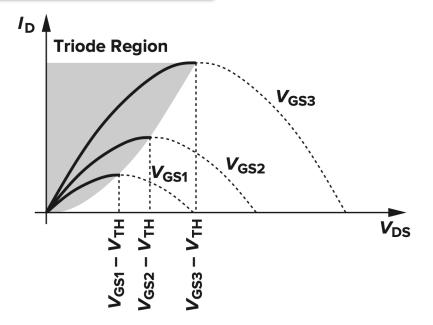

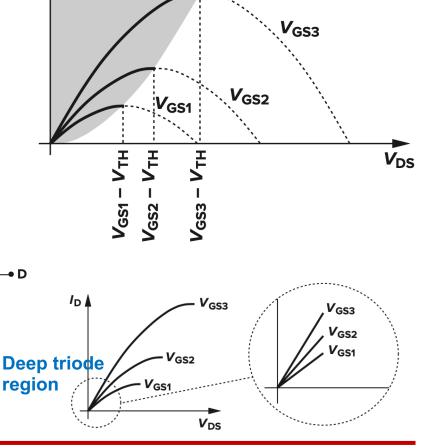

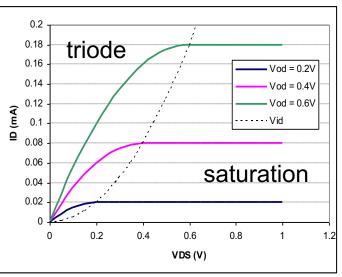

# Review: I<sub>D</sub> vs. V<sub>DS</sub> in the triode region

$$I_D = \mu_n C_{ox} \frac{W}{L} \left[ (V_{GS} - V_{TH}) V_{DS} - \frac{1}{2} V_{DS}^2 \right]$$

- The overdrive voltage:  $V_{GS}-V_{TH}$

- The aspect ratio: W/L

$$V_{DS} \le V_{GS} - V_{TH}$$

$$\downarrow or V_{GD} > V_{TH}$$

"triode" region (or linear region)

MS EE 320

# Review: I<sub>D</sub> vs. V<sub>DS</sub> in the triode region

$$I_D = \mu_n C_{ox} \frac{W}{L} \left[ (V_{GS} - V_{TH}) V_{DS} - \frac{1}{2} V_{DS}^2 \right]$$

$I_{\rm D}$

**Triode Region**

- ullet The overdrive voltage:  $V_{GS}-V_{TH}$

- The aspect ratio: W/L

$$V_{DS} \leq V_{GS} - V_{TH}$$

$$\int or V_{GD} > V_{TH}$$

"triode" region (or linear region)

### Course Schedule & new room for TPs

| Week                          | Subject by week – EE-320: Analog IC design – Fall 2024                    | Suggested Chapters                 |

|-------------------------------|---------------------------------------------------------------------------|------------------------------------|

| Week 1: <b>09/09</b> – 15/09  | Introduction, organization, review of BJT and MOS transistors + Exercise1 | Ch 1, Ch 2.1-2.4, Slides on Moodle |

| Week 2: <b>16/09</b> – 22/09  | Holiday - No class                                                        |                                    |

| Week 3: <b>23/09</b> – 29/09  | MOS large and small-signal models, regimes of operations + Exercise2      | Ch 2.1-2.4                         |

| Week 4: <b>30/09</b> – 06/10  | MOS parasitic effects, layout basic, single-stage amplifiers + Exercise3  | Ch 2.1-2.4, Ch 3.1                 |

| Week 5: <b>07/10</b> – 13/10  | Single-stage amplifiers + Exercise4                                       | Ch 3.1-3.7                         |

| Week 6: <b>14/10</b> – 20/10  | Single-stage amplifiers + Exercise5                                       | Ch 3.1-3.7                         |

| Week 7: <b>21/10</b> – 27/10  | Holiday – No class                                                        |                                    |

| Week 8: <b>28/10</b> – 03/11  | Single-stage amplifiers + Cascode + Exercise6 + Homework1                 | Ch 4.1-4.4                         |

| Week 9: <b>04/11</b> – 10/11  | Differential amplifiers + Exercise7                                       | Ch 4.1-4.4                         |

| Week 10: <b>11/11</b> – 17/11 | TP1 Practical exercise session on Cadence                                 | Tutorial on Moodle                 |

| Week 11: <b>18/11</b> – 24/11 | TP2 Practical exercise session on Cadence                                 | Tutorial on Moodle                 |

| Week 12: <b>25/11</b> – 01/12 | TP3 Practical exercise session on Cadence + Homework2                     | Tutorial on Moodle                 |

| Week 13: <b>02/12</b> – 08/12 | TP4 Practical exercise session on Cadence                                 | Tutorial on Moodle                 |

| Week 14: <b>09/12</b> – 15/12 | Differential amplifiers, current mirrors + Exercise8                      | Ch 4.1-4.4, Ch 5.1-5.3             |

| Week 15: <b>16/12</b> – 22/12 | Current mirrors + Exercise9                                               | Ch 5.1-5.3                         |

#### TPs will be held in BC07-08

#### **Assessment:**

- Written final exam: 70% of the final grade

- Homework (2 in total): 30% of the final grade

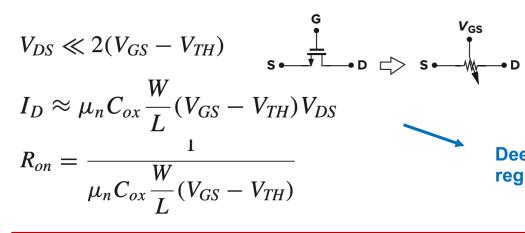

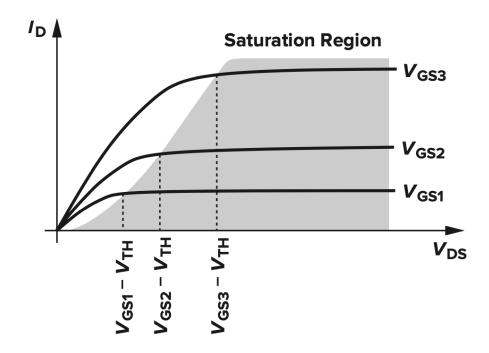

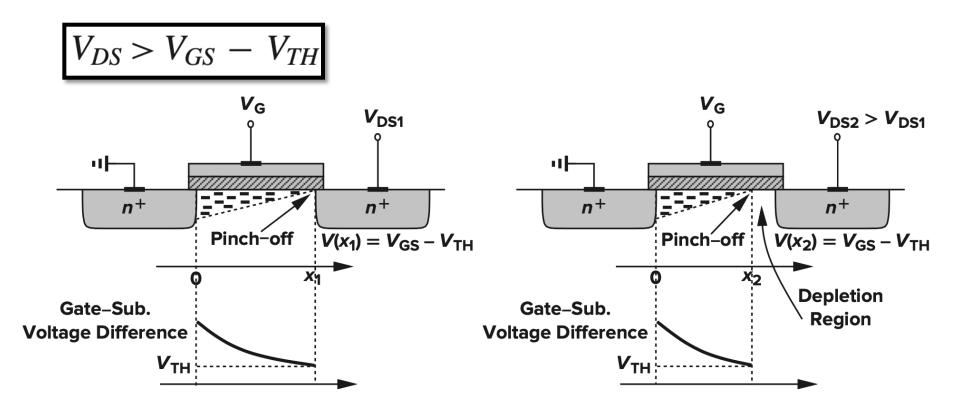

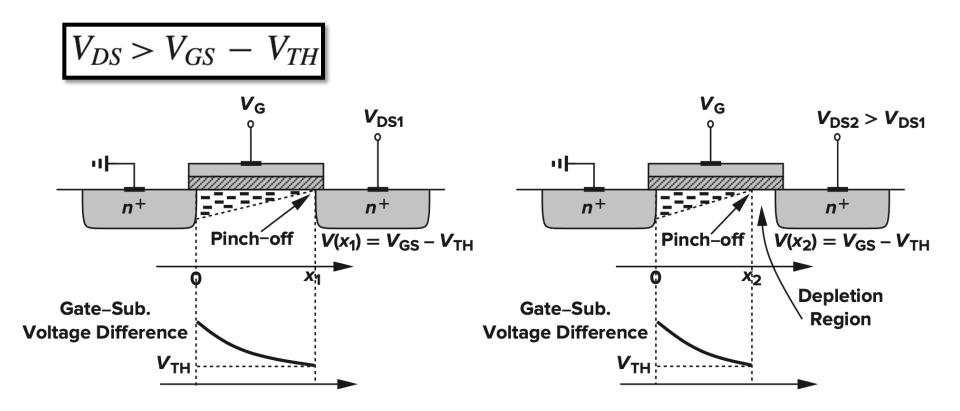

$$V_{DS} > V_{GS} - V_{TH}$$

I<sub>D</sub> becomes relatively constant, and we say that the device operates in the "saturation" region.

### MOS in Saturation: Pinch-off behavior

Recall that the local density of the inversion-layer charge is proportional to:

$$V_{GS} - V(x) - V_{TH}$$

### MOS in Saturation: Pinch-off behavior

Recall that the local density of the inversion-layer charge is proportional to:

$$V_{GS} - V(x) - V_{TH}$$

• if  $V(x) \rightarrow V_{GS} - V_{TH}$ , then  $Q_d(x)$  drops to zero. So, if  $V_{DS}$  is slightly **greater** than  $V_{GS} - V_{TH}$ , the inversion layer stops at  $x \le L$ , the channel is "**pinched off**"

9

#### MOS in Saturation: I/V Characteristics

- As the electrons approach the pinch-off point (where Q<sub>d</sub>→0), their velocity rises tremendously (v = I/Q<sub>d</sub>)

- Upon passing the pinch-off point, the electrons simply shoot through the depletion region and arrive at the drain terminal

- $Q_d$  the density of *mobile* charge: the integral from x = 0 to x = L', where L' is the point at which  $Q_d$  drops to zero (e.g.,  $x_2$ ), and from V(x) = 0 to  $V(x) = V_{GS} V_{TH}$

MS EE 320

#### Recall: derivation of I/V Characteristics

$$I_D = WC_{ox}[V_{GS} - V(x) - V_{TH}]\mu_n \frac{dV(x)}{dx}$$

$$\int_{x=0}^{L} I_D dx = \int_{V=0}^{V_{DS}} WC_{ox} \mu_n [V_{GS} - V(x) - V_{TH}] dV$$

#### MOS in Saturation: I/V Characteristics

- As the electrons approach the pinch-off point (where  $Q_d \rightarrow 0$ ), their velocity rises tremendously ( $v = I/Q_d$ )

- Upon passing the pinch-off point, the electrons simply shoot through the depletion region and arrive at the drain terminal

- $Q_d$  the density of *mobile* charge: the integral from x = 0 to x = L', where L' is the point at which  $Q_d$  drops to zero (e.g.,  $x_2$ ), and from V(x) = 0 to  $V(x) = V_{GS} - V_{TH}$

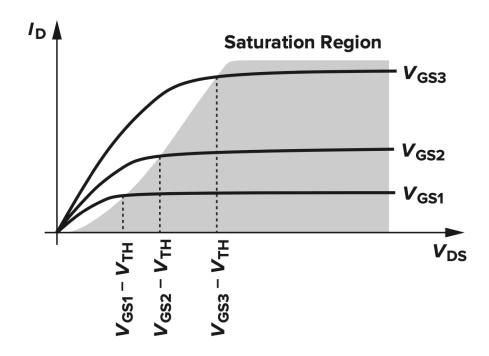

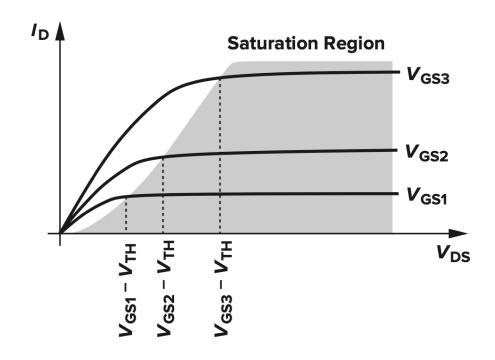

A "square-law" behavior:

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L'} (V_{GS} - V_{TH})^2$$

$$V_{DS} > V_{GS} - V_{TH}$$

or  $V_{GD} < V_{TH}$

$$V_{DS} > V_{GS} - V_{TH}$$

I<sub>D</sub> becomes relatively constant, and we say that the device operates in the "saturation" region.

#### MOS in Saturation: I/V Characteristics

- As the electrons approach the pinch-off point (where  $Q_d \rightarrow 0$ ), their velocity rises tremendously ( $v = I/Q_d$ )

- Upon passing the pinch-off point, the electrons simply shoot through the depletion region and arrive at the drain terminal

- $Q_d$  the density of *mobile* charge: the integral from x = 0 to x = L', where L' is the point at which  $Q_d$  drops to zero (e.g.,  $x_2$ ), and from V(x) = 0 to  $V(x) = V_{GS} - V_{TH}$

$$V_{DS} > V_{GS} - V_{TH}$$

or  $V_{GD} < V_{TH}$

A "square-law" behavior:

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L'} (V_{GS} - V_{TH})^2$$

$$V_{GS} = \sqrt{\frac{2I_D}{\mu_n C_{ox} \frac{W}{L'}}} + V_{TH}$$

$$V_{DS} > V_{GS} - V_{TH}$$

- The drain-source voltage must be **equal to** or **greater** than **overdrive** voltage

- $V_{D,sat} = V_{GS} V_{TH}$ , where  $V_{D,sat}$  denotes the **minimum**  $V_{DS}$  necessary for operation in **saturation**

- the larger the V<sub>D,sat</sub>, the less headroom is available

- The drain-source voltage must be equal to or greater than overdrive voltage

- $V_{D,sat} = V_{GS} V_{TH}$ , where  $V_{D,sat}$  denotes the **minimum**  $V_{DS}$  necessary for operation in **saturation**

- the larger the V<sub>D,sat</sub>, the less headroom is available

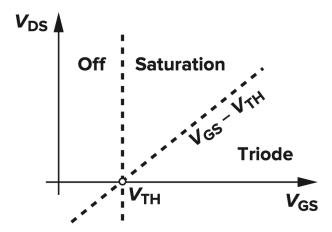

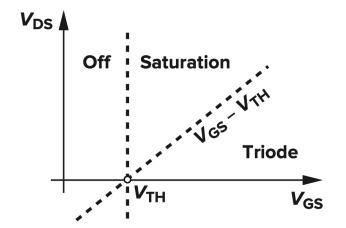

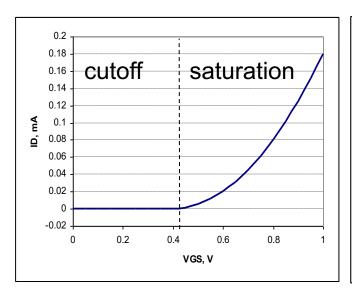

# MOS I/V in different regions

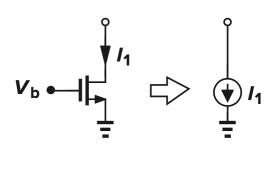

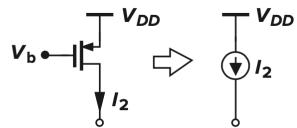

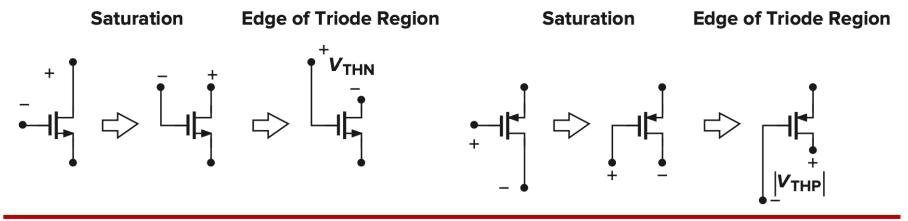

# I<sub>D</sub> for PMOS transistor, regimes of operation

- We assume that  $I_D$  flows from the drain to the source, whereas holes flow in the reverse direction: a negative sign needed

- Note that  $V_{GS}$ ,  $V_{DS}$ ,  $V_{TH}$ , and  $V_{GS} V_{TH}$  are negative for a PMOS that is turned on

- Mobility of holes ~1/2 of electrons → PMOS: lower "current driving" capability

$$I_{D} = -\mu_{p}C_{ox}\frac{W}{L}\left[(V_{GS} - V_{TH})V_{DS} - \frac{1}{2}V_{DS}^{2}\right]$$

$$I_{D} = -\frac{1}{2}\mu_{p}C_{ox}\frac{W}{L'}(V_{GS} - V_{TH})^{2}$$

$$PMOS:$$

saturation:  $V_{GD} > V_{TH}$

triode:  $V_{GD} < V_{TH}$

$$V_{TH}$$

is negative

# In for PMOS transistor, regimes of operation

- We assume that  $I_D$  flows from the drain to the source, whereas holes flow in the reverse direction: a negative sign needed

- Note that  $V_{GS}$ ,  $V_{DS}$ ,  $V_{TH}$ , and  $V_{GS} V_{TH}$  are **negative** for a PMOS that is **turned on**

- Mobility of holes ~1/2 of electrons → PMOS: lower "current driving" capability

$$I_{D} = -\mu_{p}C_{ox}\frac{W}{L}\left[(V_{GS} - V_{TH})V_{DS} - \frac{1}{2}V_{DS}^{2}\right] \qquad \begin{array}{l} \textit{PMOS:} \\ \textit{saturation: $V_{GD} > V_{TH}$} \\ I_{D} = -\frac{1}{2}\mu_{p}C_{ox}\frac{W}{L'}(V_{GS} - V_{TH})^{2} & \textit{triode: $V_{GD} < V_{TH}$} \\ V_{TH} \textit{ is negative} \end{array}$$

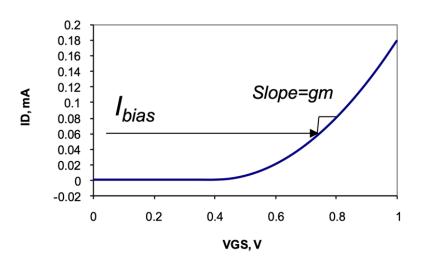

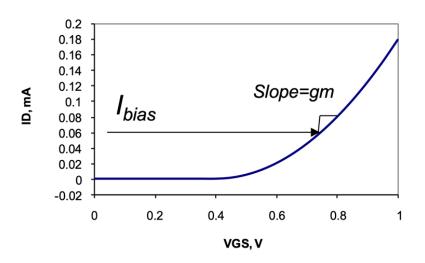

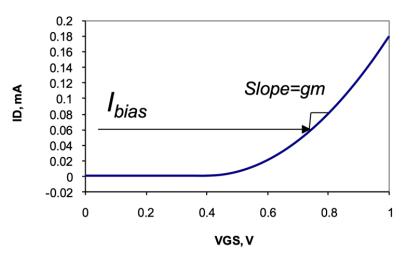

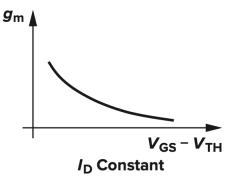

## MOS transconductance (g<sub>m</sub>) in saturation

$$g_m = \frac{\partial I_D}{\partial V_{GS}} \Big|_{VDS \text{ const.}}$$

$$= \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})$$

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L'} (V_{GS} - V_{TH})^2$$

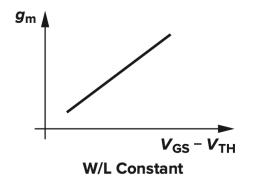

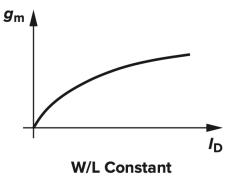

## MOS transconductance (g<sub>m</sub>) in saturation

$$g_m = \frac{\partial I_D}{\partial V_{GS}} \Big|_{VDS \text{ const.}}$$

$$= \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})$$

or

$$g_m = \sqrt{2\mu_n C_{ox} \frac{W}{L} I_D}$$

$$= \frac{2I_D}{V_{GS} - V_{TH}}$$

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L'} (V_{GS} - V_{TH})^2$$

## MOS transconductance (g<sub>m</sub>) in saturation

$$g_m = \frac{\partial I_D}{\partial V_{GS}} \Big|_{VDS \text{ const.}}$$

$$= \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})$$

or

$$g_m = \sqrt{2\mu_n C_{ox} \frac{W}{L} I_D}$$

$$= \frac{2I_D}{V_{GS} - V_{TH}}$$

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L'} (V_{GS} - V_{TH})^2$$

# Example: MOS transconductance (g<sub>m</sub>) in triode?

ightharpoonup Plot  $g_m$  as a function of  $V_{DS}$ ?

# Example: MOS transconductance (g<sub>m</sub>) in triode?

❖ Plot g<sub>m</sub> as a function of V<sub>DS</sub>?

$$g_{m} = \frac{\partial}{\partial V_{GS}} \left\{ \frac{1}{2} \mu_{n} C_{ox} \frac{W}{L} \left[ 2(V_{GS} - V_{TH}) V_{DS} - V_{DS}^{2} \right] \right\}$$

$$= \mu_{n} C_{ox} \frac{W}{L} V_{DS}$$

# Example: MOS transconductance (g<sub>m</sub>) in triode?

❖ Plot g<sub>m</sub> as a function of V<sub>DS</sub>?

$$g_{m} = \frac{\partial}{\partial V_{GS}} \left\{ \frac{1}{2} \mu_{n} C_{ox} \frac{W}{L} \left[ 2(V_{GS} - V_{TH}) V_{DS} - V_{DS}^{2} \right] \right\}$$

$$= \mu_{n} C_{ox} \frac{W}{L} V_{DS}$$

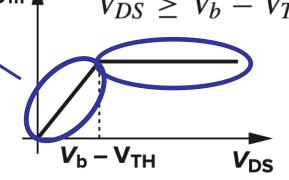

triode

- $g_m = \mu_n C_{ox} \frac{W}{I} (V_{GS} V_{TH})$

- g<sub>m</sub> drops in the triode region

- so we usually employ MOS in saturation for amplifying the signal

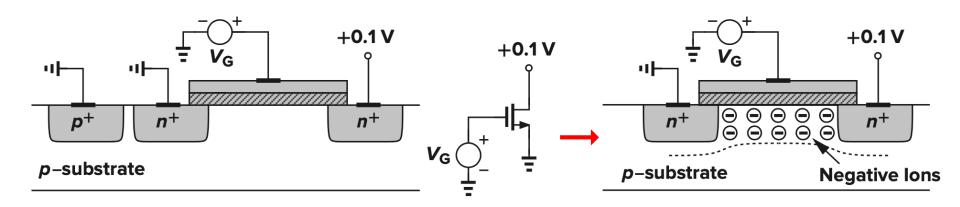

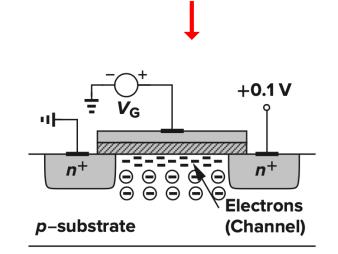

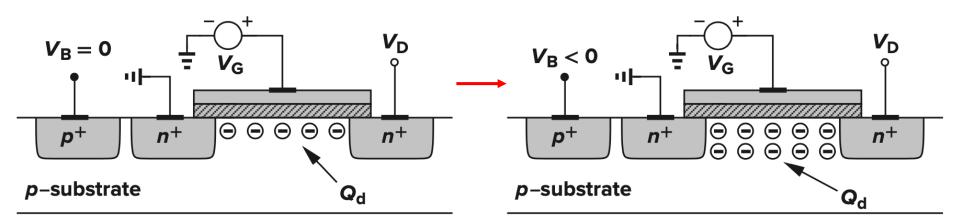

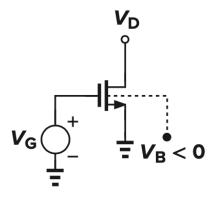

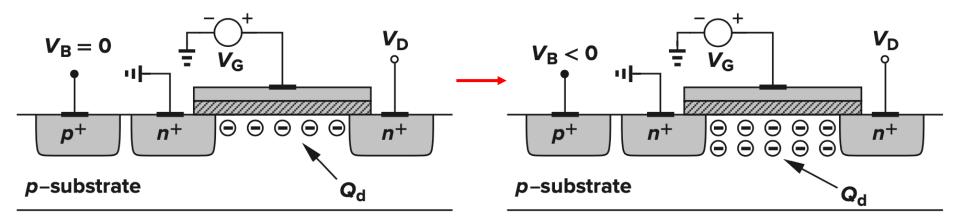

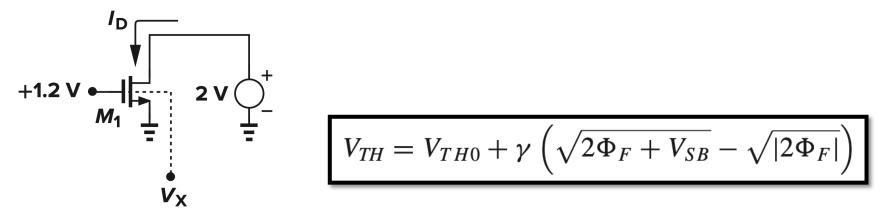

# Second-order effects: 1) Body Effect

# Second-order effects: 1) Body Effect

As V<sub>B</sub> becomes more negative, threshold voltage increases:

$$V_{TH} = V_{TH0} + \gamma \left( \sqrt{2\Phi_F + V_{SB}} - \sqrt{|2\Phi_F|} \right)$$

$$\gamma = \sqrt{2q\epsilon_{si}N_{sub}}/C_{ox}$$

V<sub>SB</sub> is the source-bulk potential difference

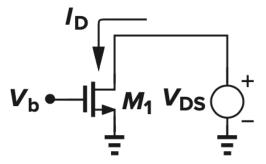

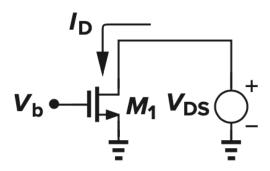

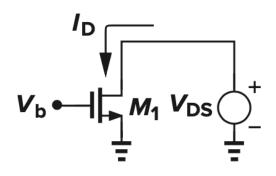

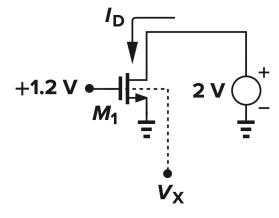

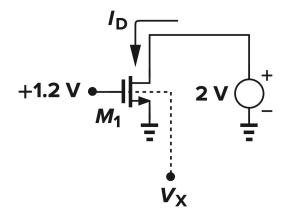

# Example: Body Effect

❖ Plot the drain current if  $V_X$  varies from −∞ to 0. Assume  $V_{TH0}$  = 0.3V,  $\gamma$  = 0.4V<sup>1/2</sup>, and 2 $\Phi_F$  = 0.7V.

# Example: Body Effect

❖ Plot the drain current if  $V_X$  varies from  $-\infty$  to 0. Assume  $V_{TH0} = 0.3$ V,  $\gamma = 0.4$ V<sup>1/2</sup>, and  $2\Phi_F = 0.7V$ .

$$V_{TH} = V_{TH0} + \gamma \left( \sqrt{2\Phi_F + V_{SB}} - \sqrt{|2\Phi_F|} \right)$$

1.2 V = 0.3 + 0.4

$$\left(\sqrt{0.7 - V_{X1}} - \sqrt{0.7}\right)$$

$\longrightarrow$   $V_{X1} = -8.83 \text{ V}$

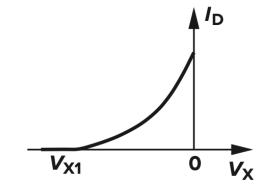

# Example: Body Effect

❖ Plot the drain current if  $V_X$  varies from -∞ to 0. Assume  $V_{TH0}$  = 0.3V, γ = 0.4V<sup>1/2</sup>, and  $2Φ_F$  = 0.7V.

$$1.2 \text{ V} = 0.3 + 0.4 \left( \sqrt{0.7 - V_{X1}} - \sqrt{0.7} \right)$$

for  $V_{X1} < V_X < 0$

$$I_D = \frac{1}{2}\mu_n C_{ox} \frac{W}{L} \left[ V_{GS} - V_{TH0} - \gamma \left( \sqrt{2\Phi_F - V_X} - \sqrt{2\Phi_F} \right) \right]^2$$

EE 320 31

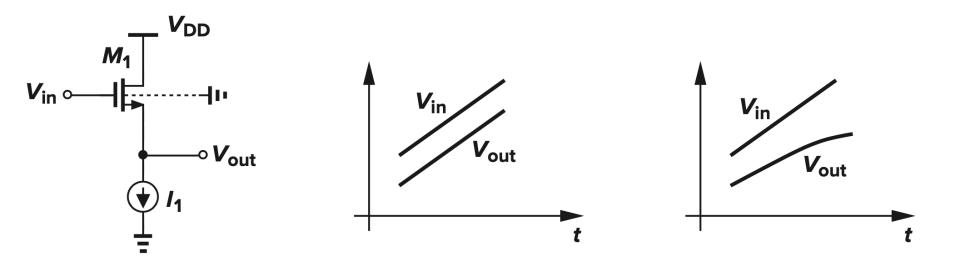

## **Body Effect**

$$I_1 = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{in} - V_{out} - V_{TH})^2$$

$$V_{TH} = V_{TH0} + \gamma \left( \sqrt{2\Phi_F + V_{SB}} - \sqrt{|2\Phi_F|} \right)$$

if V<sub>SB</sub> becomes negative, V<sub>TH</sub> decreases

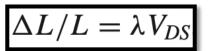

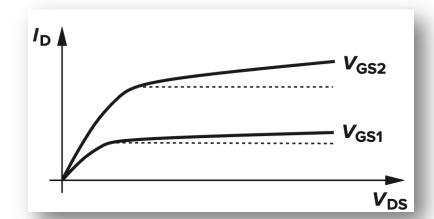

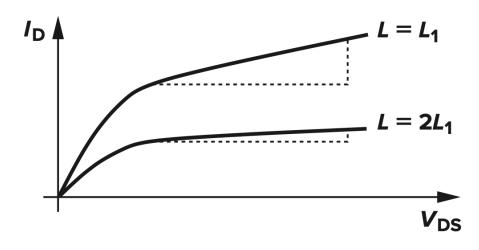

# Second-order effects: 2) Channel-Length Modulation

The actual length of the channel gradually decreases as the potential difference between the gate and the drain decreases >> L' is a function of V<sub>DS</sub>

$$L' = L - \Delta L$$

$$1/L' \approx (1 + \Delta L/L)/L$$

$$\Delta L/L = \lambda V_{DS}$$

# Second-order effects: 2) Channel-Length Modulation

The actual length of the channel gradually decreases as the potential difference between the gate and the drain decreases >> L' is a function of V<sub>DS</sub>

$$L' = L - \Delta L$$

$1/L' \approx (1 + \Delta L/L)/L$

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L'} (V_{GS} - V_{TH})^2$$

$$I_D \approx \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 (1 + \lambda V_{DS})$$

$$g_m = \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH}) (1 + \lambda V_{DS})$$

$$= \sqrt{2\mu_n C_{ox} (W/L) I_D (1 + \lambda V_{DS})}$$

# Channel-Length Modulation

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 (1 + \lambda V_{DS})$$

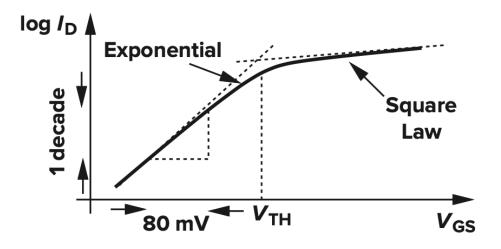

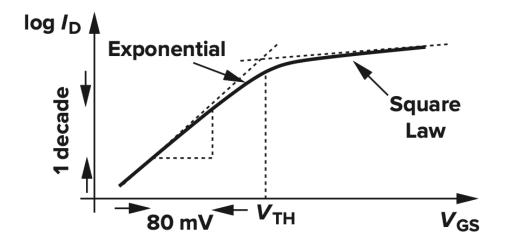

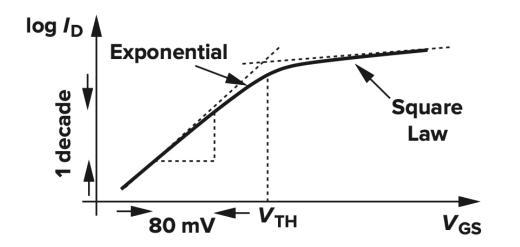

## Second-order effects: 3) Subthreshold Conduction

■ In reality, for  $V_{GS} \approx V_{TH}$ , a "weak" inversion layer exists and some current flows from D to S. Even for  $V_{GS} < V_{TH}$ ,  $I_D$  exhibits an exponential dependence on  $V_{GS}$

MS EE 320 36

## Second-order effects: 3) Subthreshold Conduction

- In reality, for  $V_{GS} \approx V_{TH}$ , a "weak" inversion layer exists and some current flows from D to S. Even for  $V_{GS} < V_{TH}$ ,  $I_D$  exhibits an exponential dependence on  $V_{GS}$

- This "subthreshold conduction" can be formulated for roughly V<sub>DS</sub> > 100 mV as:

$$I_D = I_0 \exp \frac{V_{GS}}{\xi V_T}$$

where  $I_0$  is proportional to W/L,  $\xi > 1$  is a nonideality factor, and  $V_T = kT/q$

- The device operates in "weak inversion" (for V<sub>GS</sub>>V<sub>TH</sub> in strong inversion)

- Except for ξ, similar to the exponential I<sub>C</sub>/V<sub>BE</sub> of a BJT

## **Subthreshold Conduction**

■ Observation: V<sub>GS</sub> must decrease by ~80 mV for I<sub>D</sub> to decrease by one decade

### **Subthreshold Conduction**

Observation: V<sub>GS</sub> must decrease by ~80 mV for I<sub>D</sub> to decrease by one decade

$$I_D = I_0 \exp \frac{V_{GS}}{\xi V_T} \longrightarrow g_m = I_D/(\xi V_T)$$

#### **Subthreshold Conduction**

Observation: V<sub>GS</sub> must decrease by ~80 mV for I<sub>D</sub> to decrease by one decade

$$\frac{I_D}{\xi V_T} = \frac{2I_D}{(V_{GS} - V_{TH})_1}$$

transition point?

$$(V_{GS} - V_{TH})_1 = 2\xi V_T$$

$$I_D = I_0 \exp \frac{V_{GS}}{\xi V_T} \longrightarrow g_m = I_D/(\xi V_T)$$

Subthreshold operation only with a large device width or low drain current:

the speed of subthreshold circuits severely limited

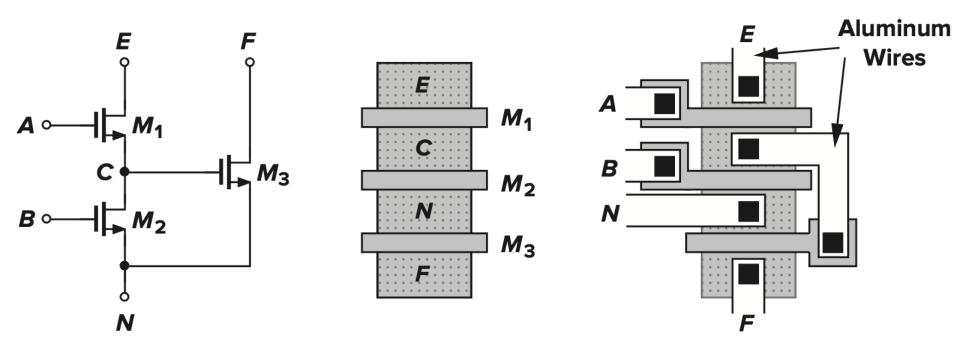

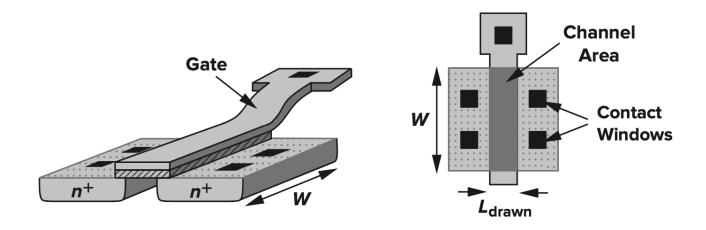

## MOS Device Layout

- The gate polysilicon and the source and drain terminals must be tied to metal (aluminum) wires as interconnects with low resistance and capacitance

- One or more "contact windows" opened in each region, filled with metal, and connected to the upper metal wires

- To minimize the capacitance of S and D, the area of each junction minimized

## MOS Device Layout

- The gate polysilicon and the source and drain terminals must be tied to metal (aluminum) wires as interconnects with low resistance and capacitance

- One or more "contact windows" opened in each region, filled with metal, and connected to the upper metal wires

- To minimize the capacitance of S and D, the area of each junction minimized

## **MOS Device Layout**

- The layout determined by both the electrical properties of the device and the "design rules" imposed by the technology

- W/L is chosen to set the transconductance or other circuit parameters while the minimum L is dictated by the process

- In addition to the gate, the source and drain areas must be defined properly