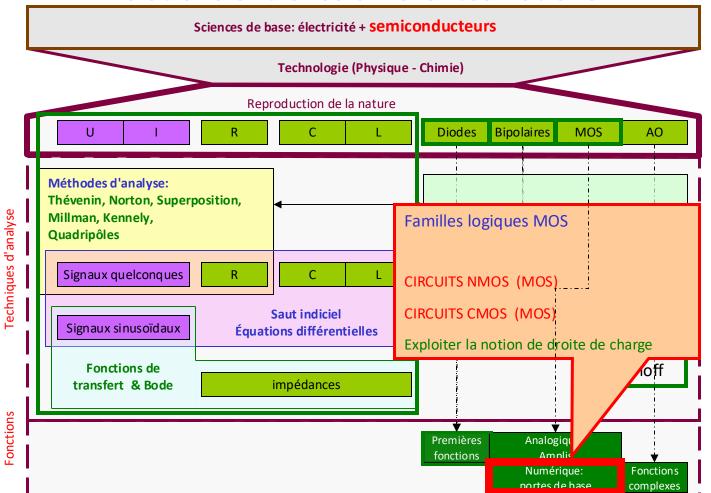

#### Relations entre les différentes notions

#### Puissance dissipée

Caractéristique essentielle en C.I., spécialement en VLSI.

Limite le nombre maximum de portes réalisables sur une puce.

La puissance maximum admissible par chip dépend du type de boîtier.

• De l'ordre de 500 mW à 1 watt.

La puissance dissipée dans un circuit logique a

- une composante statique et

- une composante dynamique.

Puissance statique = puissance dissipée au repos.

• le circuit est alimenté, mais ne change pas d'état.

Puissance dynamique = puissance dissipée pour changer d'état.

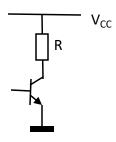

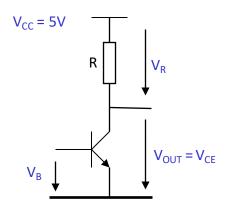

## Exemple de calcul de puissance statique

ne dissipe aucune puissance dans l'état de sortie 1 (transistor bloqué),

- Dissipe une puissance  $P_{\text{stat}} = V_{\text{cc}} I_{\text{sat}} = V_{\text{cc}}^2 / R$  avec sortie 0.

- En moyenne: moitié des sorties à l'état 1, et moitié à l'état 0

- \* la puissance statique moyenne vaut:

$$P_{stat} = \frac{V_{CC}^2}{2R}$$

L'inverseur à transistor bipolaire:

#### Cas de l'inverseur CMOS:

ne dissipe pratiquement aucune puissance au repos, car un des deux transistors est toujours bloqué.

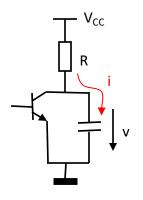

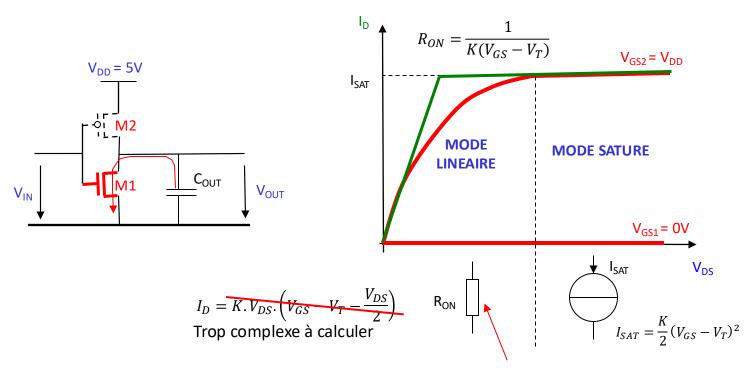

### Exemple de calcul de puissance dynamique

Lié à la charge ou à la décharge d'une capacité parasite connectée à la sortie de la porte.

La charge s'effectue à travers la résistance de charge R (le transistor est en mode bloqué)

Puissance dynamique dissipée pour une commutation de 0 à 1:

Puissance dynamique dissipée pour une commutation de 0 à 1:

$$E = \int_0^\infty (V_{CC} - V) \cdot i dt = \int_0^\infty (V_{CC} - V) \cdot C \cdot \frac{dV}{dt} dt = \int_{V(0)}^{V(\infty)} (V_{CC} - V) \cdot C \cdot dV$$

Avec  $V(\infty) = V_{CC}$  et  $V(0) = 0$  on a  $P = \frac{C \cdot V_{CC}^2}{2}$

Avec

$$V(\infty) = V_{CC}$$

et  $V(0) = 0$  on a  $P = \frac{C.V_{CC}^2}{2}$

Transition inverse: Puissance équivalente dissipée dans transistor.

La puissance dynamique dépend de la fréquence f de commutation

$$P_{Dyn} = f.C.V_{CC}^2$$

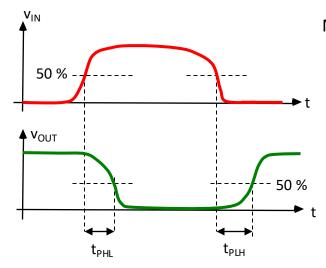

### Délai de propagation par porte

Retard entre transition des signaux de sortie et d'entrée.

Ce retard est lié à divers phénomènes dynamiques, tels que:

- la charge et/ou la décharge de diverses capacités parasites,

- l'évacuation des minoritaires stockés dans la base d'un transistor (bip.) saturé,

Méthode courante pour le délai de propagation:

- Mesurer le délai entre les points à "50%" des signaux d'entrée et de sortie.

- Délais de propagation différents pour montée et descente,

Temps de propagation = moyenne entre ces deux temps

$$t_{PD} = \frac{1}{2}(t_{PHL} + t_{PLH})$$

#### La logique NMOS

Technologie adaptée à la réalisation de circuits logiques VLSI:

- 1- Structure très simple (techno simplifiée conception simplifiée)

- ex: Pas d'isolation nécessaire entre transistors voisins (diodes en inverse)

- conséquence: économiquement moins cher

- 2- Surface de silicium réduite. conséquence:

- Plus économique que le bipolaire

- Plus de puissance de calcul pour surface identique

- mais présence d'une résistance gourmande en surface

- 3- Impédance d'entrée quasi infinie (voir cours sur les A.O.)

- Utilisation de N-MOS plutôt que des P-MOS car:

$\mu_n > \mu_p \,$  --> logique N-MOS plus rapide que P-MOS

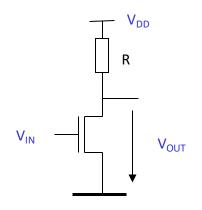

Inverseur à charge résistive

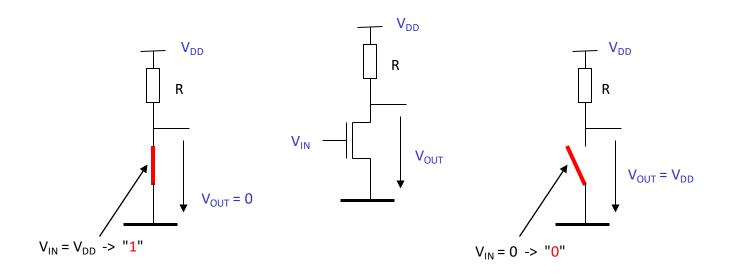

## Comportement idéal = interrupteur

Avec une charge reliée à V<sub>CC</sub>, on réalise une logique de type NOT

## Comportement idéal = interrupteur

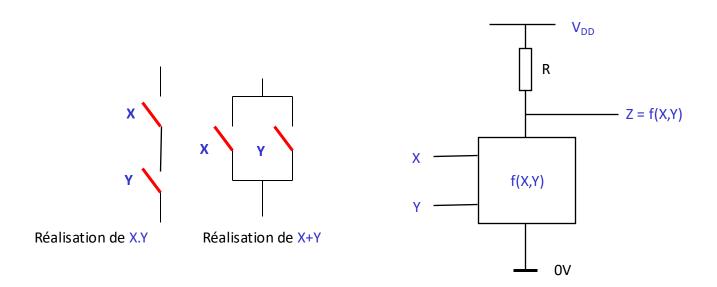

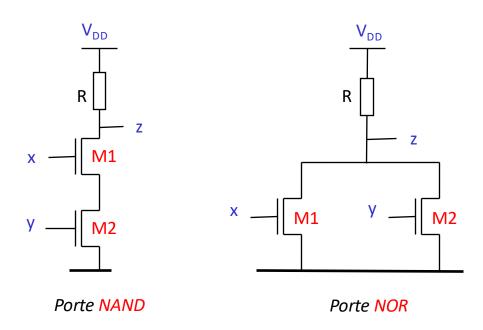

Réalisation de fonctions avec des interrupteurs

La nature des fonctions dépend de la structure série ou parallèle des composants

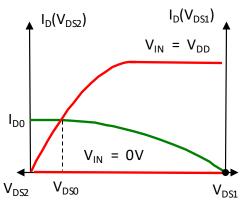

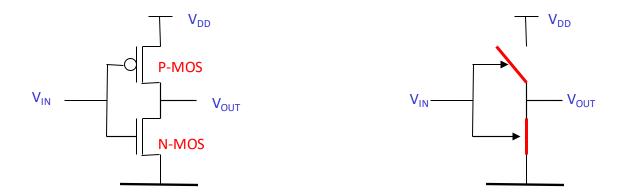

## Circuits logiques N-MOS:

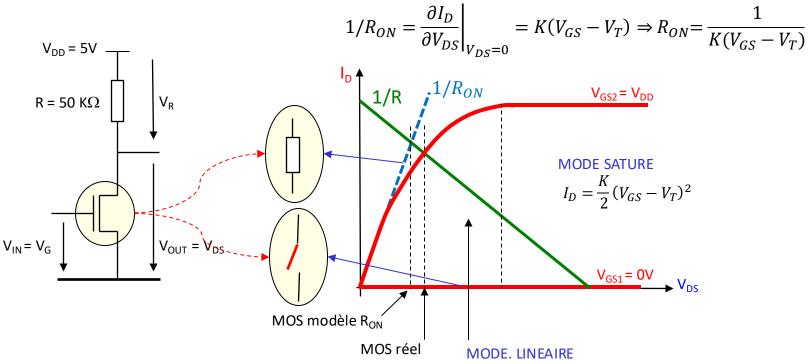

#### Dimensionnement de l'inverseur

Niveau bas

$$V_{OUT} = V_{DD} \cdot \frac{R_{ON}}{R_{ON} + R}$$

Détérioration du niveau logique "0"

$$I_D = K.V_{DS}.\left(V_{GS} - V_T - \frac{V_{DS}}{2}\right)$$

Exemple: pour  $V_{DD} = 5V$  on veut  $V_{OUT} = 0.1 V$

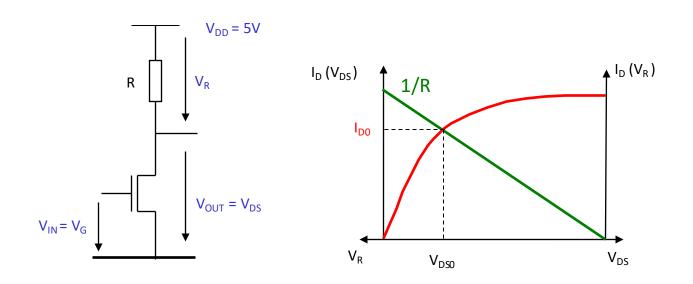

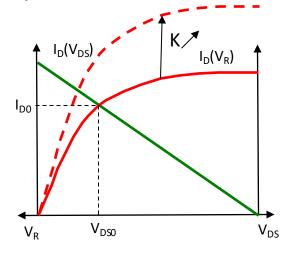

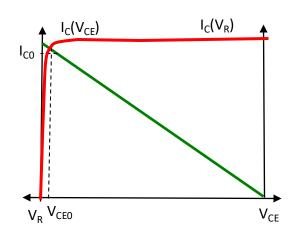

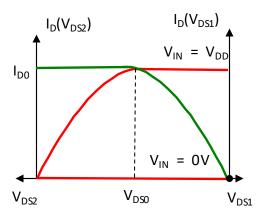

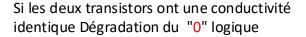

# Vision graphique: Exploitation de la droite de charge

Inconvénient majeur : Détérioration du niveau logique "0"

#### Comparaison avec le Bipolaire

#### Solution:

Redimensionner le transistor MOS

Inconvénient majeur : intégrer la résistance

#### Rappel:

Le MOS entre source et drain comparable à une Résistance (dépendante de V<sub>G</sub>)

## Améliorations possibles

Si M1 a une meilleure conductivité Dégradation du "0" logique minimisée

### Améliorations possibles

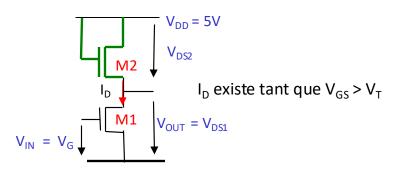

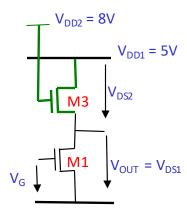

Dégradation du "1" logique

$$V_{OUT} \le V_{DD} - V_{T}$$

Deux alimentations

Transistor **déplété** avec  $V_T < 0$

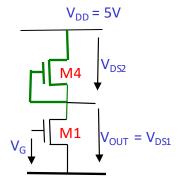

## Principe de l'inverseur CMOS

Remplace quasi toutes les autres technologies. Caractéristiques proches de la famille logique idéale :

- Excellent comportement pour des charges capacitives

- Consommation quasi nulle au repos (tant dans l'état 0 que dans l'état 1 de la sortie)

- Une seule tension d'alimentation V<sub>DD</sub>

- Niveaux logiques = Niveaux de l'alimentation (0 & V<sub>DD</sub>)

- La sortie change d'état pour V<sub>in</sub> ~ V<sub>DD</sub>/2

- Grande marge de bruit

- Vitesse élevée

# Comportement de l'inverseur CMOS

Décharge via M1:

- M1 = une source de courant dans le mode saturé

- M1 = une résistance dans le mode linéaire

Idem pour la charge via M2

Avec R<sub>ON</sub>, le résultat n'est qu'approximatif (ordre de grandeur correct)

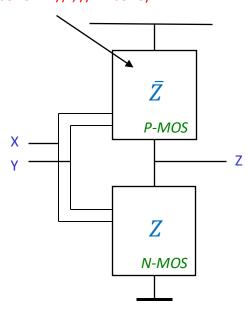

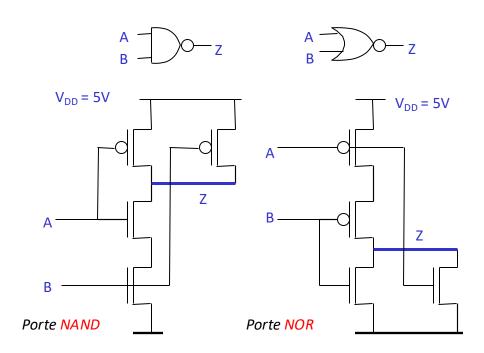

### Réalisation d'une porte logique en CMOS

## Simplement le dual du bloc N-MOS (série --> // ; //--> série)

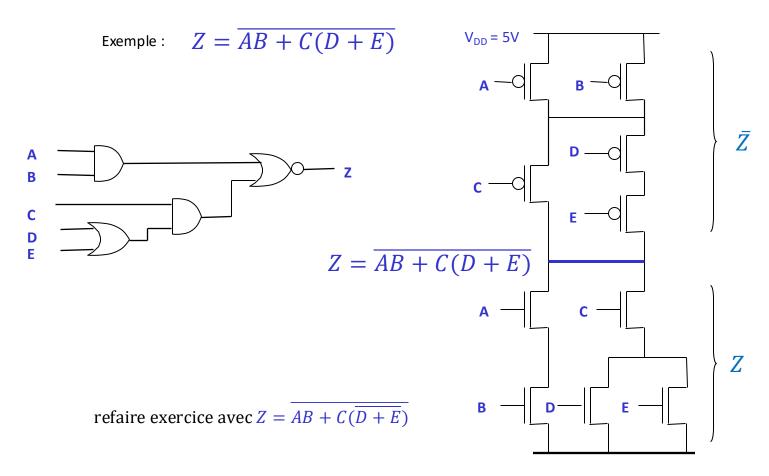

#### Portes complexes en CMOS